Fターム[5K047JJ01]の内容

デジタル伝送方式における同期 (12,489) | その他の同期 (295) | 非連続信号の同期 (129)

Fターム[5K047JJ01]の下位に属するFターム

Fターム[5K047JJ01]に分類される特許

1 - 20 / 30

通信装置及びクロック同期式通信システム

基地局装置、及び同期信号取得方法

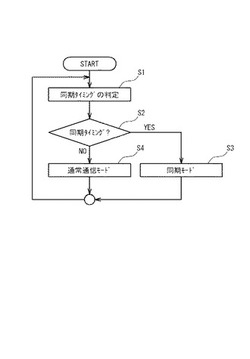

【課題】移動端末との通信中に生じる同期ずれを修正する。

【解決手段】基地局装置は、端末装置との間で通信を行う通信モードを周期的に休止する手段と、前記通信モードの周期的な休止中に、他の基地局装置からの送信信号を受信して同期信号を取得するための同期モードを実行する手段と、を備えている。前記同期モードでは、前記同期信号に基づいて、前記通信モード中に生じた同期ずれを修正する。

(もっと読む)

PONシステムの宅側装置、信号処理回路及び同期維持方法

【課題】 光トランシーバのスリープ時間の経過後に即座に通信を開始できる信号処理回路を提供する。

【解決手段】 本発明の信号処理回路は、光トランシーバ21から入力された受信信号からクロックと受信データを再生し、再生された受信データを上位層側に出力する受信側処理部33,34と、上位層側から入力された送信データを再生されたクロックと同期する送信信号として光トランシーバ21に出力する送信側処理部31,32とを備える。また、本発明の信号処理回路は、光トランシーバ21の機能を低下させるスリープ動作を行う場合に、既に再生されたクロックをスリープ時間中において保持し、かつ、スリープ時間の終了とともにクロックの保持を解除する同期維持モードを実行する制御部27を備える。

(もっと読む)

通信装置及びクロック制御方法

【課題】データ送信部に送信データが保留されている間の消費電力を低減することができる通信装置及びクロック制御方法を提供すること

【解決手段】本発明にかかる通信装置は、供給されたクロックにより駆動し、対向装置に対してデータの送信を行う送信処理部34と、送信処理部34に対してクロックを供給する送信クロック制御部20と、対向装置に対するデータ送信の停止を指示するポーズフレームを受信する受信処理部31と、を備え、受信処理部31がポーズフレームを受信した場合、送信処理部34は、対向装置に対するデータ送信を停止し、送信クロック制御部20は、ポーズフレームにおいて指定される送信停止期間中の送信処理部34に対するクロック供給を停止するものである。

(もっと読む)

送信装置、受信装置及び伝送システム

【課題】パケット間隔が不定で、伝送遅延変動が発生する伝送環境においても、クロックリカバリを確実に実現する。

【解決手段】送信装置1のMU生成部13は、発振器10からのカウンタ値に基づいてDTS及びCTSを生成し、AUにDTS及びCTSを付加すると共に、システムタイム生成部11からのUTC時刻を参照時刻に設定して付加し、MUを生成する。IP/UDPパケット化部15は、MUが分割されたATSパケットをIPパケットに格納し、放送ネットワーク/通信回線3を介して受信装置2へ送信する。受信装置2は、受信したIPパケットに含まれるDTS及び参照時刻、発振器26からのカウンタ値並びにシステムタイム生成部23からのUTC時刻に基づいて、発振器26のカウンタ値を補正する。これにより、受信装置2の発振器26におけるクロックを送信装置1の発振器10におけるクロックに同期させることができる。

(もっと読む)

シリアル通信用ボーレート検出装置およびシリアル通信用ボーレート補正装置ならびにシリアル通信用ボーレート検出方法

【課題】ボーレートを誤差の許容範囲内に維持可能にすると共に、時間の計測に用いるクロックパルスの周波数を低くする。

【解決手段】周期が一定のクロックパルスを発生するクロックジェネレータ33と、通信ライン13上に現れた通信信号の所定区間のタイミングを検出するエッジ検出回路41と、前記所定区間の長さを計数して計数結果を2進数の時間計測値として出力する時間計測タイマ43と、前記時間計測値の2進数を前記所定区間のビット構成に応じて上位ビット部と下位ビット部とに区分し、前記下位ビット部の中の最上位ビットの値を前記上位ビット部の中の最下位ビットの値に加算する加算器46とを備えて(−1<計算誤差≦0)の範囲を(−0.5<計算誤差≦+0.5)に修正する。

(もっと読む)

ステップ遅延事前補償を伴う適応クロック回復

【課題】ステップ遅延事前補償を伴う適応クロック回復を提供する。

【解決手段】ACR(適応クロック回復)サブシステムが、ジッタのあるパケット着信時間を示す入力位相信号を処理して、比較的安定した、回復されたクロック信号を生成するのに使用され得る、比較的平滑で、範囲が限られた出力位相信号を生成する。また、入力位相信号は、例えば、パケットのネットワーク・ルーティングのパス変更に対応する、ステップ遅延を検出し、測定するようにも処理される。入力位相信号が、検出された各ステップ遅延の符号および大きさに基づいて、ACRサブシステムの上流で位相調整されるステップ遅延事前補償が、実行される。その結果、ACRサブシステムは、そのようなステップ遅延の存在に実質的に気付かない。

(もっと読む)

シリアル通信システム及びシリアル通信方法

【課題】MDライン及びSDラインの両方を同時にデータ送信に使用することができるシリアル通信システムを提供する。

【解決手段】本発明のシリアル通信システム1は、第1のデバイス2と第2のデバイス3とを有し、第1のデバイス2と第2のデバイス3とは、第2のデバイス3が生成したシリアルクロックに基づいて、相互通信を開始するシリアル通信システムである。第1のデバイス2から第2のデバイス3への出力が、前フェーズにおいて受信したデータの最終ビット値と反転していると、第2のデバイス3は第1のデバイス2の通信準備状態が完了状態であると判断し、相互通信を開始する。

(もっと読む)

データ伝達方法およびシステム

【課題】互いのクロックサイクルが一致しなくても、特別のFIFOを使用することなく、送信側モジュールから受信側モジュールに正しくデータを伝達できるようにする。

【解決手段】送信側モジュール100は、送信側モジュール100の内部状態を示す表示信号Csと受信側モジュール200の内部状態を示す表示信号Cdに応じて内部クロックCLK_Sに同期して、f関数に基づき表示信号Csを変化させるとともに、表示信号Cs,Cdが一致するときにFIFO101のデータを出力する。受信側モジュール200は、表示信号Cs,Cdに応じて内部クロックCLK_Dに同期して、同じf関数に基づき表示信号Cdを変化させるとともに、表示信号Cs,Cdが一致するときにFIFO201がデータを取り込む。

(もっと読む)

伝送制御装置および伝送制御方法

【課題】スタートビットが受信できない場合に装置間の同期を回復して通信を行うための伝送制御装置および伝送制御方法を提供すること。

【解決手段】伝送制御装置60は、先頭にスタートビットを含むデータを送出する送出部621と、送出部621が送出したデータのスタートビットを受信したか否かを判断する判断部622と、判断部622によりスタートビットが受信されなかったと判断された場合は、所定の同期回復期間T2、送出部621によるデータの送出を禁止する同期回復動作を行う回復動作部623と、を備えて構成されている。

(もっと読む)

非同期型における送受信装置間の同期方法及び送受信装置

【課題】送信装置側と受信装置側にそれぞれ発振回路を有している非同期型の送受信装置の場合でも、送信装置側からのデータパルス信号に対して受信装置側のクロックパルスの位相が進んだり、遅れたりした場合でも、誤動作せずにデータパルス信号を正確に受信できるようにすること。

【解決手段】データパルス信号列の各パルスの周期と発振器27の周期とを同一にすると共に、データパルス信号列の各パルスと発振器27から出力されるクロックパルスのデューティ比をそれぞれ50%に設定する。クロックパルスCjと反転クロックパルス BarCjとで常時入力信号パルスの受信を監視し、クロックパルスCjあるいは BarCjのどちらで入力信号パルスを受信したかにより、Dフリップフロップ25での信号の取り込みのための同期信号としてのクロックパルスCjまたは BarCjを使い分ける。

(もっと読む)

映像信号処理装置および映像信号処理方法

【課題】クロックリカバリの安定度を向上させることが可能な映像信号処理装置を提供すること。

【解決手段】受信バッファ1は、受信したTSパケットを蓄積する。GAP復元部2は、受信バッファ手段に蓄積されたTSパケットの転送時における時間間隔を復元する。制御部3は、TSパケットに含まれるPCR値と、PCR間に含まれるTSパケットの個数とから、受信バッファ1に蓄積されたTSパケット転送の時間間隔を算出してGAP復元部2におけるTSパケットの転送を制御する。したがって、TSパケットの転送速度をほぼ一定とすることができ、クロックリカバリの安定度を向上させることが可能となる。

(もっと読む)

通信システム

【課題】容易に同期外れの発生を防止することができ、周波数偏差の大きい発振素子を用いた低コストな装置構成とすることができる通信システムを提供すること。

【解決手段】通信システム1は、複数ビットからなるデジタル情報に対して、所定ビット数毎に、交互に値が異なる複数ビットからなる区切りデータを挿入するビット挿入部100と、区切りデータが挿入されたデジタル情報を、デジタル信号に変換して送信する送信部101と、送信部101によって送信されたデジタル信号を受信してデジタル情報に変換する受信部110と、受信部110によって変換されたデジタル情報に含まれている区切りデータを認識し、認識結果に基づいてデジタル情報から区切りデータを削除するビット削除部111と、を備える。

(もっと読む)

クロックのデューティ比を活用した高速度シリアル通信

【課題】 シリアルデータの送受信を向上させる。

【解決手段】 シリアルデータの送受信の際に、送信したいデータが、例えば“00…”又は“11…”のように0又は1が複数ビット連続しているような構造である場合、連続しているビット数に応じて送信側100が出力する同期クロック121のデューティ比を変更する。その際の送信側からの出力データ120は、送信したいデータが“00…”ならば0、“11…”ならば1とする。受信側130は受信データが0か1かを認識し、更に同期クロックのデューティ比に応じて、受信データ0又は1が何ビット連続している構造かを判断し、そのビット数分だけデータをデータ受信シフトレジスタ133に格納する。これにより、同期クロック121の1周期の間に複数ビットのデータ120の送受信が可能となる。

(もっと読む)

基地局を同期させる方法および装置

【課題】独立の同期ソースを用いて、またはある基地局(30n)をマスタソースとして特定して、基地局(30n)を同期させる方法および装置を提供する。

【解決手段】RNC(C−RNC)(36,38,40)または基地局(30n)が、1つの基地局(30n)またはUE(20,22,24)に対して、同期を達成するために基地局(30n)から導出される測定値を獲得するように指定することができる。同期活動は、定期的に行われてもよく、または、ドリフト値が所定しきい値を超えていることを定期的測定値が示している時に行われてもよい。

(もっと読む)

非同期シリアル通信方法及び非同期シリアル通信装置

【課題】ある程度の高速性を得ながら、信号線数が少なく、回路規模を小さくする事の出来る非同期シリアル通信方法及び非同期シリアル通信装置を提供する。

【解決手段】送信側において、信号レベルを所定のレベルへ変化させた後、所定の第1時間T1の経過後から別に定めた第2時間T2以内に1ビットの送出データを送出するステップと、受信側において、信号レベルの変化を検出してから更に別に定めた第3時間T3(但し、T3>T1+T2)の経過後、または該第3時間T3の経過時点の何れかに、前記1ビットの送出データを取り込むステップとを含む。

(もっと読む)

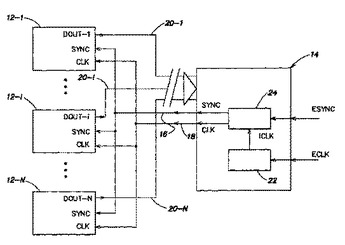

シリアルディジタルデータ通信インターフェイス

伝播遅延が数クロックサイクル長までおよび、ゆっくりと変動する可能性のある、データ送信機12からデータ受信機14へのデータ伝送のシリアルプロトコルおよびインターフェイス。データ受信機は、データ送信機にクロックを供給する。受信機または送信機のいずれかによって供給される同期信号は、クロックによって制御される転送レートで、データ伝送のフレームを始動させる。同期信号は、フレーム長として知られている、データヘッダーとそれに続く所定の数のデータビットの送信を調整する。データ受信機は、ヘッダービットを使用して、後続のデータビットをサンプリングする時間を決定する。フレームの長さは、ビット誤りを発生させるほど大きく伝播遅延ライン特性が変化しないことの十分な見込みを得るように限定される。システムは、各フレームの始点において、再同期する。  (もっと読む)

(もっと読む)

データ/ストローブエンコーディング方式回路およびデータ/ストローブエンコーディング方法

【課題】LSIのデバイス特性に依存せず、設計容易で低コストのデータ/ストローブエンコーディング方式を実現することができるデータ/ストローブエンコーディング方式回路およびデータ/ストローブエンコーディング方法を提供する。

【解決手段】データとストローブ信号を別々な線路で伝送し、データ自身の変化とストローブ信号の変化とをラッチのクロックに用い、データを別クロックで動作している後段回路に伝送するデータ/ストローブエンコーディング方式回路において、所定のデータをフリップフロップでラッチ後、データをラッチし保持していることを示す信号と、ラッチ後のデータと、を対として後段回路に渡し、後段回路から、データを受け取ったことを示す信号のアサートを受け取り、データをラッチして停止しているフリップフロップを再度動作させて新たなデータを受け取る。

(もっと読む)

車両用通信制御ユニットおよび車両用通信制御システム

【課題】バス型車載LANにおいて各ECUが送信する周期的メッセージの衝突を回避する送信タイミングを設定する車両用通信制御ユニットおよび該車両用通信制御ユニットを備える車両用通信制御システムを提供する。

【解決手段】複数のECU同士を車載LAN網を介して相互に送受信可能に接続しているバス型車載LANに接続され、前記複数の各ECUから送信される周期的メッセージの送信時間を受信し、該受信結果を集計して各ECUから送信されるメッセージが他のECUから送信されるメッセージの送信開始時点から送信終了時点までの時間と重ならないように送信タイミングを調整して設定・管理する送信タイミング集計・設定・管理部を備え、該設定した送信タイミングを各ECUに送信して各ECUから設定した送信タイミングでメッセージを送信させる構成としている。

(もっと読む)

シリアル通信装置

【課題】カウントパルスの周波数を上げることなく、誤った符号判定を抑制し得るシリアル通信装置を提供する。

【解決手段】カウントパルス発生部21によりシンクフィールドSFを構成するビット列の1ビット区間よりも十分に短いパルス幅のカウントパルスCpを発生させ、シンクフィールドSFのスタートビットからストップビットまでの間で発生したカウントパルスCpの数をビット長カウント部23によりカウントする。そして、ビット長決定部30よって、ビット長カウント部23によりカウントされたカウントパルスCpの数をビット列のビット数2nで除した商Qおよびその余りSに基づいて1ビット区間の1ビット長を決定し、ビット長決定部30により決定された1ビット長に従った所定タイミングで同期クロック生成部27により同期クロックSynCLK を生成する。

(もっと読む)

1 - 20 / 30

[ Back to top ]