Fターム[5K069DB11]の内容

交換用スイッチ回路、多重交換制御方式 (1,187) | スイッチ、通話路 (238) | 時間スイッチ (21)

Fターム[5K069DB11]の下位に属するFターム

通話路メモリ

制御メモリ (1)

入力バッファメモリ (1)

出力バッファメモリメモリ (1)

メモリに対するアクセス手段、方法 (2)

タイムスロット入れ替え方式 (4)

並列処理(交換)するもの (2)

Fターム[5K069DB11]に分類される特許

1 - 10 / 10

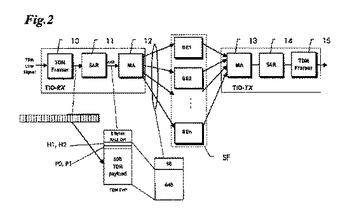

時分割多重信号を交換するために分割および再組み立て(SAR)機能を用いるスケーラブルなネットワーク要素

適度な機器コストでより高容量を可能にする、伝送網で時分割多重信号を交換するためのネットワーク要素を提供するために、ネットワーク要素は、いくつかの入力ポート(I;IO1−IO8)と、いくつかの出力ポート(O;IO1−IO8)と、入力ポートと出力ポート(IO1−IO8)を相互に接続するスイッチファブリック(SF;58)とを有する。スイッチファブリック(SF;58)は、セルのセルヘッダに含まれているアドレスに基づいて固定長のセルを交換するように構成された1つまたは複数のスイッチモジュール(SE1−SEn)を含むセルベースのスイッチである。入力ポート(I)は、入力時分割多重信号を分割して固定長のセルにし、各セルにアドレス情報を割り当てるための分割装置(11)を含む。出力ポート(O)は、上記スイッチファブリック(SF;58)から受信したセルを再組み立てして出力時分割多重信号にするための再組み立て装置(14)を含む。アドレス情報は、ファブリックアドレス(H1、H2)およびTDMアドレス(P0、P1)を含む。スイッチファブリックは、ファブリックアドレス(H1、H2)に従ってセルを対応する出力ポート(O)に交換し、再組み立て装置(14)は、TDMアドレス(P0、P1)に従ってセルを再組み立てする。  (もっと読む)

(もっと読む)

自己タイミング型時分割多重化バスを使用した相互接続

集積回路の通信バス上のトランスポートユニット間でデータ及びタイミング情報を含む信号を送信する方法は、バス上のすべてのトランスポートユニットのクロックトリガを生成するステップであって、それによって、各先行トランスポートユニットを起動して、隣接する後続トランスポートユニットへウェイブ-フロントで前記信号の送信を開始し、該ウェイブ-フロントはトランスポートユニットのそれぞれにおいて共通の時点で起動される、生成するステップと、すべてのトランスポートユニットが、自身が前記先行トランスポートユニットから前記信号で受信するデータ及びタイミング情報の少なくとも一方にタイミング調整を適用するステップを備えており、該適用するステップは、(1)先行トランスポートユニットからの前記データをキャプチャすること、(2)先行トランスポートユニットから前記後続トランスポートユニットへ通信バス上で前記データを変更することなく中継すること、及び(3)通信バスへ新たなデータをロードすること、の少なくとも1つを、更新されたタイミング情報を用いて後続のウェイブ-フロントで行う。  (もっと読む)

(もっと読む)

クロスコネクトパス試験システム及びそれに用いるパス試験方法

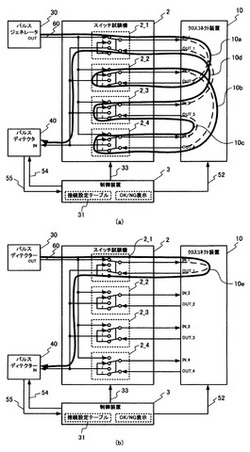

【課題】クロスコネクト装置が多数のチャネル数を有する場合でも、短い作業時間と少ない作業工数でパス状態を試験することを可能にする。

【解決手段】入力端子IN_1及び出力端子OUT_1をパルスジェネレータ30及びパルスディテクタ40に各々接続するとともに、他の入出力端子IN_2〜IN_4、OUT_1〜OUT_4を経由しながら、入力端子IN_1から出力端子OUT_1までを連続的に繋ぐパスをクロスコネクト装置10に設定する第1パス設定と、入力端子IN_1を出力端子OUT_1に折り返し接続するパスをクロスコネクト装置10に設定する第2パス設定とを、チャネル1〜4の各々について実行し、クロスコネクト装置10のパス状態を試験することを特徴とするクロスコネクトパス試験システム1。

(もっと読む)

スイッチング帯域幅を向上させるスイッチングシステムおよび方法

交換帯域幅を向上させる交換システムおよび方法を提供する。システムは、ATCA/ATCA300アーキテクチャと互換性があり、バックプレーンといくつかのノードボードと少なくとも2つのハブボードとを備える。ノードボードは、バックプレートを使用してハブボードと接続される。すべてのノードボードは少なくとも2つのハブボードと接続される。異なるデータは、ノードボードと少なくとも2つのハブボードとの接続により形成された少なくとも2つのデータリンク上で送信され、少なくとも2つのハブボードはノードボード間でデータ交換を互いに認識する。現在のATCA/ATCA300標準によって規定された物理構造およびバックプレートコネクタ配信と互換性があるケースでは、本発明は、マルチプレーン交換の方法で、ノードボード間で交換相互接続された帯域幅を拡大することによりノードボード間の効率的な通信帯域幅を提供する。 (もっと読む)

ネットワークオンチップシステムのスイッチング装置及びそのスケジューリング方法

【課題】転送パケット数に応じて柔軟にコードの長さを決定することにより、スイッチの性能を向上させるネットワークオンチップシステムのスイッチング装置及びそのスケジューリング方法を提供する。

【解決手段】ネットワークオンチップシステムのスイッチング装置は、複数個の入力ポート200aと複数個の出力ポート200bを有するスイッチング部100と、入力ポート200aと前記出力ポート200b間の転送経路を設定し、複数個の入力ポート200aのうちデータを保有する入力ポート数に基づいてコードの長さを決定し、設定された転送経路に対応する入力ポート200a及び出力ポート200bに決定されたコードの長さに所定のコードを割当てるスケジューラ300とを備える。これにより、スイッチの性能を向上させることができる。

(もっと読む)

多重変換装置

【課題】多重変換装置を伝送システムの方式の変更に対応できるようにアップグレード可能に構成する。

【解決手段】たとえば、現用系:予備系高速伝送路が1:1構成のLTEを高速伝

送路とのインタフェースを担う2組の10Gインタフェース10、低速伝送路との

間の多重変換を行う対象とする高速伝送路を選択するSELH30などのユニットで構成する。このLTEを2Fiber BLSR対応のADMにアップグレードする場合には、ユニットSELHを、高速伝送間および低速伝送路との間で各タイムスロットの信号の交換を行うSWHに交換する。SELHのSWHの外部との間の信号のインタフェースを共通化すると共に、各々の信号の入出力間の遅延時間を一致させておくことにより、運用中のユニット交換によるアップグレードを可能とする。

(もっと読む)

通話路制御装置

【課題】 通話路系パッケージに割当てられたハイウェイおよび通話回路に割当てられたタイムスロットを監視し、基本通話系パッケージに専用のハイウェイを設けず、必要とされるタイムスロット数のハイウェイを検出して基本通話系パッケージに割当て可能な通話路制御装置を提供する。

【解決手段】 送信ハイウェイ番号SHW0〜SHW3の送信ハイウェイおよび受信ハイウェイ番号RHW0〜RHW3の受信ハイウェイに接続し、通話路系パッケージ8が未搭載の送信ハイウェイおよび送信ハイウェイを選択するハイウェイ選択手段6と、電子交換機1に必須のPB受信器などの基本通話系パッケージ7を備える。

(もっと読む)

光TDMネットワーク管理方法、光TDMネットワーク管理プログラム、そのプログラムを記憶した記憶媒体および光TDMネットワーク管理装置

【課題】 光スイッチのスイッチング速度が低速な場合でも、光TDM方式の伝送を可能とする。

【解決手段】 管理装置10がスロット割り当て情報を参照し、各リンク50のスロットのうち、既に出力ポートが割り当てられている第1のスロットおよび新規パスの出力ポート32aとは異なる出力ポートが割り当てられているスロットを中心とした前後所定スロット数の範囲にある第2のスロットには新規パスの割り当てを不可とする識別子を記した新規パスの割り当て可能性リストを作成し、このリストに基づき光スイッチ30のスイチング制御を行う構成とした。

(もっと読む)

イーサネット(登録商標)受動光ネットワーク内でパケットを転送する方法および装置

本発明は、中央ノードと少なくとも1つのリモートノードとを含む、イーサネット(登録商標)受動光ネットワーク(EPON)内でのパケットの転送を容易にするシステムを提供する。動作の間、システムは、中央ノードとリモートノードとの間の論理リンクに対応する論理リンク識別子(LLID)をリモートノードに割り当てる。システムはまた、中央ノード内のスイッチのポートと対応付けて、スイッチは多数のポートを有し、ポートは物理ポートまたは仮想ポートで、スイッチの多数のポートをネットワーク側ポートとユーザ側ポートとに分割する。ネットワーク側ポートから下流側パケットを受信するとすぐに、システムは、マッピングテーブルをサーチして、下流側パケットの1つ以上のフィールド値がLLIDまたはポートのいずれかに対応するかどうか判定する。LLIDを下流側パケットに割り当てて、下流側パケットをリモートノードに送信する。  (もっと読む)

(もっと読む)

非対称構成用に最適化されたブロードキャスト・ルータ

ブロードキャスト・ルータを提供する。このブロードキャスト・ルータには、少なくとも1つの入力シャーシ(401)と少なくとも1つの出力シャーシ(450)とが含まれている。入力シャーシの各々には、複数の入力カード(410)と1つの拡張カード(415)とが含まれている。複数の入力カードは、ブロードキャスト・ルータに入力されるデータを最初に受信する。拡張カードは、ブロードキャスト・ルータに入力されたそれぞれのデータを受信する。拡張カードは、複数の入力カードからのそれぞれのデータを受信して、ブロードキャスト・ルータ内に於ける伝送用にデータを構成処理する。少なくとも1つの出力シャーシの各々には、マトリックス・カード(465)と複数の出力カード(460)とが含まれている。マトリックス・カードは、少なくとも1つの入力シャーシの全てからデータを受信して、複数の出力カードのうちの適切なものにデータをルーティングする。複数の出力カードは、それぞれ、マトリックス・カードからデータを受信して、ブロードキャスト・ルータ外にデータを出力する。少なくとも1つの入力シャーシの各々には上記複数の出力カードもその他の如何なる出力カードも含まれておらず、且つ、少なくとも1つの出力シャーシの各々には上記複数の入力カードもその他の如何なる入力カードも含まれていない。

(もっと読む)

(もっと読む)

1 - 10 / 10

[ Back to top ]