Fターム[5L106CC11]の内容

半導体メモリの信頼性技術 (9,959) | 冗長手段 (1,538) | アドレス、経路切換え手法 (285)

Fターム[5L106CC11]の下位に属するFターム

レーザで切断 (81)

電気的に溶断又は設定 (182)

Fターム[5L106CC11]に分類される特許

1 - 20 / 22

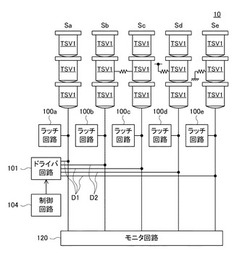

半導体装置及びその試験方法

【課題】論理値の反転処理を行う回路をコアチップ側に設けることなく、TSVを含む電流パスラインのショート不良を検出する。

【解決手段】半導体装置10は、第1及び第2の電流パスSa,Sbと、これらとそれぞれ電気的に接続する第1及び第2のラッチ回路100a,100bと、第1のラッチ回路100aに第1のデータD1を供給するとともに、第2のラッチ回路100bに第1のデータとは逆の論理値を有する第2のデータD2を供給するドライバ回路101と、第1のデータD1が第1のラッチ回路100aに供給され、かつ第2のデータD2が第2のラッチ回路100bに供給されない第1の期間と、第2のデータD2が第2のラッチ回路100bに供給され、かつ第1のデータD1が第1のラッチ回路100aに供給されない第2の期間と、が交互に繰り返されるよう、ドライバ回路101を制御する制御回路104と、モニタ回路120とを備える。

(もっと読む)

半導体装置及びこれを備えるデータ処理システム

【課題】散発的に発生するビット不良を救済可能な半導体装置を改良する。

【解決手段】ビット線MIOに接続されたライトアンプWAMPと、スイッチSW1を介してビット線MIOに接続されたリードアンプRAMPと、ライトポートがスイッチSW2を介してビット線MIOに接続され、リードポートがスイッチSW3を介してリードアンプRAMPに接続された救済記憶素子SCとを備える。不良メモリセルへのアクセスが要求された場合、ライト動作時においては、スイッチSW2をオンすることによりライトアンプWAMPからビット線MIOを介して救済記憶素子SCにライトデータを供給し、リード動作時においては、スイッチSW1をオフしスイッチSW3をオンすることにより、救済記憶素子SCから読み出されたリードデータをビット線MIOを介することなくリードアンプRAMPに供給する。

(もっと読む)

半導体記憶装置

【課題】不良救済効率を改善する。

【解決手段】サブワード線レベルの不良のときとメインワード線レベルの不良のときとで、スペアワード線の選択態様を変更する。スペア判定結果信号SP2が活性化される時同時にスペア判定結果信号SP1が活性化される時には、3本のノーマルサブワード線間においてショート不良が存在する。この場合には、スペア判定結果信号SP1が活性化されるため、ノーマルロウデコーダ264が非活性状態であり、スペアメインワード線のみが選択されてスペアサブワード線対により不良救済が実行される。この場合においても、ツインセルモードにしたがってサブワード線を選択することができる。

(もっと読む)

半導体記憶装置

【課題】 半導体記憶装置に面積の大きな冗長メモリセルアレイ、高感度冗長センス増幅器を設けることによる、半導体記憶装置の面積に与える影響を比較的小さくすることが課題である。

【解決手段】 メモリセルアレイは行方向および列方向に沿って2次元的に配置された複数のメモリセルを有し、複数のメモリセル中の少なくとも一列の複数のメモリセルが面積の大きな冗長メモリセルとして割り当てられる。行方向に沿って配置され、各々が前記メモリセルアレイの各列の列方向上に設けられた複数のセンス増幅器中、冗長メモリセルとして割り当てられた少なくとも一列の複数のメモリセルの列方向上に設けられた少なくとも1個のセンス増幅器が高感度冗長センス増幅器として割り当てられる。

(もっと読む)

半導体記憶装置

【課題】従来の半導体記憶装置では、遅延故障等に起因するビット誤りを訂正することが困難である問題があった。

【解決手段】本発明の半導体記憶装置は、格子状に配列されたデータセルを有するデータ格納領域22aと、データ格納領域22bに格納されたデータのうち同一の行に格納されるデータ群に対応して設けられる1ビットのパリティデータを格納する冗長データ格納領域22bと、データ群に含まれるデータのうち不良位置情報Sにより指定される不良データをパリティデータに置き換えたパリティ演算用データ群を出力する第1のスイッチ部23と、パリティ演算用データ群に基づき不良データを訂正した訂正データを生成する複合器25と、不良位置情報に基づきデータ群に含まれる不良データを訂正データに置き換えた読み出しデータ群を出力する第2のスイッチ部24と、を有する。

(もっと読む)

メモリテスト回路及び半導体メモリ装置

【課題】チップ外に設ける端子数を少なくすることができるメモリテスト回路及び半導体メモリ装置を提供すること。

【解決手段】本発明にかかるメモリテスト回路41は、メモリセルと、当該メモリセルが不良メモリセルである場合に置き換えて救済するための冗長セルとを有する半導体メモリ装置に設けられている。冗長セルが使用されていないテスト結果情報を格納するAレジスタ32と、冗長セルが使用されているテスト結果情報を格納するBレジスタ33の2種類のレジスタを設けている。Aレジスタ32よりテスト結果情報を読み出してテスト用の置換アドレスデータを生成し、Bレジスタ33よりテスト結果情報を読み出して外部に出力する。

(もっと読む)

半導体装置及びその制御方法

【課題】同一列に並んだ複数のメモリセクタそれぞれのメモリセルに不良が発生した場合でも、全ての不良メモリセルを救済すること。

【解決手段】本発明は、複数の不揮発性メモリセルから構成される、行列状に配置された複数のメモリセクタ12と、メモリセクタ12のビットライン18に接続し、同一列に配置されたメモリセクタ12に跨るグローバルライン24と、グローバルライン24延伸方向に配置された複数の冗長セクタ14と、外部回路から入力されたメモリセクタ12のアドレスが不良メモリセルを有するメモリセクタ12のアドレスと一致するか判断し、一致した場合に、外部回路から入力されたメモリセクタ12のアドレスを不良メモリセルを有するメモリセクタ12に対応する冗長セクタ14のアドレスに変換する制御回路と、を具備する半導体装置である。

(もっと読む)

不良な列にあるアドレスでプログラミングするのに時間を消費することを回避する方法

【課題】 不良列のアドレスをプログラミングする時間を低減する。

【解決手段】 (a)被試験メモリに適用される同じアドレス30によりアドレス指定されるタグRAMを確立し、(b)適用されるアドレスが不良な列に関連することを判定し、(c)タグRAM中の前記適用されるアドレスに前記列が不良であることの表示123、124を記憶し、(d)(a)〜(c)の後に、前記被試験メモリの試験の次の段階の間に自動データ置換機構(35”)をイネーブルし、そして、(e1)前記タグRAMに試験アドレスを適用しつつ、前記被試験メモリを前記試験アドレスにプログラミングすることを試みて、(e2)前記試験アドレスが不良な列に属するものであることの表示を前記タグRAMが含んでいる場合には、被試験メモリが正常であると即座に通知するようにする1によってプログラミングされるべきデータ値を置換することを含む方法を提供する。

(もっと読む)

半導体記憶装置

【課題】歩留まりを向上できる半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、複数のメモリチップ15−1〜15−8と、前記複数のメモリチップのいずれか1つが不良チップとなった場合に前記不良チップと置換される冗長用の予備チップ17と、前記複数のメモリチップおよび前記予備チップを同一のパッケージ内に封止する外囲器14とを具備する。

(もっと読む)

ビットエラーの修復方法および情報処理装置

【課題】フラッシュメモリにおいて発生するビットエラーを効果的に修復する。

【解決手段】フラッシュメモリ4から読み出される一時記憶データのエラーをチェックするエラー訂正機能を備える。エラーが発見されると、そのエラー情報は、レジスタ9に一時記憶された後、適切なタイミングで不揮発性メモリ6に記憶される。電源投入時などの適切なタイミングで、不揮発性メモリ6に記憶されたエラー情報に基づき、エラーが発見された一時記憶データを再度読み出してエラー訂正を行ってフラッシュメモリ4に書き戻す。リードディスターブなどの回復可能なビットエラーを修復することができる。通常の読み出し処理が支障なく実行でき、ユーザに不快感を与えなくて済む。

(もっと読む)

半導体記憶装置

【課題】パリティデータを格納した場合においてもデータ圧縮を行いつつテストを実行することを可能にした半導体記憶装置を提供する。

【解決手段】メモリセルアレイ1は、複数のワード線WLと複数のビット線BLの交点に形成された複数のメモリセルMCを有する。メモリセルアレイは複数のセグメントSGに分割され、各セグメントSGからは4本のメインデータ線MDLが延びている。また、パリティデータ記憶用のセグメントSGPからは、パリティ用メインデータ線MDLPが延びている。第1判定回路10Aは、メインデータ線MDLから読み出されたデータとその期待値とを比較してその一致・不一致を判定する。第2判定回路10Bは、複数のパリティ用メインデータ線MDLPから読み出されるデータとその期待値とを比較してその一致・不一致を判定する。第2判定回路10Bは、その判定結果を選択的に出力する選択回路105を備えている。

(もっと読む)

メモリシステム

【課題】アクセス速度の低下をできるだけ抑えながら、メモリの故障を確実に救済する。

【解決手段】メモリシステムであって、故障を救済するための冗長領域をそれぞれ有する複数のメモリバンクを有するメモリを備え、同一のメモリバンクで複数の故障が発生した場合には、少なくとも1つの故障を、そのメモリバンクが有する冗長領域を用いて救済し、その他の少なくとも1つの故障を、他のメモリバンクが有する冗長領域を用いて救済する。

(もっと読む)

半導体装置及びその製造方法

【課題】 ヒューズを用いずに救済処理を行なう。

【解決手段】 半導体チップに予備回路が形成されており、この予備回路の接続変更によって救済処理を行なう半導体装置において、前記半導体装置は、前記半導体チップと半導体装置の外部端子とを再配線層によって接続しており、この再配線層のパターンを変えて、前記予備回路の接続変更を行なっている。また、その製造方法において、前記半導体装置は、前記半導体チップと半導体装置の外部端子とを再配線層によって接続しており、形成された回路を検査する工程と、前記検査によって不良と判定された回路を、前記再配線層のパターンを変えて、前記予備回路に接続変更を行なう工程とによって、救済処理を行なう。

(もっと読む)

半導体記憶装置

【課題】

カラム不良発生時にも、エラー訂正効率の低下を回避する半導体記憶装置の提供。

【解決手段】

メモリセルアレイ101と、不良セルの置換を行うためのリダンダンシセル118と、メモリセルのデータの誤り訂正を行う誤り訂正回路110と、誤り訂正回路で誤り訂正されたメモリセルのロウ座標とカラム座標を保存しておく、誤り訂正セルロウ座標情報格納用レジスタ119、誤り訂正セルカラム座標情報格納用レジスタ120と、誤り訂正回路110からの誤り訂正情報より、一のカラム線上での誤り訂正ビットの数があらかじめ定められた値を超えたか検出するECC訂正数検出回路128と、誤り訂正数があらかじめ定められた値を超えた場合、前記一のカラム線をリダンダンシセルで置換するリダンダンシ切替回路127と、を備えている。

(もっと読む)

半導体メモリ

シフトレジスタは、通常メモリセル列の通常ワード線および冗長メモリセル列の冗長ワード線のいずれかをリフレッシュ要求毎に順次活性化させるために、これらのワード線にそれぞれ対応する複数のラッチで構成される。活性化回路は、シフトレジスタの出力に応じて通常ワード線および冗長ワード線のいずれかを活性化させる。第1記憶回路は、不良の通常メモリセル列を示す不良アドレスを予め記憶する。第1活性化制御回路は、シフトレジスタの出力が第1記憶回路の不良アドレスに対応するときに、不良アドレスに対応する通常ワード線の活性化を禁止する。不良の通常メモリセル列の通常ワード線は活性化されないため、シフトリフレッシュ方式を採用する半導体メモリにおいて、不良の通常メモリセル列のリフレッシュを禁止でき、リフレッシュ動作に伴う充放電電流の無駄な消費を回避できる。  (もっと読む)

(もっと読む)

保安リダンダンシーブロックを具備したNANDフラッシュメモリ装置及び保安ブロックをリペアする方法

【課題】本発明は保安リダンダンシーブロックを具備したNANDフラッシュメモリ装置に関する。

【解決手段】本発明によるNANDフラッシュメモリ装置は、メインデータを貯蔵するメインブロックと、保安データを貯蔵する保安ブロックと、前記メインブロックまたは保安ブロックにフェイルが発生した時にフェイルになったブロックを取り替えるためのリダンダンシーブロックとを含む。ここで、前記リダンダンシーブロックは、ヒューズ情報に応じて前記保安ブロックを保安リダンダンシーブロックに取り替える。また、前記リダンダンシーブロックは別途の保安リダンダンシーブロックを具備して前記保安ブロックをリペアする。本発明によると、保安ブロックにフェイルが発生した場合に、NANDフラッシュメモリ装置をフェイル処理しなければならない従来の問題点を改善することができる。

(もっと読む)

データ反転制御回路及びこのデータ反転制御回路を有する記憶装置及びデータ反転制御方法

【課題】LOW側冗長ワード線とHIGH側冗長ワード線とを有するとともに、ツイスト構造を有するビット線及びビット補線とを有する記憶装置に、前記ビット線と前記ビット補線とのツイストにともなってデータを反転または非反転させながら入力させるデータ反転制御回路、及びこのデータ反転制御回路を有する記憶装置、及びデータ反転制御方法において、データ反転制御を高効率化する。

【解決手段】LOW側冗長ワード線を使用するようにワード線のアドレスを前記LOW側冗長ワード線方向へシフトする起点となっているLシフト設定アドレスが、HIGH側冗長ワード線を使用するようにワード線のアドレスをHIGH側冗長ワード線方向へシフトする起点となっているHシフト設定アドレスよりも大きい場合に、Lシフト設定アドレスとHシフト設定アドレスのアドレスデータを入れ替える。

(もっと読む)

内部発生されたプログラミング電圧を用いてアンチヒューズをプログラムする方法及び装置

【課題】アンチヒューズを、集積回路の他の構成部品に損傷を与えずに比較的高い電圧を用いてプログラムする方法および装置を提供する。

【解決手段】アンチヒューズのためのプログラミング回路は、非プログラミング期間中にキャパシタを電源電圧に帯電するブート回路を利用する。アンチヒューズがプログラムされるべきとき、電源電圧が印加されるキャパシタのプレートが0に切替えられ、これによって、キャパシタのもう一方のプレートを負電圧とする。この負電圧はアンチヒューズの一方のプレートに切替えられ、アンチヒューズのもう一方のプレートは外部源から正電圧を受ける。これにより、集積回路のいずれのノードに印加されるいずれの電圧よりも大きな電圧が、アンチヒューズの両端にわたって印加される。

(もっと読む)

セット連想リペアキャッシュシステムおよび方法

本発明は識別された故障メモリセルを修正または修復するセット連想リペアキャッシュシステムを利用してメモリデバイスのスケーリングおよびその動作を容易にする。リペアキャッシュ領域ルータ(602)がメモリアドレスのリペア領域部をリペアキャッシュ領域と比較して整合リペアキャッシュ領域を識別する。次に、ローカルリペア個所ルータ(603)がメモリアドレスのリペアアドレス部を整合リペアキャッシュ領域に特有のローカルリペア個所アドレスと比較して整合ローカルリペアアドレスを識別する。整合ローカルリペアアドレスが識別されると、リペアコンポーネント(606)は整合ローカルリペアアドレスおよび整合するリペアキャッシュ領域に従ってリペア個所へのアクセスを提供する。また、メインメモリ(604)がメモリアドレスに従って記憶場所へのアクセスを提供する。他のシステムおよび方法も開示される。  (もっと読む)

(もっと読む)

メモリアレイにおける特定のコラムに冗長性ウィンドウを定義するための方法及びシステム

メモリ冗長性の方法(600)、そのシステム(100)が記載される。メモリアレイは、通常、メモリセルの複数のコラム(例、ビット線)を含む。メモリアレイの特定のコラム(例、欠陥)が識別される(610)。冗長性ウィンドウ(410)が欠陥コラム(620)を含む隣接コラムグループを選択することによって定義される。選択されたコラムグループにおけるコラムの数は、メモリアレイに結合される冗長性ウィンドウ(110)におけるコラムの数に等しい可能性がある。この冗長性アレイは、情報を記録するためのものであり、そうでなければ、情報は冗長性ウィンドウのメモリセルに記録され得る。このグループは欠陥コラムの一方側に少なくとも1コラムがあり、欠陥コラムの他方側にもう1つのコラムがあるように選択される。通常、欠陥コラムの各側に多数のコラムがある。これらのコラムにおけるメモリセルはプログラムされる(630)。  (もっと読む)

(もっと読む)

1 - 20 / 22

[ Back to top ]