Fターム[5L106CC12]の内容

半導体メモリの信頼性技術 (9,959) | 冗長手段 (1,538) | アドレス、経路切換え手法 (285) | レーザで切断 (81)

Fターム[5L106CC12]に分類される特許

1 - 20 / 81

半導体装置

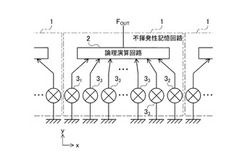

【課題】不揮発性記憶回路の出力として「未破壊」を示す第1の論理レベルが期待される場面で、第1及び第2の不揮発性記憶素子の一方に干渉破壊が発生したとしても、第3の不揮発性記憶素子に干渉破壊が生じない限り、不揮発性記憶回路に正しく第1の論理レベルを出力させる。

【解決手段】半導体装置は、第1及び第2の不揮発性記憶素子31,32と、少なくとも1つの第3の不揮発性記憶素子33と、少なくとも1つの第3の不揮発性記憶素子33すべてと、第1及び第2の不揮発性記憶素子31,32のうちの少なくともいずれか一方とが未破壊状態である場合に、未破壊を示す第1の論理レベルを出力する論理演算回路2とを有する不揮発性記憶回路1を備える。

(もっと読む)

半導体装置及びトリミング方法

【課題】ヒューズ素子の列数増に伴うトリミング時間の伸長を抑制する。

【解決手段】x方向に延伸する接地配線Gと、接地配線のy方向の一方側に設けられたヒューズ素子領域Aにx方向に沿って3列に並べて配置され、かつそれぞれの一端が接地配線Gに共通に接続される複数のヒューズ素子と、ヒューズ素子領域Aを挟んで接地配線Gの反対側に設けられ、ヒューズ素子領域Aに配置された複数のヒューズ素子それぞれの他端と接続される救済回路とを備え、上記複数のヒューズ素子は、それぞれ1つの欠陥選択線を示すアドレス情報を記憶する複数のヒューズ素子グループに所定個ずつグループ化され、同一のヒューズ素子グループに属する所定個のヒューズ素子は、同一列に配置されることを特徴とする

(もっと読む)

半導体ウエハ、半導体装置、および、半導体装置の製造方法

【課題】半導体チップのチップ面積の削減を図るとともに、半導体チップへの入力を記憶させる時間を短縮する。

【解決手段】本発明の半導体ウエハ1は、チップ領域10に形成され、絶縁膜を有し、電圧の印加による絶縁膜の絶縁破壊により導通状態となる複数のアンチヒューズ14を有するアンチヒューズ回路12と、チップ領域10を区画するダイシング領域20に複数のアンチヒューズ14の各々に対応して形成され、配線を有し、レーザー照射による配線の切断により非導通状態となる複数のレーザーヒューズ24を有するレーザーヒューズ回路22と、複数のアンチヒューズ14のうち、半導体チップへの入力に応じて非導通状態とされたレーザーヒューズ22に対応するアンチヒューズ14の有する絶縁膜に、電源からの電圧を印加させて、そのアンチヒューズ14を導通状態とする制御回路13と、を有する。

(もっと読む)

半導体装置

【課題】トリミング時間の短縮とヒューズ素子による占有面積の縮小を達成しつつ、高速アクセスを実現する。

【解決手段】不良ワード線のアドレスを記憶するロウヒューズ回路21と、不良ビット線のアドレスを記憶するカラムヒューズ回路22と、ロウアドレスXADD又はロウヒューズ回路21から読み出されたアドレスRXADDに基づいてワード線WL又は冗長ワード線RWLを選択するロウデコーダ11と、カラムアドレスYADD又はカラムヒューズ回路22から読み出されたアドレスRXADDに基づいてビット線BL又は冗長ビット線RBLを選択するカラムデコーダ12とを備える。ロウデコーダ11、ロウヒューズ回路21及びカラムヒューズ回路22はメモリセルアレイ10の長辺10aに沿って配置され、カラムデコーダ12はメモリセルアレイ10の短辺10bに沿って配置される。

(もっと読む)

半導体装置

【課題】不良チップの救済効率を向上させ歩留まりを向上させる。

【解決手段】第1半導体チップのメモリセルアレイは、ノーマルセルアレイとスペアセルアレイとを備える。第1不良アドレスデータ出力回路は、メモリセルアレイ中の不良メモリセルのアドレスを示す第1不良アドレスデータを出力する。第1比較回路は、アドレスデータと第1不良アドレスデータとを比較して第1の一致信号を出力する。第2不良アドレスデータ出力回路は、メモリセルアレイ中の不良メモリセルのアドレスを示す第2の不良アドレスデータを出力する。第2比較回路は、アドレスデータと第2の不良アドレスとを比較して第2の一致信号を出力する。

(もっと読む)

メモリ装置

【課題】少ない情報で不良メモリセルを冗長メモリセルに切り替えることができるメモリ装置を提供することを課題とする。

【解決手段】メモリ装置は、複数のメモリセルと、冗長メモリセルと、複数のメモリセルの中の不良メモリセルを冗長メモリセルに切り替えるセレクタとを含む複数のメモリセルブロック(501〜503)と、複数のメモリセルブロックの各々が不良メモリセルを有するか否かの不良情報、及び不良メモリセルを有するメモリセルブロック内の不良メモリセルを特定するための特定情報に基づき、複数のメモリセルブロックのセレクタの制御信号を出力する制御回路(522)とを有し、制御回路は、複数のメモリセルブロックのセレクタの制御信号の各ビット線に対応して設けられ、特定情報をシリアルにシフトするための複数のフリップフロップ(FF0〜FF8)を有する。

(もっと読む)

半導体装置

【課題】不良選択線のアドレスを記憶するための回路からイネーブルヒューズ回路を除去する。

【解決手段】アクセスが要求されたアドレスと欠陥のある選択線のアドレスとを比較し、これらが一致したことに応答してヒット信号HIT0を生成するヒット信号生成回路40と、ヒット信号HIT0の活性化に応答して選択される冗長選択線RWL/RBLとを備える。ヒット信号生成回路40は、欠陥のある選択線のアドレスが第1のアドレス範囲にある場合、比較の結果にかかわらずヒット信号HIT0を非活性状態とする。これにより、アドレス記憶用のヒューズ回路の出力の一部を参照するだけで、ヒット信号生成回路40が使用状態であるか否かを判定することができる。これにより、イネーブルヒューズ回路を排除しつつ、ヒット信号生成回路40が使用状態であるか否かをより少ない回路素子を用いて判定することができる。

(もっと読む)

半導体記憶装置

【課題】ヒューズセットを用いた冗長セル列の選択の簡易化を図る。

【解決手段】半導体記憶装置は、メモリセルブロック40−1,・・・と、複数の冗長セル列41−11,・・・と、冗長判定信号をそれぞれ出力する複数のアドレス判定回路50−11,・・・と、前記冗長判定信号に基づき、アドレス信号をデコードして冗長セル列41−11,・・・及びメモリセルブロック内のメモリセル列を選択する複数のデコーダ60−11,・・・とを備えている。各アドレス判定回路は、不良メモリセルの位置を示す冗長位置情報を持つヒューズ51a−1〜51a−8と、メモリセルブロックを選択するためのブロック選択情報を持つヒューズ51a−9と、を有するヒューズセット51Aを備え、前記冗長位置情報がアドレス信号と一致するか否かを判定し、この判定結果にブロック選択情報を付加した冗長判定信号を出力する。

(もっと読む)

半導体装置及びその制御方法並びにその情報処理システム

【課題】階層化ビット線構成を有するメモリセルアレイにおいてプリチャージ回路を削減しつつ冗長判定に伴うアクセス速度の低下を防止し得る半導体装置を提供する。

【解決手段】階層化ビット線構成の通常領域であるメモリ領域SM(0)及び冗長領域を含むメモリ領域SM(m)を有する。スタンバイ時にはグローバルビット線GBL及びメモリ領域SM(m)のローカルビット線LBLをプリチャージし、メモリ領域SM(0)のローカルビット線LBLはプリチャージしない。例えば、メモリ領域SM(0)のアクティブ動作時には直ちにメモリ領域SM(0)のローカルビット線LBLをプリチャージし、その後の冗長判定結果に応じて各メモリ領域SM(0)、SM(m)の階層スイッチSWをそれぞれ維持または非活性状態に制御して通常メモリセルMC又は冗長メモリセルRCをアクセスする。

(もっと読む)

半導体装置及びその製造方法

【課題】高速アクセス時に初めて不良となるアドレスを救済する。

【解決手段】メモリセルアレイ101に含まれる不良メモリセルを置換するための冗長回路102,103と、不良メモリセルのアドレスを記憶する電気ヒューズ回路142と、メモリセルアレイ101から読み出されるテストデータの正誤判定を行うことによって判定信号を生成するデータ判定回路107aと、第1の動作モードにおいては判定信号P/Fが活性化している場合に与えられたアドレス信号を電気ヒューズ回路142に供給し、第2の動作モードにおいては判定信号P/Fに関わらず外部から供給されるデータマスク信号DMが活性化している場合に与えられたアドレス信号を電気ヒューズ回路142に供給する解析回路143と、を備える。本発明によれば、高速アクセス時に初めて不良となるアドレスについても正しく救済することが可能となる。

(もっと読む)

半導体装置及びその製造方法

【課題】不良メモリセルのアドレスを解析するのに必要なメモリの記憶容量を削減する。

【解決手段】メモリセルアレイ101に含まれる不良サブワード線及び不良ビット線をそれぞれ置換するためのロウ冗長回路102及びカラム冗長回路103と、不良サブワード線及び不良ビット線のアドレスをそれぞれ記憶する電気ヒューズ回路142a,142bと、第1の動作モードにおいては、判定信号P/Fが活性化している場合に与えられたアドレス信号に基づいて電気ヒューズ回路142a,142bの一方を選択し、第2の動作モードにおいては、判定信号P/Fが活性化している場合に与えられたアドレス信号に基づいて電気ヒューズ回路142a,142bの他方を選択するヒューズ選択回路146を備える。本発明によれば、冗長ワード線を用いた置換と冗長ビット線を用いた置換をフレキシブルに切り替えることができる。

(もっと読む)

半導体記憶装置

【課題】 省スペースによって従来よりも多くの論理回路及びヒューズブロックを設けることができる半導体記憶装置を提供する。

【解決手段】 ヒューズ露出窓を介して外部に露出して互いに並置された複数のヒューズ片を各々が含む複数のヒューズブロックがゲートアレイの近傍において縦列に配置され、電源配線と接地配線とが当該ヒューズ片の並置方向に沿って延在しており、ヒューズブロックの配置のために当該ゲートアレイの近傍のスペースを活用した半導体記憶装置。

(もっと読む)

半導体メモリ装置での冗長プログラム回路

【課題】半導体メモリ装置の冗長プログラム回路を提供する。

【解決手段】マスタヒューズを有し、該マスタヒューズのカッティングの有無を示す状態信号として動作イネーブル信号を生成するマスタヒューズ部と、マスタヒューズ部の動作イネーブル信号に応じて制御され、アドレス信号のビット数だけに対応する制御ヒューズを有し、欠陥セル情報に従い制御ヒューズのカッティングの有無をそれぞれ示す状態信号として第1−第M制御信号ペア(Mは前記アドレス信号ビットの数)を生成する制御ヒューズ部と、アドレス信号がデコーディングされたアドレスの信号ビットを第1−第M制御信号ペアの組合せ論理入力により対応的にデコーディングして、デコーディングアドレスの信号ビットのうち欠陥セル情報を有する論理状態がデコーディング出力端にそのまま伝達されるようにするデコーディング部と、を備える半導体メモリ装置での冗長プログラム回路を備える。

(もっと読む)

半導体記憶装置

【課題】半導体記憶装置において、メインワード線の断線故障が起きた場合に、断線箇所から先がフローティング状態になることにより、正常なワード線の信号に影響を及ぼすことを防止する。

【解決手段】メインワード線の遠端にラッチ回路を設け、断線箇所から先に電位が、ハイ電位に固定されるようにし、正常なワード線に影響しないようにする。

(もっと読む)

半導体記憶装置

【課題】対象アドレスと救済アドレスの一致時におけるアドレス置換の速度を向上させる。

【解決手段】アドレス判定回路116は、救済アドレスを保持し、救済アドレスとアクセス先のアドレスが一致するときヒット信号を発生させる。第1領域148と第2領域150の間にはエンコーダEX、EYが並ぶ。第2領域150側の列に属するエンコーダ回路EX4には、第1領域148のアドレス判定回路116と第2領域150のアドレス判定回路116それぞれからのヒット信号が共通に入力される。エンコーダEX4を出力先とする第1領域148のアドレス判定回路116と第2領域150のアドレス判定回路116は、第1領域148および第2領域150それぞれの回路配置可能領域においてエンコーダEX4にもっとも近い位置に配置される。

(もっと読む)

半導体装置及びその制御方法

【課題】電気ヒューズ素子からなるヒューズ回路をウェハ状態である前工程における一次救済及びパッケージ後である後工程における二次救済の両方で有効に利用する。

【解決手段】複数のアンチヒューズセットAFSETを含むヒューズ回路50と、ヒューズ回路50に書き込むべきアドレスを電気的に保持するヒューズアドレスレジスタ70と、ヒューズ回路50にアドレスを書き込むプログラム回路40とを備える。プログラム回路40は、第1のテストコマンドが発行された場合には該第1のテストコマンドと共に外部から入力されたアドレスをヒューズ回路40に書き込み、第2のテストコマンドが発行された場合には際にヒューズアドレスレジスタ70に保持されたアドレスをヒューズ回路50に書き込む。これにより、通常の後工程用のテスタを用いて不良メモリセルを冗長メモリセルに正しく置換することが可能となる。

(もっと読む)

半導体装置及びその製造方法

【課題】不良メモリセルのアドレスを解析するのに必要なメモリの記憶容量を削減する。

【解決手段】

複数のメモリセルに対して順番にテストを行い、テストによって不良メモリセルを検出するたびに、複数の不良メモリセルの相対的な配置関係に基づいてエラーパターン情報を更新するとともに、複数の不良メモリセルの少なくとも一部のアドレスに基づいてエラーアドレス情報を更新する。本発明によれば、解析用メモリの記憶容量を大幅に削減することが可能となることから、解析用メモリ自体を半導体装置内に搭載することも可能となり、この場合には、外部テスタに解析用メモリを設ける必要がなくなる。

(もっと読む)

半導体装置

【課題】パッケージング後に生じた不良セルを冗長セルに効率よく置換する。

【解決手段】半導体装置10は、複数のチップ100と、チップ100を制御するチップ200と、チップ100とチップ200とを接続する内部配線400とを備える。チップ100は、光学ヒューズ120及びその情報を保持するラッチ回路101と、内部配線400を介してチップ200から供給された電気ヒューズ220の情報を保持するラッチ回路102と、ラッチ回路101,102のいずれか一方の情報を選択する選択回路151を含み、選択された情報から冗長判定信号HITを生成する。本発明によれば、電気ヒューズの情報が内部配線を介してチップ200からチップ100に転送されることから、チップ100に電気ヒューズを設ける必要がなくなるとともに、転送に外部端子を使用しないことから、起動時間が増大することもない。

(もっと読む)

半導体装置及び書込データ検出方法

【課題】ヒューズROMに書き込まれているデータが、書き込む期待値とした期待値データと一致しているか否かを検出する機能を有する半導体装置を供給する。

【解決手段】本発明は、ヒューズROMの書込状態を示す書込データがヒューズ回路51A、51B及び51Cの各々から供給される比較部600を有している。この比較部600は、ヒューズROMに書き込むデータである期待値データも入力され、この期待値データとヒューズROMに実際に書き込まれている書込状態を示す書込データとを比較し、比較結果を出力する。そして、本発明によれば、出力回路65が複数のヒューズROMのデータの判定結果を1つの出力パッドNC501から1ビットの判定データとして出力する。

(もっと読む)

半導体装置

【課題】不良メモリセルの救済効率の高い半導体装置を提供する。

【解決手段】複数のメモリセルブロック(MBA、MBB)と、冗長行メモリセルブロック(RMBA、RMBB)と、複数のメモリセルブロックに共通に設けられ、記憶した不良メモリセルのアドレスと外部から入力されるアドレスとが一致した場合、一致したことを示す結果を出力する冗長フューズブロック(RFBLK5)と、冗長行メモリセルブロックの冗長救済単位を選択する冗長行選択信号(RXA1〜4、RXB1〜4)が入力されると冗長救済単位の一つを選択する冗長行ドライバ(REDXDA1〜4、REDXDB1〜4)と、一致したことを示す結果が入力されると、記憶する複数の冗長行ドライバのうちからいずれかの冗長行ドライバを選択するかの選択情報に基づいて冗長行選択信号を出力する冗長行ドライバ選択回路(XRS)と、を備える。

(もっと読む)

1 - 20 / 81

[ Back to top ]