Fターム[5L106CC21]の内容

半導体メモリの信頼性技術 (9,959) | 冗長手段 (1,538) | 不良部のアクセス禁止 (120)

Fターム[5L106CC21]の下位に属するFターム

冗長部能動化信号を用いるもの (45)

Fターム[5L106CC21]に分類される特許

1 - 20 / 75

メモリコントローラ

半導体装置

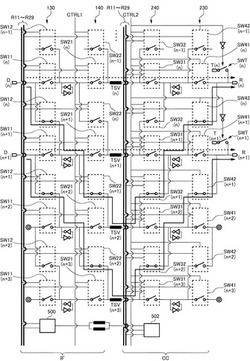

【課題】複数の貫通電極を選択的に利用可能な積層型の半導体装置において、回路動作を安定させる。

【解決手段】半導体記憶装置10は、インターフェースチップIFと複数のコアチップCCを含む。コアチップCCは、インターフェースチップIFに積層される。インターフェースチップIFとコアチップCCは複数の貫通電極TSVにより接続される。コアチップCCに含まれる入力切り替え回路240、230は、電源投入時における設定処理の前に、コアチップCCに含まれる複数の入力信号線と複数の貫通電極TSVとの接続をいったん遮断し、コアチップCCの設定後に、複数の入力信号線と複数の貫通電極TSVの接続を示す救済情報にしたがって各入力信号線を複数の貫通電極TSVのいずれかと接続する。

(もっと読む)

半導体記憶装置及びそのテスト方法

【課題】ロールコールテストに要する工数を削減できる半導体記憶装置及びそのテスト方法を提供する。

【解決手段】不良アドレスが格納される不揮発性の記憶素子を備えた半導体記憶装置にロールコールテスト時にマスク用テストモード信号を出力するテスト制御回路とロールコール回路とを備える。ロールコール回路は、アドレス信号と不良アドレスとをビット単位で比較し、その比較結果を出力する。また、ロールコール回路は、マスク用テストモード信号が入力されると、アドレス信号の所望のビットに対応する比較結果をマスクして上記アドレス信号と不良アドレスとが一致していることを示す値を出力すると共に、マスクされていないビットに対するロールコールテストを可能にする。

(もっと読む)

メモリシステム

【課題】不良メモリチップが発生した場合でも、並列駆動可能な組み合わせ数を最大限確保可能なメモリシステムを提供すること。

【解決手段】物理バンク内の不良メモリチップが識別可能な不良メモリチップ情報に基づき、不良メモリチップを使用せずに各レーン内において並列アクセス可能なメモリチップ数が最大となるように、論理バンクを構成する複数の物理バンクの組み合わせを動的に設定する。

(もっと読む)

半導体装置

【課題】不良チップの救済効率を向上させ歩留まりを向上させる。

【解決手段】第1半導体チップのメモリセルアレイは、ノーマルセルアレイとスペアセルアレイとを備える。第1不良アドレスデータ出力回路は、メモリセルアレイ中の不良メモリセルのアドレスを示す第1不良アドレスデータを出力する。第1比較回路は、アドレスデータと第1不良アドレスデータとを比較して第1の一致信号を出力する。第2不良アドレスデータ出力回路は、メモリセルアレイ中の不良メモリセルのアドレスを示す第2の不良アドレスデータを出力する。第2比較回路は、アドレスデータと第2の不良アドレスとを比較して第2の一致信号を出力する。

(もっと読む)

メモリ装置

【課題】少ない情報で不良メモリセルを冗長メモリセルに切り替えることができるメモリ装置を提供することを課題とする。

【解決手段】メモリ装置は、複数のメモリセルと、冗長メモリセルと、複数のメモリセルの中の不良メモリセルを冗長メモリセルに切り替えるセレクタとを含む複数のメモリセルブロック(501〜503)と、複数のメモリセルブロックの各々が不良メモリセルを有するか否かの不良情報、及び不良メモリセルを有するメモリセルブロック内の不良メモリセルを特定するための特定情報に基づき、複数のメモリセルブロックのセレクタの制御信号を出力する制御回路(522)とを有し、制御回路は、複数のメモリセルブロックのセレクタの制御信号の各ビット線に対応して設けられ、特定情報をシリアルにシフトするための複数のフリップフロップ(FF0〜FF8)を有する。

(もっと読む)

半導体記憶装置

【課題】不良メモリセルからのデータ読み出しを無効にし、救済メモリセルからのデータ読み出しを有効にする読み出し制御技術を改良した半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、複数のメモリバンクと、自己に対応するメモリバンク内のメモリセルからデータを読み出す複数のリードアンプと、複数のメモリバンク内の不良メモリセルの代わりの救済メモリセルと、データの入出力を行う入出力部と、不良メモリセルのアドレスを受け付けた場合にヒット信号を出力する判定部と、ヒット信号に応答して、不良メモリセルを有するメモリバンクに対応する特定リードアンプと入出力部とを非接続状態にし、特定リードアンプとは異なる所定リードアンプと入出力部とを接続状態にする接続制御部とを含み、所定リードアンプは、データ読出し時にヒット信号に応答して救済メモリセルからデータを読み出し入出力部に出力する。

(もっと読む)

不揮発性半導体記憶装置の領域設定方法および不揮発性半導体記憶装置

【課題】カンパニー領域専用のブロックが不要な不揮発性半導体記憶装置の領域設定方法を提供する。

【解決手段】不揮発性半導体記憶装置1のメモリセルアレイ2のブロックに不良ブロックが含まれていた場合に、ブロックにユーザー領域とカンパニー領域とを設定する方法において、メモリセルアレイは複数のバンクに分かれていて、各バンクはユーザー領域として使用する複数の通常ブロックと、1つ以上の冗長ブロックとを有していて、カンパニー領域を所定バンクの冗長ブロックに初期設定するステップと、通常ブロックのうちのいずれかが不良ブロックであった場合に、当該不良ブロックの代わりに使用する代替ブロックを、当該不良ブロックが属するバンクの冗長ブロックに設定するステップと、代替ブロックがカンパニー領域と重なった場合に、カンパニー領域を、空いている冗長ブロックに移動させるステップとを有している。

(もっと読む)

半導体メモリ、および製造方法

【課題】冗長セルに置き換え可能な不良セルを増加でき、歩留まりを向上させること。

【解決手段】メモリセルアレイ102はワードごとにxビット分のデータセルとyビット分の冗長セルとを有している。位置情報記憶部103はワードごとに不良セルの位置情報を記憶する。指定ワードの読み出し処理の場合、不良ビット代替回路104は、位置情報記憶部103内の指定ワードの不良セルの位置情報であるFAIL DATAに基づいて、メモリセルアレイ102内の指定ワードのx+yビット分のRAW READ DATAから不良セルのデータを除いたxビット分のREAD DATAを出力する。指定ワードへの書き込み処理であれば、不良ビット代替処理回路104は、FAIL DATAを用いて、xビット分のWRITE DATAをデータセルと冗長セルに書き込むx+yビットのRAW WRITE DATAに変換し、メモリセルアレイ102に書き込む。

(もっと読む)

半導体集積回路装置、制御記憶装置の制御方法及びプログラム

【課題】ブロック単位で構築された冗長構成の利点を最大限利用すると共に、制御記憶装置自体にエラーチェック機構が備えられていない場合であっても対処可能にする。

【解決手段】エラー検出部22は、読み出し制御部21が通常の運用時における制御装置3の動作を規定する通常運用データを冗長メモリ11,12から読み出す前に、通常運用データを格納するブロックに対してチェック処理を行う。当該チェック処理によるエラー情報はエラー情報保持部13に保持させる。読み出し制御部21は、エラー情報保持部13に保持されたエラー情報に基づいて、エラーが検出されたブロックに冗長構成的に対応する健全なブロックが存在するか否かを判定し、健全なブロックが存在する場合には、通常運用データの読み出しを行う。

(もっと読む)

試験装置

【課題】試験時間を短縮化する。

【解決手段】被試験メモリを試験する試験装置であって、被試験メモリのアドレス毎に被試験メモリから出力された出力データと期待値データとを比較して、出力データと期待値データとが不一致である場合にフェイルデータを出力する論理比較器と、被試験メモリのアドレスに対応付けてフェイルデータを記憶する不良解析メモリ部と、論理比較器から出力されたフェイルデータをカウントし、カウント値が予め設定された上限フェイル値を超えた場合に、論理比較器から不良解析メモリ部へと供給されるフェイルデータをマスクするマスク部と、を備える試験装置を提供する。

(もっと読む)

半導体記憶装置

【課題】2個の隣接する列ブロックのいずれにも欠陥がある場合でも、これらの列ブロックの救済が可能な半導体記憶装置を提供する。

【解決手段】データ線シフト回路58は、偶数番目の正規ブロックに欠陥がある場合に、偶数番目の正規ブロックおよび偶数番目のスペアブロックを対象としたシフトリダンダンシ方式によって、偶数番目の内部正規データ線NIOXおよび偶数番目の内部スペアデータ線SIOXと偶数番目の外部データ線EIOXとの接続を行ない、奇数番目の正規ブロックに欠陥がある場合に、奇数番目の正規ブロックおよび奇数番目のスペアブロックを対象としたシフトリダンダンシ方式によって、奇数番目の内部正規データ線NIOXおよび奇数番目の内部スペアデータ線SIOXと奇数番目の外部データ線EIOXとの接続を行なう。

(もっと読む)

半導体装置

【課題】分割セルアレイのビット線対の長さを、冗長ワード線を含む、含まないに関係なく、分割セルアレイ間で同じ長さにする事を簡単にできるようにする。

【解決手段】第1及び第2のセルアレイと、前記第1のセルアレイ内を延在され前記第1のセルアレイ内の複数のセルに接続する第1のデータ線と、前記第2のセルアレイ内を延在され前記第2のセルアレイ内の複数のセルに接続する第2のデータ線とに接続され、前記第1及び第2のセルアレイの間に配置された第1のアンプと、アドレス信号をデコードし前記第1のセルアレイの第1ワード線群の選択を行う第1のデコーダと、前記アドレス信号をデコードし前記第2のセルアレイの第2ワード線群の選択を行う第2のデコーダを備え、前記第1及び第2のデコーダの内部の所定ノードをワイヤードオアした結果を出力する回路を備える。

(もっと読む)

半導体装置

【課題】選択ビット線のYスイッチと非選択のビット線のYスイッチがともに選択されるマルチ選択状態に陥ることを回避する。

【解決手段】ゲート電極の電位に従ってビット線とIO線とを電位的に接続するYスイッチと、Yスイッチ制御信号を前記Yスイッチのゲート電極に供給するビアと、Yスイッチのゲート電極に接続し、信号(1)に対応して前記ゲート電極をGND電位に設定しYスイッチを電気的に非導通とする制御を行うトランジスタ(N1)と、ビット線をプリチャージ電圧にプリチャージ・イコライズする回路(P1〜P3)と、を備え、Yスイッチのゲート電極をGND電位に設定するプリチャージ信号の活性化は、イコライズ回路の活性化のタイミングに対応している。

(もっと読む)

半導体装置およびテスト方法

【課題】不良となり得るビット線対のテスト結果に、潜在的な不良を有する可能性を反映する半導体装置のテスト方法および半導体装置を提供する。

【解決手段】複数のワード線と複数のビット線との交点にそれぞれ配置された複数のメモリセルを有する第1および第2のメモリセルマットと、第1のメモリセルマット内のビット線と第2のメモリセルマット内のビット線とからなるビット線対の電位差を増幅するセンスアンプと、を備える半導体装置は、ビット線対に配置された複数のメモリセルが不良か否かのテストをメモリセルごとに順番に行う判定回路と、テストが行われるごとにテスト結果を受け付け、不良を示すテスト結果の数をカウントするカウンタ回路と、カウントされた数が所定数以上になると、カウントされた数が所定数になった以降に行われるテスト結果を全て不良として出力するテスト出力回路と、を含む。

(もっと読む)

不揮発性メモリコントローラ及び不揮発性記憶装置

【課題】不良ブロックが発生しても、新たなデータの書き込みが可能な不揮発性メモリコントローラ及び不揮発性記憶装置を提供する。

【解決手段】コントローラ102は、ホスト機器200からの論理アドレスに基づいて物理ブロックに対するデータの書き込み及び/又は読み出しを制御する制御部108と、有効論理アドレス範囲内の1箇所以上の部分領域を論理不良クラスタとし、当該論理不良クラスタの論理アドレスの情報を格納する論理不良クラスタテーブル112と、物理ブロックに格納されるデータの、有効論理アドレス範囲の論理アドレスと物理ブロックの物理アドレスとの対応情報を格納するアドレス変換テーブル109とを備え、制御部108は、論理不良クラスタテーブル112に格納された論理アドレスに対するホスト機器200からのデータの書き込み命令を受けた場合、当該論理アドレスに対するデータの前記物理ブロックへの書き込みの反映を不可とする。

(もっと読む)

半導体記憶装置

【課題】不良メモリセルに関する情報をメモリセルアレイの記憶容量を割いて記憶させなくても、不良メモリセルを非選択とすることが可能な半導体記憶装置を提供することを課題とする。

【解決手段】駆動回路に不良メモリセルに関する情報を記憶した冗長制御機能を設け、メモリセルアレイの欠陥を救済する。すなわち、データを記憶させるために設けられたメモリセルアレイの一部を使って不良メモリセルのアドレス情報を記憶させるのではなく、メモリコントローラの中に不良メモリセルのアドレス情報を記憶させる不揮発性のメモリを設ける。不良メモリセルのアドレス情報を保持するメモリコントローラは、不良メモリセルのアドレス情報を取得するために、わざわざメモリセルアレイまでアクセスしないで済み、処理速度の向上に寄与することになる。

(もっと読む)

不揮発性半導体記憶装置、及び不揮発性半導体記憶装置の制御方法

【課題】不良メモリセルを効率的に判定して管理できる不揮発性半導体記憶装置及び不揮発性半導体記憶装置の制御方法を提供する。

【解決手段】不揮発性半導体記憶装置は、抵抗変化素子と整流素子とが直列にそれぞれ接続された複数の不揮発性メモリセルが配列されたメモリセルアレイと、順方向となる第1のバイアスを不揮発性メモリセルの両端に印加した後に逆方向となる第2のバイアスを前記不揮発性メモリセルの両端に印加する一連の動作を行い、前記複数の不揮発性メモリセルのうち、データ保持特性が基準に満たない不揮発性メモリセルを不良メモリセルとして判定する制御回路と、前記制御回路により判定された前記不良メモリセルのアドレスを記憶する記憶部と、前記記憶部に記憶された前記不良メモリセルのアドレスを避けて前記メモリセルアレイ内の不揮発性メモリセルにデータを記憶するように制御するアドレス制御部とを備えている。

(もっと読む)

インターフェース回路、パリティビット割付方法及び半導体記憶装置

【課題】メモリセルアレイ中のパリティビットセルに不良セルがあってもパリティビットを含むデータを記憶することができるインターフェース回路、パリティビット割付方法及び半導体記憶装置を提供する。

【解決手段】コアロジック2と半導体メモリ3との間に、割付回路1cを設けた。割付回路1cには、各ビット線について、ビット線上のメモリセルに不良メモリセルが形成されたビット線か否かを示すビット線選択情報SLに基づいて、ライトデータWD中のパリティビットD9〜D12を、不良メモリセルが形成されていない正常なメモリセルが形成されているビット線に出力する書込回路部10を設けた。

(もっと読む)

不揮発性半導体記憶装置

【課題】ECC動作を消去モードの最初に行うことで、高速読み出し動作可能な不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置10は、データ格納用の不揮発性メモリセルが配列されたメモリ領域(メイン消去ブロック110−2〜110−n)と、メモリ領域が不良領域である場合にメモリ領域と置換される冗長領域(冗長用消去ブロック110−1)と、消去動作を示すコマンドが入力されると、消去動作に先立って前記メモリ領域からデータを読み出し、誤り検出を行い、誤り検出結果に基づいて前記冗長領域へと置換する前記不良領域を検出する制御部(制御部12)と、を備える。

(もっと読む)

1 - 20 / 75

[ Back to top ]