Fターム[5L106GG03]の内容

半導体メモリの信頼性技術 (9,959) | 改良手段 (1,147) | タイミング (177)

Fターム[5L106GG03]に分類される特許

1 - 20 / 177

半導体装置

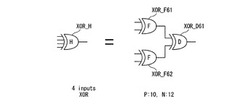

【課題】動作速度と駆動能力とのバランスが調整された多入力論理回路を備えた半導体装置を提供する。

【解決手段】3入力以上の入力端子を含み当該3入力以上の入力端子の論理レベルについて論理演算を行う多入力論理回路(XOR_H)を備え、当該多入力論理回路は、それぞれ2つの入力端子を含み当該2つの入力端子の論理レベルに対して前記論理演算を行う複数の2入力論理回路を含み、当該複数の2入力論理回路は、第1の2入力論理回路(XOR_D61)と当該第1の2入力論理回路よりも占有面積が小さく駆動能力が小さい第2の2入力論理回路(XOR_F61、XOR_F62)とを含み、前記第1の2入力論理回路が前記多入力論理回路の最終段として動作し、前記第2の2入力論理回路が前記第1の2入力論理回路に信号を供給する前段回路の少なくとも一部として動作することを特徴とする。

(もっと読む)

半導体装置

【課題】CRC機能を有し、ライト動作とリード動作を高速に行うことができる半導体装置を提供する。

【解決手段】メモリセルアレイ(メモリセルアレイ11)と、巡回冗長論理符号を生成する誤り検出符号生成回路(誤り検出符号生成回路20)と、メモリセルアレイから読み出されたデータに巡回冗長論理符号を付加してデータ入出力端子を介して半導体装置の外部へリードデータとして出力し、或いは半導体装置の外部からライトデータが入力されて、前記メモリセルアレイへ書き込むデータを誤り検出符号生成回路に出力するデータ入出力部(データ入出力部19)と、メモリセルアレイとデータ入出力部との間に配置されるバス配線(リードライトバス)と、誤り検出符号生成回路とデータ入出力部との間に配置される巡回冗長論理符号配線(CRC信号線)と、を備える。

(もっと読む)

半導体記憶装置

【課題】マーチパターンテストではアドレスデコーダの配線の遅延を検知できない。

【解決手段】半導体記憶装置のアドレスデコーダは,アドレスサイクルの第1のタイミングで,複数の入力アドレス信号それぞれの非反転及び反転論理レベルを有する第1と第2の内部アドレス信号を出力するアドレスレジスタと,複数の入力アドレス信号の第1と第2の内部アドレス信号を伝播する複数の内部アドレス信号線を有する内部アドレス信号線網と,アドレスレジスタと内部アドレス信号線網の間に設けられ,アドレスレジスタが出力した第1と第2の内部アドレス信号を,アドレスサイクルの第1のタイミング後の第2のタイミングで一定の論理レベルにリセットするリセット回路と,内部アドレス信号線網を介して複数の入力アドレス信号の第1と第2の内部アドレス信号の組合せを供給され,当該組合せを論理演算してそれぞれのワード線又はビット線を選択する複数のアドレスデコード回路とを有する。

(もっと読む)

半導体装置及びそのテスト方法

【課題】ディスターブ試験時のノイズを低減しサイクル高速化を実現する技術を提供する。

【解決手段】本発明による半導体装置は、ワード線及びビット線に接続された複数のメモリセルを含み、複数のバンクに分割されたメモリセルアレイと、テスト動作時に、テスト回路用アドレス信号とディスターブ試験用テスト信号を用いて、バンク毎にワード線を内部アドレス信号に応じて別々のタイミングで選択するロウ周辺回路とを備える。

(もっと読む)

メモリ装置およびメモリ装置の制御方法

【課題】メモリセル31が劣化した場合にも、誤り訂正回路20の回路面積を増大させることなく誤り訂正を行うことができるメモリ装置2を提供する。

【解決手段】実施の形態のメモリ装置2は、メモリ部30と、制御部11と、補正部41と、誤り検出訂正部40とを具備する。メモリ部30は、データを記憶する複数のメモリセル31からなる。制御部11は、電荷量に対応した閾値電圧を読み出すためにメモリセル31にHB読出電圧HVと、補間読出電圧AVと、を印加する制御を行う。補正部41は読み出された、閾値電圧Vthから決定されたビットデータを反転する。誤り検出訂正部40は、補正部41で反転されたビットデータを含めた所定長のデータ列を、硬判定復号符号により復号処理を行う。

(もっと読む)

半導体装置

【課題】誤ってテストモードにエントリされたとしても、正常に動作させる。

【解決手段】半導体装置は、内部回路をテストするテスト回路2に対してテストを開始させるテストモードエントリ信号が入力されたことに応じて、内部のラッチ10をセットすることにより、テスト回路2に対し、テスト回路2の駆動を許可するテストイネーブル信号をラッチ10から出力するテスト信号発生回路1を備える。テスト信号発生回路1が、ラッチ10がテストイネーブル信号を出力している場合、テストイネーブル信号を遅延させて、ラッチ10をリセットするリセット信号を生成するリセット信号生成回路30と、ラッチ10がテストイネーブル信号を出力している場合に、外部から供給されるトグル信号に基づいて、リセット信号生成回路30によるリセット信号を生成する動作を初期化する遅延初期化信号を出力する遅延初期化回路40と、を有している。

(もっと読む)

半導体装置

【課題】アドレス比較回路に入力される判定信号の期間であって、アドレス比較回路が誤判定を起さない期間、を評価工程において求めることができる半導体装置を提供する。

【解決手段】供給されるヒューズ判定信号(ヒューズ判定信号RRFDETA)が活性レベルの場合に、入力されるアドレスがヒューズに記憶したアドレスと一致するか否かを判定するアドレス比較回路(FUSE判定回路20)と、外部から半導体装置に供給される外部クロックのレベルの遷移に応じて、前記ヒューズ判定信号の活性レベル及び非活性レベルを制御するヒューズ制御回路(FUSE制御回路18a)と、を備えることを特徴とする。

(もっと読む)

半導体記憶装置およびそのテスト手法

【課題】短時間でライト動作不良をテストすることができる、半導体記憶装置、及びそのテスト方法を提供すること。

【解決手段】非テスト対象ポートに対応するワード線を活性化させ、非テスト対象ポートに対応するプリチャージ信号を非活性にすることにより、非テスト対象ポートに対応する前記ディジット線対の一方を放電させる。放電後の前記ディジット線対の電位差が保たれた状態で、複数のワード線を活性化させ、テスト対象ポートに対応するディジット線対を駆動することにより、メモリセルにテストデータを書き込む。その後、メモリセルからデータを読み出し、テストデータが正しく書き込まれていたか否かを判定する。

(もっと読む)

メモリインターフェース回路

【課題】DLLの遅延値を補償するテストができるメモリインターフェース回路を供給する。

【解決手段】メモリインターフェース回路のテストシステムを以下のように構成する。クロック信号(CK)の周期を遁倍した遁倍クロック(CKx2、CKx4)を生成する遁倍クロック生成PLL回路(2、14)と、遁倍クロック(CKx2、CKx4)によりDQS信号の出力タイミングを選択して出力する選択回路(5、13)と、DQS信号のリード回路側に配置され、オフセット設定機能を有するDLL回路(4)と、テストパタンデータを自己で生成するパターン発生回路(3)と、テストパタンデータとDQ信号とが一致しているか否かを判定する一致判定回路(9)と、DQ信号を1データ遅れで受け取ったときに、DQ信号とテストパタンデータとが一致していると判定する1データ遅れ一致判定回路(10)とを有するように構成する。

(もっと読む)

半導体装置

【課題】ウェハレベルバーンインテスト時におけるクロックツリー配線のNBTI劣化を防止する。

【解決手段】通常動作時においては内部クロック信号DLLCLKを生成し、ウェハレベルバーンインテスト時においては内部クロック信号DLLCLKの生成を停止するディレイライン24aと、内部クロック信号LCLKを伝送するクロックツリー配線25と、ウェハレベルバーンインテスト時において、セルフリフレッシュタイミング信号SLFをダミークロック信号としてクロックツリー配線25に供給するセレクタ51,24bとを備える。本発明によれば、ウェハレベルバーンインテスト時においてダミークロック信号を供給していることから、ウェハレベルバーンインテストによるクロックツリー配線のNBTI劣化を防止することが可能となる。

(もっと読む)

試験装置および試験方法

【課題】精度良く被試験デバイスを試験する。

【解決手段】データ信号とクロック信号とを授受する被試験デバイスを試験する試験装置であって、被試験デバイスにデータ信号およびクロック信号を試験信号として供給する試験信号供給部と、被試験デバイスが出力するデータ信号を、被試験デバイスが出力するクロック信号に応じたタイミングで取得するデータ取得部と、データ取得部が取得したデータ信号を期待値と比較した比較結果に基づいて被試験デバイスの良否を判定する判定部と、調整時において、データ信号を取得するタイミングを生成するためのクロック信号の遅延量を調整する調整部とを備える試験装置を提供する。

(もっと読む)

情報処理装置、情報処理装置の制御方法、および、プログラム

【課題】経年変化に起因して生じず誤りの誤り訂正を行う。

【解決手段】本発明の情報処理装置は、データを格納する複数のブロックからなり、前記複数のブロックの各々に対するデータの再書込みが可能な記憶部と、前記複数のブロックの各々について、該ブロックに格納されているデータの誤り検出を定期的に行い、誤りを検出すると、該検出した誤りの誤り訂正を行い、誤り訂正後のデータの前記ブロックに対する再書込みを行う処理部と、を有する。

(もっと読む)

半導体試験装置及びそのテスト方法

【課題】メモリのテスト時の消費電流を抑え、メモリテスト時の周波数を高速化する。

【解決手段】制御回路103は、第1及び第2のテストパタンジェネレータ104、105によるテストがともにライトの場合、一方のテストパタンジェネレータによるテストシーケンスの実行を許可し、他方のテストパタンジェネレータに対してテストシーケンスの実行を不許可とし、一方のテストパタンジェネレータからメモリグループ101、102の対応する一方のグループに対してライトのテストパタンを出力し、他方のグループに対するライトの実行を、一方のグループのライトのテストサイクル単位で時間的にずらし、一方のテストパタンジェネレータによる一方のグループのライトの終了後、他方のテストパタンジェネレータによるテストシーケンスの実行を許可し、他方のテストパタンジェネレータから対応する他方のグループに対するライトのテストパタンを出力する。

(もっと読む)

半導体装置

【課題】従来は、外部機器側で情報の書き込みが正常に成されたか否かを判断していた。また、半導体装置ないに大掛かりな回路を構成しなければ、正しく書き込みを判断できなかった。

【解決手段】外部機器から入力される書込パルスのうち、そのパルス長で、搭載する不揮発性記憶手段に情報が正しく書き込まれたか否かの判定を行なう判断手段を設けた。判断手段は、書込パルスのパルス長が所定の範囲にあるか否かや、書込パルスの到来と同時に時間を計測する計時手段などを用いることで、パルス長が正しいか否かを判定する。これにより、簡便な構成で、正しい情報の書き込みを判断できる。

(もっと読む)

半導体装置及び半導体装置の制御方法

【課題】tRP期間の性能限界試験を実行可能な半導体装置及びその制御方法を提供する。

【解決手段】コマンドデコーダ16は、デバイスのアクティブ動作を認識し保持する第1の取り込み部、第1の取り込み部が出力する第1の出力信号を後段の回路(制御回路18)に出力する第1の出力部、デバイスのインアクティブ動作を認識し保持する第2の取り込み部、第2の取り込み部が出力する第2の出力信号を後段の回路に出力する第2の出力部を含む。第1及び第2の取り込み部は、同期信号(クロック信号CLK)の第1の遷移エッジに対応してCommandを取り込み且つ保持し第1の出力部は、第1の遷移エッジに対応して第1の出力信号(inACT)を出力する。第2の出力部は、テストモード信号が第2の論理であるテストモード動作時に、第1の遷移エッジと逆の遷移エッジである同期信号の第2の遷移エッジに対応して第2の出力信号(inPRE)を出力する。

(もっと読む)

集積回路装置および集積回路装置の試験方法

【課題】メモリへの連続アクセス回数を増やしても使用するスキャンチェーン数を増加させることなく試験を行うことができる集積回路装置の提供を図る。

【解決手段】メモリMEMと、該メモリに接続される複数のロジック回路Lと、前記メモリおよび前記ロジック回路の試験を行うスキャンチェーンSCI,SCIIと、を含む集積回路装置であって、前記メモリの前段の第1スキャンチェーンSCIにおいて、前記メモリに対して出力端子が繋がっている少なくとも2つの第1および第2フリップフロップFF107,FF108を有し、前記第2フリップフロップFF108の前記出力端子と、前記第1フリップフロップFF107のスキャン入力端子の間に、少なくとも1つの第1挿入フリップフロップFF105,FF101を挿入して、前記スキャンチェーンの接続を規定する。

(もっと読む)

半導体装置

【課題】低周波数のクロックしか供給できないバーンインテスタを用いた場合であっても、テストに長時間を要するディスターブテストを、高周波数で実行可能な半導体装置を提供する。

【解決手段】テスト動作モードにおいて、ロウアドレスバッファ部12dにより、第1のワード線の位置を示すロウアドレスを取り込む。制御回路18a及びタイミング制御回路18bは、第1のワード線とビット線対を共有する第1のワード線とは異なる第2のワード線を選択し、当該ワード線に接続されるメモリセルのリフレッシュ動作を、外部から供給されるクロック信号の第1の周波数に比べて高い第2の周波数で実行する、ことを特徴とする。

(もっと読む)

半導体集積回路及び半導体集積回路のテスト方法

【課題】内部に備えられた順序回路の動作検証にかかる時間を短縮できる半導体集積回路を提供すること

【解決手段】半導体集積回路1は、入力信号3が論理回路4を通過した信号である通過信号が供給されるD型F/F10を備える。遅延量測定回路6は、論理回路4により生じる入力信号3の遅延量を、D型F/F10の動作検証前に測定する。遅延制御回路5は、D型F/F10の動作検証の際に、入力信号3を遅延量測定回路6が測定した遅延量だけ遅延させた遅延信号を生成する。比較回路11は、D型F/F10の動作検証の際に、遅延制御回路5が生成した遅延信号をD型F/F10の入力とした場合のD型F/F10からの出力と、期待値と、を比較してD型F/F10の動作検証を行う。

(もっと読む)

半導体記憶装置

【課題】 各種のデータ転送が可能な半導体記憶装置を提供する。

【解決手段】 メモリセルアレイ10は、複数の不揮発性メモリセルが配置されている。RAM(Random Access Memory)30は、メモリセルアレイ10に書き込まれるデータ、又は読み出されたデータを保持する。制御部4は、RAMを用いた第1の動作モードと、RAMを用いない第2の動作モードを制御する。データ転送部17は、第2の動作モードにおいて、データの書き込み時、データバスDIRを介して入出力部40から供給されたデータをバッファ部12に転送し、バッファ部12に転送されたデータをエラー訂正部20に転送し、エラー訂正部20において、生成されたパリティデータをバッファ部12に転送する。

(もっと読む)

半導体記憶装置

【課題】セットアップ及びホールド時間のマージンを確保する。

【解決手段】半導体記憶装置1は、第1のクロックを受け、かつデータの入出力を行う第1のバッファ12を有する第1のメモリ10と、データの入出力を行う第2のバッファ22を有する第2のメモリ20とを含む。第1のメモリ10は、第1のクロックを用いて第2のメモリ20に第2のクロックを転送する。第1のバッファ12は、第1のクロックに応答して第2のメモリ20にデータを転送する。第2のバッファ22は、第2のクロックに応答してデータを受ける。

(もっと読む)

1 - 20 / 177

[ Back to top ]