Fターム[5M024AA22]の内容

Fターム[5M024AA22]に分類される特許

1 - 20 / 159

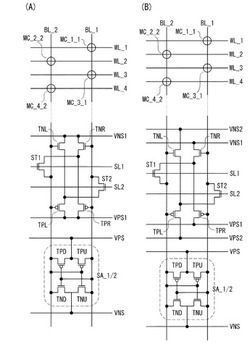

半導体メモリ装置およびその駆動方法

【課題】従来のDRAMでは微細化と共にデータの読み出しエラーが発生しやすくなる。

【解決手段】第1のビット線BL_1の微弱な電位の変動はNチャネル型トランジスタTNRとPチャネル型トランジスタTPRで構成される第1のインバータで反転され、第1のスイッチである第1の選択トランジスタST1を介して、第2のビット線BL_2に出力される。第2のビット線BL_2の電位は、第1のビット線BL_1の電位とは反転した電位であるため、第1のビット線BL_1と第2のビット線BL_2の電位差は拡大する。この拡大した電位差を公知のセンスアンプSA_1/2あるいは、第2のインバータ(Nチャネル型トランジスタTNLとPチャネル型トランジスタTPLで構成される)と第1のインバータで構成されるフリップフロップ回路等で増幅する。

(もっと読む)

セルフリフレッシュパルス生成回路

【課題】セルフリフレッシュモード入り後初期期間に周期が制御されたセルフリフレッシュパルスを生成することにより、リフレッシュフェイルを防止することが可能なセルフリフレッシュパルス生成回路を提供する。

【解決手段】セルフリフレッシュパルス生成回路は、セルフリフレッシュモード入り後初期期間の終了時点でレベルが遷移する制御信号を生成する制御信号生成部と、前記セルフリフレッシュモードにおいて、前記制御信号に応答して、周期が制御されたセルフリフレッシュパルスを生成するセルフリフレッシュパルス生成部とを備える。

(もっと読む)

メモリにおけるピーク電力管理のためのメカニズム

【課題】メモリにおけるピーク消費電力管理のためのメカニズムを提供する。

【解決手段】サブ・アレイ・ブロックを含むメモリ・ストレージ・アレイにおけるピーク電力を管理するためのメカニズムが、サブ・アレイ・ブロックの各々に対するワードライン信号の起動を互い違いにすることにより、読み出し動作及び書き込み動作と関連したピーク電流を削減することができる。具体的には、1つのサブ・アレイ・ブロックの読み出しワードライン信号が、別のサブ・アレイ・ブロックの書き込みワードライン信号と同時に1つの論理レベルから別の論理レベルに遷移しないように、各々のサブ・アレイ・ブロックに対してワードライン信号を生成することができる。さらに、ワードライン・ユニットは、所与のサブ・アレイ・ブロックの読み出しワードライン信号が、別のサブ・アレイ・ブロックの読み出しワードライン信号と同時に1つの論理レベルから別の論理レベルに遷移しないように、ワードライン信号を生成することができる。

(もっと読む)

半導体記憶装置

【課題】オープンビット線方式における電源ノイズの影響を低減した半導体記憶装置を提供する。

【解決手段】半導体記憶装置は,列方向に両側に延びる一対のビット線に接続するセンスアンプを列方向に直交する行方向に複数配置したセンスアンプ群が列方向に複数配置され,列方向に隣接するセンスアンプ群それぞれに接続される複数のビット線が互いに平行に配置され,列方向の両端に配置されたセンスアンプ群に接続された一対のビット線のうち列方向の両端側の複数のビット線にそれぞれ平行に配置された複数の未使用ビット線を有し,複数のワード線が行方向に配線され,複数のビット線及び複数の未使用ビット線と複数のワード線との交差位置にメモリセルが配置されたメモリセルアレイと,メモリセルアレイの列方向の一端に配置され,複数のセンスアンプ群に内部電源を内部電源線を介して供給する内部電源回路とを有し,未使用ビット線は内部電源配線に接続されている。

(もっと読む)

半導体記憶装置及びそのリフレッシュ制御方法

【課題】アクセス頻度が高いプレートのリフレッシュ動作頻度を上げる技術を提供する。

【解決手段】半導体装置において、プレートへのアクセス頻度を検出し、アクセス頻度が所定の閾値を超えたときに活性信号を出力するディスターブカウンタ回路と、オートリフレッシュコマンド時に活性信号を検出すると、アクセス頻度が所定の閾値以上のプレートについてのリフレッシュ割り込み信号を出力するリフレッシュカウンタ回路とを提供する。

(もっと読む)

半導体装置

【課題】ワード線の負荷を増大させることなく、ワード線に生じるノイズを低減する。

【解決手段】少なくとも一のスイッチング素子を有する複数の記憶素子がマトリクス状に配置され、前記記憶素子のそれぞれにはワード線とビット線がそれぞれ接続され、前記ワード線には少数キャリアが実質的に存在しないトランジスタのゲート(またはソース及びドレイン)が接続され、前記少数キャリアが実質的に存在しないトランジスタのソース及びドレイン(またはゲート)の電位が制御されることで前記少数キャリアが実質的に存在しないトランジスタの容量値の制御を行う半導体装置とする。前記少数キャリアが実質的に存在しないトランジスタは、ワイドギャップ半導体により設けられていればよい。

(もっと読む)

半導体装置及びシステム

【課題】互いに独立に動作する複数の記憶領域に対するリフレッシュ動作の起動タイミングが重ならないように制御可能な半導体装置及びシステムを提供する。

【解決手段】本発明は、互いに独立に動作する複数の記憶領域と、これらの記憶領域の動作をそれぞれ独立に制御する複数の制御回路と、リフレッシュ起動制御回路40とを備えている。リフレッシュ起動制御回路40は、オシレータ信号N0を出力するオシレータ41と、オシレータ信号N0に基づいて活性化タイミングが互いに異なる複数のリフレッシュ起動信号RSを生成するリフレッシュ起動信号生成回路42(2分周回路50〜52及びデコーダ53)とを備え、リフレッシュ要求を受けた制御回路に対応する記憶領域が、対応するリフレッシュ起動信号RSの各活性化タイミングに応答してリフレッシュされる。

(もっと読む)

記憶装置及び電子機器

【課題】メモリセル毎に選択動作を行う。

【解決手段】装置は、第1のメモリセルと、第1のメモリセルと同じ行に設けられた第2のメモリセルと、を具備し、前記第1及び第2のメモリセルのそれぞれは、第1のゲート及び第2のゲートを有し、オン状態又はオフ状態になることにより、メモリセルにおける少なくともデータの書き込み及びデータの保持を制御する電界効果トランジスタを備え、前記第1のメモリセル及び前記第2のメモリセルが備える前記電界効果トランジスタの前記第1のゲートのそれぞれに電気的に接続される行選択線と、前記第1のメモリセルが備える前記電界効果トランジスタの前記第2のゲートに電気的に接続される第1の列選択線と、前記第2のメモリセルが備える前記電界効果トランジスタの前記第2のゲートに電気的に接続される第2の列選択線と、をさらに具備する。

(もっと読む)

半導体装置

【課題】ワード線非活性化における情報破壊を防止する半導体装置を提供すること。

【解決手段】半導体装置は、ワード線及びビット線を含むメモリセルマットと、サブワードドライバ回路と、サブワードドライバ回路を制御する第1制御部と、を有するメモリセルアレイを備える。第2制御部は、第1電源電位を低電位側とする第1電源電圧で動作する第3回路部と、第1電源電位よりも低い第2電源電位を低電位側とする第2電源電圧で動作する第4回路部と、を含む。第2制御部は、サブワードドライバ回路に第1制御信号を供給し、第1制御部に第2制御信号を供給する。第1制御部は、第1電源電位を受け取らずに第2電源電位を低電位側とする第3電源電圧で動作し、第2制御信号を受け取り第3制御信号をサブワードドライバ回路に供給する。サブワードドライバ回路は、第1制御信号と第3制御信号とを受け取り、活性状態のワード線を非線形に非活性状態とする。

(もっと読む)

半導体装置

【課題】ダミーセルを設けたメモリセルアレイのセンスマージンの向上とビット線ノイズの低減が可能な半導体装置を提供する。

【解決手段】相補対をなすビット線BL、/BL、同じ構造のメモリセルMCL、MCR及びダミーセルDCL、DCR、差動型のセンスアンプSA、ビット線BL、/BLをイコライズするイコライズ回路(Q1)を備え、ビット線イコライズ期間に、メモリセルMCL、MCRをビット線BL、/BLから切り離しダミーセルDCL、DCRをビット線BL、/BLに接続した状態でイコライズ回路でビット線BL、/BLをイコライズし、メモリセルMCLへのアクセス時に、イコライズ回路を非活性にし、ダミーセルDCLをビット線BLから切り離し、メモリセルMCLをビット線BLに接続し、センスアンプSAを活性化する。よって、ビット線BL、/BLの容量バランスを確保し、センスマージンの向上とビット線ノイズの低減を実現できる。

(もっと読む)

半導体メモリおよび半導体メモリの動作方法

【課題】 センスアンプの動作マージンの低下を防止する。

【解決手段】 各メモリブロックは、複数のメモリセルと、メモリセルにそれぞれ接続される複数のワード線とを有している。リフレッシュアドレスカウンタは、第1リフレッシュアドレス信号をリフレッシュ要求信号に応じて生成する。メモリブロックにそれぞれ対応するアドレス変換部は、第1リフレッシュアドレス信号に基づいてメモリブロック毎に値が異なる第2リフレッシュアドレス信号をそれぞれ生成するとともに、第2リフレッシュアドレス信号の値の組み合わせパターンを所定数のリフレッシュ動作毎に変更する。これにより、センスアンプで増幅されるデータのパターンを所定の頻度で変えることができ、センスアンプの動作マージンの低下を防止できる。

(もっと読む)

メモリインターフェース回路、メモリインターフェース方法、および電子機器

【課題】回路規模を抑え、複雑な制御を必要とせずに、データストローブ信号がハイインピーダンス状態にある場合に内部にリードデータ信号の誤取り込みを防止して、安定的にメモリからデータを読み出すことが可能なメモリインターフェース回路を提供すること。

【解決手段】DQS信号が伝播するDQS線DQSLをローレベルにクランプするクランプ回路11と、リードイネーブル信号RENに応じて、DQS線DQSLを介して入力されるDQS信号の論理レベルの検出を開始するアンド回路10とを備え、クランプ回路11を設けることにより、読み出し動作において、DQS線DQSLは接地電位にクランプされる。よって、DQS線DQSLがハイインピーダンス状態に維持されることはなく、ノイズ等によりDQS線DQSLに生じる不測のエッジを検出することはない。DQS信号を誤検出することはなく、誤ったDQ信号を取り込む恐れがない。

(もっと読む)

半導体記憶装置

【課題】リフレッシュを必要とするメモリを有する半導体記憶装置において、リフレッシュ動作に起因した電源ノイズの周波数成分による回路動作への影響を低減する。

【解決手段】リフレッシュ信号CIN1はリフレッシュ周期またはその整数分の1の周期を持つパルス信号である。信号変換回路2はリフレッシュ信号CIN1を、リフレッシュサイクル毎に1個のパルスを有し、かつ、周期が不定であるリフレッシュ実行信号COUTに変換し出力する。リフレッシュ制御回路3は、リフレッシュ実行信号COUTに従って、メモリセルアレイ4のリフレッシュを実行する。

(もっと読む)

半導体装置

【課題】出力バッファにおいて発生したノイズが、他の出力バッファに伝搬することを防止し、且つ各出力バッファに安定した電源供給を行うことが可能な半導体装置を提供する。

【解決手段】外部電圧が供給される複数の電源パッド111,112と、複数のデータ出力パッド113,114と、複数の電源パッド111,112に共通接続された電源幹線411,412と、電源幹線から分岐した複数の分岐電源配線411B,412Bと、それぞれ対応する分岐電源配線411B,412Bから供給される電源電圧によって動作し、それぞれ対応するデータ出力パッド113,114を駆動する複数の出力バッファ72と、複数の分岐電源配線411B,412Bにそれぞれ設けられたローパスフィルタ回路1000とを備える。

(もっと読む)

半導体装置及びその制御方法

【課題】内部電圧生成回路が発生するノイズがセンシティブな回路ブロックに与える影響を低減する。

【解決手段】電源ラインVLに内部電圧V0を供給する内部電圧生成回路1,2を複数個並列に接続し、付加回路3に含まれる複数の回路ブロックのうち、ノイズの影響を受けやすい回路ブロックが動作中ではない場合は、内部電圧V0の低下に応答して全ての内部電圧生成回路1,2を活性化させ、ノイズの影響を受けやすい回路ブロックが動作中である場合は、内部電圧V0が低下しても内部電圧生成回路2のみを活性化させ、内部電圧生成回路1を活性化させない。これにより、内部電圧生成回路の動作に伴う負荷回路3へのノイズの影響を低減させる。

(もっと読む)

半導体メモリ装置およびその駆動方法

【課題】従来のDRAMでは容量素子の容量を減らすと、データの読み出しエラーが発生しやすくなる。

【解決手段】1つのビット線MBL_mに複数個のセルを接続させる。各セルはサブビット線SBL_n_mと4乃至64個のメモリセル(CL_n_m_1、等)を有する。さらに各セルは選択トランジスタSTr1_n_mとSTr2_n_mを有し、また、選択トランジスタSTr2_n_mには相補型インバータ等の増幅回路AMP_n_mを接続する。サブビット線SBL_n_mの寄生容量は十分に小さいため、各メモリセルの容量素子の電荷による電位変動を増幅回路AMP_n_mでエラーなく増幅でき、ビット線に出力できる。

(もっと読む)

半導体装置

【課題】ポイントシフト型FIFO回路の制御に必要な信号配線の本数を削減する。

【解決手段】入力ノードNI0〜NImが入力選択回路1に接続され、出力ノードNO0〜NOmが出力選択回路2に接続されたラッチ回路L0〜Lmと、入力選択回路1及び出力選択回路2を制御する制御回路6とを備える。制御回路6は、入力ポインタ信号IPを生成するシフトレジスタ6aと、出力ポインタ信号OPを生成するバイナリカウンタ6bを含む。入力選択回路1は、入力ポインタ信号IPの値に基づいていずれかのラッチ回路を選択し、出力選択回路2は、出力ポインタ信号OPの値に基づいていずれかのラッチ回路を選択する。これにより、入力選択回路1におけるハザードの発生を防止しつつ、出力ポインタ信号OPを伝送する信号配線の本数を削減することが可能となる。

(もっと読む)

半導体装置及びこれを備える情報処理システム

【課題】並列接続された複数の入力回路のうち使用する入力回路を切り替える際に生じる出力ノードの信号ノイズ(ハザード)を防止する。

【解決手段】それぞれが、入力信号INが供給される一つの入力ノードN10に接続し、出力信号OUTを供給する一つの内部出力ノードN11に接続し、互いに電気的特性が異なる第1及び第2の入力回路100A,100Bと、切り替え信号SELを生成し、切り替え信号SELによって、入力回路100A,100Bを制御する入力制御回路300とを備える。入力制御回路300は、入力回路100A,100Bのいずれか一方を活性から非活性へ、いずれか他方を非活性から活性へ切り替えるとき、入力回路100A,100Bが同時に活性状態となる時間を含むように制御する。これにより、入力回路100A,100Bの切り替えに伴う信号ノイズ(ハザード)の発生が防止される。

(もっと読む)

半導体装置

【課題】出力バッファを制御する制御回路部において発生する電源ノイズを低減する。

【解決手段】データ出力端子14を駆動する単位バッファ501〜507と、単位バッファ501〜507を制御するインピーダンス制御回路511〜513と、インピーダンス制御回路511〜513を制御する制御回路部400とを備える。インピーダンス制御回路511〜513と制御回路部400は互いに異なる電源によって動作し、制御回路部400は、互いに逆相であるプルアップデータ及びプルダウンデータをインピーダンス制御回路511〜513に供給し、インピーダンス制御回路511〜513は、逆相であるプルアップデータ及びプルダウンデータを同相に変換して単位バッファ501〜507に供給する。これにより、制御回路部400にて使用する電源VDDにノイズが生じにくくなる。

(もっと読む)

半導体装置及びその制御方法

【課題】電流量制御信号OVDRの非活性化を開始した直後の第2の電圧V2のオーバーシュート又はアンダーシュートを抑制する。

【解決手段】半導体装置1は、カレントミラーで構成されたオペアンプ61を含み、第1の電圧V1から第2の電圧V2を生成するレギュレータ6と、電流量制御信号OVDRを生成し、電流量制御信号OVDRの第1の遷移によってカレントミラーが流す電流を増大させ、電流量制御信号OVDRの第2の遷移によってカレントミラーが流す電流を減少させる制御回路8と、を備え、制御回路8は、第2の遷移に関連する電流量制御信号OVDRの第2のスルーレートを、第1の遷移に関連する電流量制御信号OVDRの第1のスルーレートよりも小さくするスルーレート処理部80を含む。

(もっと読む)

1 - 20 / 159

[ Back to top ]