Fターム[5M024EE17]の内容

DRAM (26,723) | リフレッシュ (1,117) | リフレッシュ制御回路 (615) | リフレッシュの省略 (62)

Fターム[5M024EE17]に分類される特許

1 - 20 / 62

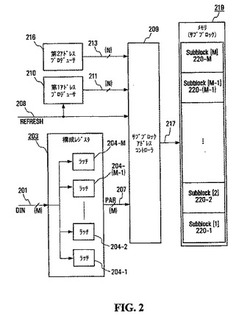

完全に独立のパーシャルアレイリフレッシュ機能を有するダイナミックランダムアクセスメモリ

【課題】独立パーシャルアレイリフレッシュ機能を有する改善されたダイナミックランダムアクセスメモリ(DRAM)を提供する。

【解決手段】DRAMデバイスが、複数のメモリサブブロックを有する。各サブブロックは、複数のワード線を有し、これらのワード線に、複数のデータ記憶セルが接続される。パーシャルアレイセルフリフレッシュ(PASR)構成セッティングが、独立に作られる。PASRセッティングに従って、メモリサブブロックが、リフレッシュのためにアドレッシングされる。PASRセッティングは、メモリコントローラによって作られる。サブブロックアドレスのすべての種類の組合せを選択することができる。したがって、メモリサブブロックは、完全に独立にリフレッシュされる。データ保持に関するユーザ選択可能メモリアレイは、特に低消費電力モバイル応用の有効なメモリ制御プログラミングをもたらす。

(もっと読む)

バッファメモリ装置及び通信装置

【課題】 リフレッシュの有無をリアルタイムに判定でき、しかも、優先データを扱うことが可能なパケットバッファ装置を提供する。

【解決手段】 対象としているパケットバッファ装置は、メモリ空間を複数のブロックに分け、メモリブロック単位で書込みデータのリフレッシュを行うものである。そして、メモリブロック毎に、書込みデータ数と読出しデータ数との一致、不一致を判定する一致・不一致判定手段と、書込みデータ数と読出しデータ数とが一致しているメモリブロックのリフレッシュを禁止し、書込みデータ数と読出しデータ数とが不一致のメモリブロックのリフレッシュを許可するリフレッシュ制御手段とを備えることを特徴とする。

(もっと読む)

メモリ装置のリフレッシュ方法、リフレッシュアドレス生成器及びメモリ装置

【課題】メモリ装置のリフレッシュ方法、リフレッシュアドレス生成器及びメモリ装置を提供する。

【解決手段】リフレッシュレバレッジングを利用してメモリ装置をリフレッシュするように、リフレッシュアドレスがリフレッシュ周期で生成される。リフレッシュアドレスが第2アドレスの時、第2アドレスを有する第1ストロングセルの代わりに第1アドレスを有するウィークセルに対するリフレッシュが実行される。リフレッシュアドレスが第3アドレスの時、第1ストロングセルまたは、第3アドレスを有する第2ストロングセルのうち、いずれか1つに対するリフレッシュが実行される。メモリ容量が減少するように、第1、第2及び第3アドレスうち、ただ1つに対するアドレス情報が保存される。他の実施形態において、リフレッシュレバレッジングを実行するように、リフレッシュアドレスが少なくとも1つの所定のアドレスの時、フラグによってウィークセル、第1ストロングセルまたは、第2ストロングセルのうち、いずれか1つに対するリフレッシュが実行される。

(もっと読む)

通信装置、通信方法、プログラム

【課題】シェーピング処理に際してパケットを格納するバッファとして用いられるDRAMの省電力化を図る。

【解決手段】バッファ30は高優先度対応メモリ部31−1、中優先度対応メモリ部31−2および低優先度対応メモリ部31−3から成る。シェーピング処理に際してバッファにパケットを格納する際は、優先度が対応するメモリ部31に対してデータを格納する。この際、低優先度対応メモリ部31−3については、1つのパケットデータは1カラム内に格納されるようにする。そのうえで、高優先度対応メモリ部31−1および中優先度対応メモリ部31−2についてはオートリフレッシュを実行させ、低優先度対応メモリ部31−3については、データが格納された列のみを対象とするカラム指定リフレッシュを実行させるように構成する。

(もっと読む)

メモリアクセス制御回路およびメモリアクセス制御方法

【課題】半導体メモリに対するアクセス要求が連続して発行される場合でも、アクセス要求とリフレッシュとを効率良く実行することができるメモリアクセス制御回路を提供する。

【解決手段】リフレッシュ要求部20は、半導体メモリ3のリフレッシュを実行するか否かを指定するリフレッシュ発行要求130を出力する。調停部30は、リフレッシュ発行要求130と、半導体メモリ3に対するアクセス要求101及びアクセス対象のアドレス102とを受け取り、リフレッシュ発行要求130がリフレッシュの実行を示す場合、半導体メモリ3に対してリフレッシュ要求を出力し、リフレッシュを実行しないことを示す場合、半導体メモリ3に対してアクセス要求101及びアドレス102を出力する。リフレッシュ要求部20は、マスク部40と要求部60とを備える。

(もっと読む)

メモリシステム、バッファメモリ制御方法およびバッファメモリ制御プログラム

【課題】一時的に使用するデータをリフレッシュ動作の必要なバッファメモリに格納するとき、管理が簡単で必要な箇所にのみリフレッシュ動作を可能とするメモリシステム、バッファメモリ制御方法およびプログラムを得る。

【解決手段】バッファメモリ11は複数のメモリ領域に区分けされており、アドレス記憶手段12にはその全アドレスが格納されている。バッファメモリ11にデータを書き込むときアドレス記憶手段12から所定の順番でメモリ領域を選択し、不要となったデータのアドレスを再選択可能にする。アドレス選択手段13によって使用中とされたアドレスの存在するメモリ領域のみリフレッシュが行われる。

(もっと読む)

メモリ制御装置および画像形成装置

【課題】セルフリフレッシュモード時の消費電流量を低減させる。

【解決手段】データを格納する複数のメモリ2,3と、メモリ2,3を制御する各信号を入出力するメモリコントローラ1と、各信号を接続/切断可能なスイッチ20と、を備え、メモリコントローラ1は、セルフリフレッシュモードへの移行時に、スイッチを切り替えて複数のメモリ2,3を、セルフリフレッシュモード時に電源供給されるメモリ2と、セルフリフレッシュモード時に電源遮断されるメモリ3と、に分け、電源遮断されるメモリ3上における保持が必要なデータを電源供給するメモリ2上に格納する。

(もっと読む)

ダイナミック型半導体メモリのリフレッシュ制御方法

【課題】リフレッシュコマンドの要求頻度を下げると共に、時分割動作を必要としないダイナミック型半導体メモリのリフレッシュ制御方法の提供を図る。

【解決手段】第1または第2のいずれかのメモリブロックに対してリフレッシュ動作を行い、前記リフレッシュ動作を、定期的な制御信号を元に生成したリフレッシュ信号に従って行い、前記リフレッシュ信号を、前記定期的な制御信号を第1の分周率で分周した第1のクロック信号に同期して生成し、前記定期的な制御信号を第1の分周率とは異なる第2の分周率で分周した第2のクロック信号により、リフレッシュ動作を開始し、その後、前記第1のクロック信号に従って、全てのメモリセルに対してリフレッシュ動作を逐次行い、全てのメモリセルに対するリフレッシュ動作が終了したら、次の前記第2のクロック信号が与えられるまでリフレッシュ動作を行わないようにする。

(もっと読む)

半導体装置及びその制御方法

【課題】揮発性記憶素子のリフレッシュに要する消費電力を削減する。

【解決手段】

メモリセルアレイに、予め保持領域とコピー領域とを設定する。パーシャルアクセスモードにエントリする際、前記保持領域に含まれるメモリセルの各々をコピー元とするとともに、該コピー元のメモリセルが接続されるビット線に接続された前記コピー領域に含まれる一又は複数のメモリセルをコピー先として、コピー動作を行う。その後、パーシャルアクセスモード期間中、前記コピー元のメモリセルと前記コピー先のメモリセルとをアクセス単位として動作させる。

(もっと読む)

揮発性メモリの性能へのリフレッシュ動作の影響を最小化する方法およびシステム

【課題】揮発性メモリの性能がリフレッシュにより低下することを防止できるメモリシステムを提供する。

【解決手段】揮発性メモリ110において行われた先行リフレッシュの回数を監視するリフレッシュカウンタ130を備え、定期的にスケジュールされたリフレッシュ要求を検出することに応答して、リフレッシュカウンタを検査して、定期的にスケジュールされたリフレッシュ要求をスキップすることができるかどうかを判断するように構成された制御装置120とを含む。

(もっと読む)

半導体記憶装置

【課題】リフレッシュ制御信号を与える必要がなく、SRAMと同様なアクセスが可能な、DRAMコアを内蔵するシステムLSIを提供する。

【解決手段】セルフリフレッシュタイマは常に動作状態とされリフレッシュ要求信号FAYを定期的に活性化する。行選択系回路/コマンド発生系回路16は、リフレッシュ要求信号FAYと外部からのリードコマンドまたはライトコマンドとが競合したときには、たとえばリードやライト動作が終了してからリフレッシュ動作が行なわれるようにロウ系制御信号を制御する。サブメモリアレイSMAは従来と比べて細分化され、リフレッシュサイクルは短時間で終了するので、リードサイクル時間内でリードとリフレッシュとを終了させることができ、SRAMと同様な簡単な制御で使用できるDRAMコアを実現することができる。

(もっと読む)

半導体記憶装置

【課題】リフレッシュ動作の有無をより細かく指定することが可能な半導体記憶装置を提供する。

【解決手段】それぞれ複数のセグメントに分割された複数のメモリバンクBANK0〜BANK7と、リフレッシュ対象となるメモリバンクを指定するバンクアドレスレジスタ24と、リフレッシュ対象となるセグメントを指定するセグメントアドレスレジスタ23と、バンクアドレスレジスタ24及びセグメントアドレスレジスタ23の少なくとも一方で指定されていないメモリバンク又はセグメントのリフレッシュを禁止するリフレッシュ制御回路22とを備える。本発明によれば、メモリバンク単位だけでなく、メモリバンク内のセグメント単位でリフレッシュ動作の有無を指定できることから、従来のパーシャルリフレッシュよりもさらに消費電力を低減することが可能となる。

(もっと読む)

半導体記憶装置

【課題】リフレッシュに係る消費電流を低減するために特段のリフレッシュシーケンスを必要とする。

【解決手段】半導体記憶装置1は、記憶領域30を複数のバンクメモリ31〜3nによって構成し、それぞれのバンクメモリ単位にリフレッシュ可能な半導体記憶装置である。半導体記憶装置1は、それぞれのバンクメモリ31〜3nに対応してリフレッシュ制御回路21〜2nおよび保持回路11〜1nを備える。保持回路11〜1nは、半導体記憶装置のリセット後に、対応するバンクメモリ31〜3nにデータの書き込みがなされた場合にセットされる。リフレッシュ制御回路21〜2nは、対応する保持回路11〜1nがセットされている場合に、対応するバンクメモリ31〜3nをリフレッシュ実行可能な状態とする。

(もっと読む)

半導体記憶装置

【課題】電源電圧や外部制御信号により記憶容量を切り換えることで動作マージンを向上させた半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、複数のワード線、この複数のワード線に交差する複数のビット線、これらワード線及びビット線の各交差部に配置された2値のデータを保持する複数のメモリセルからなるメモリセルアレイと、制御信号に基づいて前記メモリセルアレイの記憶容量を切り換えるとともに、前記メモリセルのアクセスに必要なアドレス空間の切り替えを行う制御回路とを備えたことを特徴とする。

(もっと読む)

メモリの制御方法および装置

【課題】DRAMのリフレッシュに要する時間を短縮する。

【解決手段】DRAM12に対しライトアクセスした複数のライト済みのロウアドレスを保持するロウアドレス保持ユニット23と、複数のライト済みのロウアドレスの内、リフレッシュサイクル内にライトアクセスおよびリードアクセスのない、未アクセスのライト済みのロウアドレスに対しダミーリードコマンドを発行するダミーリードユニット30と、複数のライト済みのロウアドレスの内、最終のリードアクセスが行われたライト済みのロウアドレスをロウアドレス保持ユニット23から消去する更新ユニット25とを有するリフレッシュ制御ユニット20を提供する。

(もっと読む)

半導体装置

【課題】セルフリフレッシュモード時における消費電流を高速アクセス動作を損なうことなく低減する。

【解決手段】動作モード指示信号がリフレッシュモードを指定するときにメモリアレイのリフレッシュを行なう領域を指定するリフレッシュ領域指定アドレスをアドレスレジスタ(87)に格納する。リフレッシュアドレス発生回路(20b、86,88)は、動作モード指示信号がリフレッシュモードを指定するとき、リフレッシュ領域指定アドレスが指定する領域内のメモリセルのリフレッシュを行なうようにリフレッシュアドレスを発生する。リフレッシュ系回路は、リフレッシュタイマ(85)から所定の周期で発行されるリフレッシュ要求に従って、リフレッシュアドレス発生回路からのリフレッシュアドレスに従って選択されたメモリセルのリフレッシュを行なう。

(もっと読む)

半導体装置

【課題】ロジック回路の電源電圧停止時にメモリリフレッシュ動作を可能とする。

【解決手段】半導体装置は、第1電圧、高い第2電圧を供給されるロジック回路30、第1、第2電圧、高い第3電圧を供給されるメモリ部20を備える。メモリ部20は第1メモリ2、電圧生成回路5、リフレッシュ制御回路40を含む。第1メモリ2は、第1、第2電圧を供給される周辺回路4、第1、第3電圧が供給されるセルアレイコア3を含む。電圧生成回路5は、第1、第3電圧が供給され、第3電圧を降圧又は昇圧した第2電圧より高い第4、第5電圧をセルアレイコア3に出力する。第3、第4、第5電圧はセンスアンプ53、ワード線駆動回路52、ビット線プリチャージ回路22のいずれかに供給される。第3、第4、第5電圧のいずれかはリフレッシュ制御回路40に供給される。リフレッシュ制御回路40は第2電源停止時にセルアレイコア3のリフレッシュ動作を行う。

(もっと読む)

半導体メモリ装置およびその動作方法

【課題】各種のメモリタイプのメモリとして使用でき、しかも、アクセス状況に応じたリフレッシュを行うことが可能な半導体メモリ装置およびその動作方法を提供する。

【解決手段】リフレッシュ動作を要するメモリアレイが形成されたメモリアレイ部3と、外部装置とメモリアレイ部3との間のインターフェースを行うインターフェース部2と、リフレッシュ動作を制御部するリフレッシュ制御部26と、を有し、インターフェース部3は、複数のメモリタイプにそれぞれ対応し、選択的に外部装置とメモリアレイ部3との間のインターフェース処理に適用される複数のインターフェースモジュールを含み、リフレッシュ制御部26は、リフレッシュ周期内においてリフレッシュコマンドを発行する機能を有し、リフレッシュコマンドの発行に際し、上記メモリアレイへのアクセスコマンドとリフレッシュコマンドとが衝突する場合、この衝突を回避する機能を含む。

(もっと読む)

半導体記憶装置

【課題】セルフリフレッシュのエントリ時に、オートリフレッシュとならず直接にセルフリフレッシュのモードにてリフレッシュが開始される半導体記憶装置を提供する。

【解決手段】本発明の半導体記憶装置は、メモリセルに対して行うリフレッシュとして、オートリフレッシュとセルフリフレッシュとのモードを有し、コマンドからリフレッシュモードを検出し、モードを示す種別データを出力し、リフレッシュ開始を示すリフレッシュ信号を出力するコマンドデコーダと、種別データが設定されるモードレジスタと、モードレジスタに設定された種別データで、リフレッシュ信号の遅延の有無を選択し、選択結果にてリフレッシュ信号を遅延させ、または遅延させずにリフレッシュ開始信号として出力する信号選択回路と、モードレジスタに設定された種別データを、リフレッシュ開始信号にて読み込み、種別データに対応するリフレッシュ処理を行う制御回路とを有する。

(もっと読む)

リフレッシュ制御回路

【課題】半導体メモリの各バンク別に所望の特定領域のみをリフレッシュすることができるリフレッシュ制御回路を提示する。

【解決手段】入力される第1アドレス信号と第2アドレス信号とをパルス信号に同期させて、バンクに対するマスク情報信号とセグメントに対するマスク情報信号とを出力するMRSラッチ部10と、前記バンクに対するマスク情報信号に応答して、バンクアクティブ信号を出力するバンクアクティブ制御部20と、前記バンクアクティブ信号、前記セグメントに対するマスク情報信号及び第3アドレス信号に応答して、ローアドレスデコード信号を出力するデコード部30と、を含む。

(もっと読む)

1 - 20 / 62

[ Back to top ]