Fターム[5M024GG15]の内容

Fターム[5M024GG15]に分類される特許

1 - 20 / 27

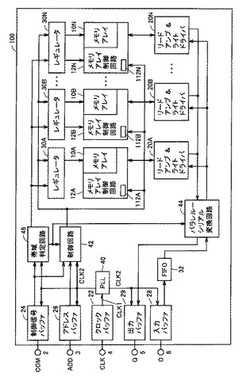

半導体装置

【課題】メモリに入力される外部データが、内部のメモリの処理速度に対して高い場合でも、データの書込みミスなく処理でき、消費電力を抑える半導体装置を提供する。

【解決手段】メモリアレイ制御回路12A〜12Nは、第1の動作として、記憶部に格納されたデータであって、メモリ100の処理速度のうち第1の処理速度で処理可能なデータを読出し、複数のメモリアレイ10A〜10Nへ書込みし、メモリアレイ制御回路12A〜12Nは、第2の動作として、残余データのうちメモリ100の処理速度のうち第2の処理速度で処理可能なデータを読出し、複数のメモリアレイ10A〜10Nへ書込みを行う。

(もっと読む)

メモリインターフェースおよび画像処理装置

【課題】 フレームメモリにすでに書き込まれた直前のフレームを構成する画素の画素値を示すデータの出力を開始するまでの遅延時間の短縮化が図られたメモリ制御回路、および回路規模の削減化が図られた画像処理装置を提供する。

【解決手段】 垂直同期信号VSYNCの立ち下がりエッジをSDRAMコントローラ22で検知して、初期アドレスにクリアされたアドレス信号A,読み出しを指示するコマンドCを生成してSDRAM10に供給し、SDRAM10から所定の範囲の過去データを先読みして読み出し用FIFO23に格納しておき、現在データの入力が開始された後に読み出し用FIFO23から読み出して出力する。

(もっと読む)

モード選択可能プリフェッチおよびクロック対コアタイミングを伴うメモリ装置

【課題】コア速度に過度にストレスをかけずに、広いデータ転送範囲に応じるメモリ装置を提供する。

【解決手段】記憶アレイからリトリーブされたデータの第1の部分またはより小さな第2の部分のどちらかが、プリフェッチモード選択に従ってデータバッファにロードされ、次に、信号インタフェースを介してメモリ装置から出力される。記憶リソースのいずれか1つに連続アクセスを行う間に生じることになるクロック信号の最小サイクル数を示す値は、メモリ装置の構成回路内で受信および記憶する。この値が、閾値数未満であるクロックサイクル数Nを示す場合には、メモリ装置は、クロック信号のNサイクルのそれぞれの間に、信号インタフェースとデータバッファとの間で、第1のアドレスに関連するデータを転送する。Nが閾値数を超えるか等しい場合には、メモリ装置は、別の制御を行う。

(もっと読む)

半導体装置および集積型半導体装置

【課題】積層型半導体装置における全ての半導体チップのテストを行うにあたり、テスト装置側でチップ選択端子に対して割り当てるべき端子数を削減する。

【解決手段】集積型半導体装置100のチップ200において、制御信号出力部210は、制御信号入力端子302Aからの外部制御信号TRGIの入力に応じて、チップ識別子保持部250に対してチップ識別子の保持を指示する。チップ識別子保持部250は指示に応じて、アドレス入力端子303Aから入力されるチップ識別子の値を保持する。また、チップ識別子の保持タイミングを指示した後の所定タイミングで次段チップ制御信号TRGOを出力する。次段チップ制御信号TRGOは、次段のチップ200が制御信号入力端子302Aから外部制御信号TRGIとして入力する。

(もっと読む)

バッファ制御信号生成回路及びこれを用いた半導体メモリ装置

【課題】バッファ制御信号生成回路及びこれを用いた半導体メモリ装置を提供する。

【解決手段】このバッファ制御信号生成回路は、ライトパルスを第1区間分だけクロックシフティングして第1バースト開始信号を生成し、前記ライトパルスを第2区間分だけクロックシフティングして第2バースト開始信号を生成するもので、前記第2区間は、前記第1区間よりも短く設定されるバースト開始信号生成部と、前記第2バースト開始信号及びカラム制御信号に応答してバースト区間パルス及びカラムアクティブパルスを生成するコマンドデコーダと、前記カラムアクティブパルスを受信して、前記バースト区間パルスをバッファリングしてバースト終了信号を生成するバースト制御部と、前記バースト終了信号及び前記カラムアクティブパルスを受信して前記カラム制御信号を生成するバーストカラム制御部と、を含む。

(もっと読む)

半導体記憶装置

【課題】低速なテスト装置を用いてテストをすることが可能な半導体記憶装置を提供する。

【解決手段】入力された入力データをクロック信号の一方のエッジと他方のエッジとに同期して取り込む半導体記憶装置であって、入力された入力データをクロック信号の一方のエッジと他方のエッジとの少なくとも一方に応答して記憶し、記憶された入力データを選択して出力する入力データ記憶選択部を有する。

(もっと読む)

1/4周期遅延クロック発生器

【課題】リセット信号を別途に不要とし、特定の初期値がなくても正常に動作できる1/4周期遅延クロック発生器を提供する。

【解決手段】本発明の1/4周期遅延クロック発生器は、基準クロック信号を発生させる基準クロック発生部と、前記基準クロック信号の立ち上がりエッジで第1入力信号をキャッチして前記基準クロック信号の次の立ち上がりエッジまで第1出力信号として前記第1入力信号を出力し、反転された前記第1出力信号の入力を前記第1入力信号として受ける第1回路部と、第2入力信号をキャッチして第2出力信号として出力し、前記第2入力信号として前記第1回路部から前記第1出力信号の入力を受ける第2回路部とを備える。

(もっと読む)

半導体集積回路装置、リダンダンシシステム

【課題】ヒューズデータの転送は行うが、ヒューズボックスから外部へのヒューズデータの転送(データ出力)は行わないヒューズデータの迂回動作を行うことができ、利便性を向上できる半導体集積回路装置およびリダンダンシシステムを提供する。

【解決手段】半導体集積回路装置は、ヒューズデータをラッチするヒューズラッチ回路12と、ヒューズカウンタ回路13と、前記ヒューズデータを外部に転送する転送回路16と、前記ヒューズデータを転送しない場合に前記ヒューズデータを外部に転送せず自身の中で迂回させる迂回データパスを形成する迂回データパス回路17とを備える制御回路15とを具備するヒューズボックス11において、前記迂回データパス回路17は、前記ヒューズカウンタ回路から送信される制御信号を受信すると、前記ヒューズラッチ回路から次のヒューズデータを要求するリクエスト信号REQを前記ヒューズカウンタ回路13に動作させる。

(もっと読む)

半導体記憶装置、および半導体記憶装置のデータ出力方法

【課題】リードライトアンプ部分への入力信号の本数を減少させることにより、チップサイズを小さくした半導体記憶装置を提供する。

【解決手段】4ビットプリフェッチ動作のDDRにおいて、カラムアドレスの下位2ビットの信号Y0/Y1で分離された4つのデータD0〜D3をデータバスRWBSに転送する際に、DQ部10から先に出力される2データ(前サイクルのデータ)と後に出力される2データ(後サイクルのデータ)の判定を、データセレクタ(13A、13B)の部分においてY1信号のみにより行う。また、RWBS転送後のデータに対し、DQ部10のY0セレクタ&RWBSセレクタ14においてY0信号により順番を切り替える。

(もっと読む)

記憶回路制御装置、記憶回路制御方法

【課題】スキャンテストが失敗した場合でも有効なテスト結果を得ることができる記憶回路制御装置、記憶回路テスト方法を提供する。

【解決手段】複数のスキャンラッチ回路は第1経路で互いに接続されると共に該第1経路と異なる第2経路で互いに接続されており、選択信号が第1経路を示し、且つ初期化信号が初期化タイミングを示す場合、スキャンラッチ回路内の第1経路が透過状態になるようにスキャンラッチ回路への第1クロックを制御する第1クロック制御部と、選択信号と初期化信号とが入力され、選択信号がデータ経路を示し、且つ初期化信号が初期化タイミングを示す場合、スキャンラッチ回路内の第2経路が透過状態になるようにスキャンラッチ回路への第2クロックを制御する第2クロック制御部とを備えた。

(もっと読む)

半導体記憶装置

【課題】回路規模の増大を抑制しつつ、バースト長をプリフェッチ数よりも少なく設定可能な半導体記憶装置を提供する。

【解決手段】データ入出力端子DQに接続されたFIFO回路群123と、データ入出力端子DQを介して連続的に入力され又は連続的に出力するnビットのデータを並列に入出力する時分割転送回路107A,107Bと、時分割転送回路107A,107BとFIFO回路群123との間でデータ転送を行うデータバスRWBSと、バースト長を設定するためのモードレジスタ122とを備える。時分割転送回路107A,107Bは、モードレジスタ122に設定可能な最小バースト長をm(<n)とした場合、バースト長にかかわらずデータバスを用いたデータの転送をmビット単位で行う。これにより、バーストチョップを行うことなく、バースト長をプリフェッチ数よりも少なく設定できる。

(もっと読む)

メモリ装置のためのデータ出力回路及びその駆動方法

【課題】複数のクロック信号の選択的な活性化に応答してデータを出力するメモリ装置のためのデータ出力回路及びその駆動方法を提供する。

【解決手段】メモリカラムアドレスの一部または全体に応答して複数のクロック信号を発生する制御回路と、複数のクロック信号の選択的な活性化に応答して、入力端を通じて受信されたメモリデータを出力端を通じて出力するマルチプレクサ回路と、を備え、複数のクロック信号は、メモリカラムアドレスの一部または全体に基づく順序で順次活性化されることを特徴とするメモリ装置のためのデータ出力回路。

(もっと読む)

モード選択可能プリフェッチおよびクロック対コアタイミングを伴うメモリ装置

【課題】 コア速度に過度にストレスをかけずに、広いデータ転送範囲に応じるメモリ装置を提供する。

【解決手段】

メモリ装置において、記憶アレイからリトリーブされたデータの第1の部分またはより小さな第2の部分のどちらかが、プリフェッチモード選択に従ってデータバッファにロードされ、次に、信号インタフェースを介してメモリ装置から出力される。記憶リソースのいずれか1つに連続アクセスを行う間に生じることになる、クロック信号の最小サイクル数を示す値は、メモリ装置の構成回路内で受信および記憶することができる。この値が、閾値数未満であるクロックサイクル数Nを示す場合には、メモリ装置は、クロック信号のNサイクルのそれぞれの間に、信号インタフェースとデータバッファとの間で、第1のアドレスに関連するデータを転送してもよい。Nが閾値数を超えるか等しい場合には、メモリ装置は、クロック信号のXサイクルのそれぞれの間に、信号インタフェースと記憶バッファとの間で、第1のアドレスに関連するデータを転送し、次に、クロック信号のXサイクルのそれぞれの間に、信号インタフェースと記憶バッファとの間で、第2のアドレスに関連するデータを転送してもよく、Xは、N未満の整数値である。

(もっと読む)

半導体集積回路装置、及び、その制御方法

【課題】半導体集積回路装置の内部状態を保存するために、バッテリバックアップされた外部メモリが必要となる。

【解決手段】半導体集積回路装置は、内部論理回路部と第1メモリと第2メモリと制御回路部とを具備する。内部論理回路部は、回路の正常性を試験するスキャンチェーンを備える。第1メモリは、内部論理回路部によりアクセスされる。第2メモリは、第1メモリに格納されるデータの有効性を示すバリッドビットを第1メモリに関連付けて格納する。制御回路部は、スキャンチェーンに保持される内部状態データを第1メモリに格納し、第1メモリに格納された内部状態データをスキャンチェーンに再設定する。内部状態データが第1メモリに格納された後、第1メモリ及び第2メモリの電源供給を継続しながら内部論理回路部の電源供給を停止し、内部論理回路部の電源供給が再開されたとき、第1メモリに格納された内部状態データをスキャンチェーンに再設定する。

(もっと読む)

クロック同期型メモリ装置及びそのスケジューラ回路

【課題】内部回路の動作開始のタイミングを管理できるスケジューラ回路。

【解決手段】スケジューラ回路2内に、外部クロックまたはそれから生成したクロックに同期しシフト動作するシフトレジスタを設け、コマンドの供給時からコラム系の動作開始までのレイテンシ制御時は、コマンドの供給時にシフトレジスタのレイテンシ対応位置にコラムアクセス信号を格納する。シフトレジスタは、クロックに同期してシフト動作を行うので、レイテンシ対応のクロック数後に、コラムアクセス信号を出力する。コラム制御回路4は、該コラムアクセス信号の出力タイミングに応答し、コラムアドレス等のコラム系回路の動作に必要なデータを取得し、動作を開始する。かくしてスケジューラ回路2の動作は、単純化される。シフトレジスタには、内部動作を開始する内部動作コマンド信号をセットして、任意の内部動作の開始までのレイテンシを容易に管理可能である。

(もっと読む)

メモリアレイ試験回路

【課題】メモリセルアレイの試験回路にあって、待ち時間制御を実現する。

【解決手段】メモリセルアレイ100の欠陥メモリセルを検出すると、比較器104が障害信号出力ライン108に障害信号を生じさせ、これはシフトレジスタ112に送られて、出力回路ブロック118がこの障害信号に応じて高インピーダンス状態に入るようにされる。シフトレジスタ112は、例えば、1,2あるいは3クロックサイクルといった待ち時間の変化度に従った多数のラッチを具備するように構成される。

(もっと読む)

半導体メモリチップ

【課題】ODT非同期信号からODT同期信号への切替をDLL回路の始動時間を考慮して行うことのできる内部ODT信号生成回路を備えたDRAMチップを提供すること。

【解決手段】内部CKE信号生成回路610は、周波数対応信号で示される周波数に応じた遅延量であってDLL回路100の始動時間を考慮して定められた遅延量をクロックイネーブル信号に付加して内部クロックイネーブル信号として出力し、ODTLカウンタ650はそれをODTレーテンシ分だけ遅延させてセレクタ700に選択切替信号として出力する。これにより、ODT信号がアサートされている間におけるODT非同期信号からODT同期信号への切り替えを適切なタイミングでセレクタ700に指示することができる。

(もっと読む)

同期式メモリ装置のウェーブパイプライン構造の出力回路

【課題】同期式メモリ装置のウェーブパイプライン構造の出力回路を提供する。

【解決手段】ウェーブパイプライン構造の出力回路では、同期式メモリ装置の高周波モード時にデータを伝達する経路と、同期式メモリ装置の低周波モード時にデータを伝達する経路とが分離される。そして、高周波モード時のデータ出力経路に備えられるレジスタ数が減少し、かつレジスタのデータ入出力に関連する制御信号数も減少する。その結果、高周波モード時のデータ出力経路の負荷が減少し、これにより、高周波動作が向上し、かつ出力回路のチップ面積が縮小しうる。

(もっと読む)

同期式半導体メモリ装置

【課題】

同期式半導体メモリ装置の動作の際、周波数の変動に関係なく最適化された区間の間、内部電圧がコア回路に供給されるように制御し、回路面積と動作電流量とを大幅に減らすことができる半導体メモリ装置を提供すること。

【解決手段】

カラムアドレスに対応する命令語信号の入力に応答して、カラム動作感知パルスを出力する動作制御部と、クロック信号の周期をN倍分周して出力するシフトレジスタ制御部と、シフトレジスタ制御部から出力される分周クロック信号に同期させて、カラム動作感知パルスを出力端を介して次の端にシフティングさせるための複数のシフトレジスタと、複数のシフトレジスタから出力される出力信号を論理和して、カラムアクティブ信号を出力する信号組み合わせ部と、カラムアクティブ信号の活性化区間の間、内部電圧をメモリコア領域に提供する内部電圧生成部とを備えた。

(もっと読む)

連続的なバーストモードで動作可能な擬似SRAM及びそのバーストモード動作制御方法

【課題】連続的なバーストモードで動作可能な擬似SRAM及びそのバーストモード動作制御方法を提供する。

【解決手段】擬似SRAM及びそのバーストモード動作制御方法は一回受信されたアクセスコマンド及び外部アドレス信号に基づいて、次第に増加するバーストロウ及びカラムアドレス信号を連続的に発生させることにより、連続的なバーストモードでデータの読み出しまたは書き込み動作を実行する。

(もっと読む)

1 - 20 / 27

[ Back to top ]