Fターム[5M024KK18]の内容

DRAM (26,723) | 特定の機能を有するメモリ、特殊なメモリ (655) | 特定の機能 (123) | 省電力モード (45)

Fターム[5M024KK18]に分類される特許

1 - 20 / 45

メモリ制御装置および画像形成装置

【課題】セルフリフレッシュモード時の消費電流量を低減させる。

【解決手段】データを格納する複数のメモリ2,3と、メモリ2,3を制御する各信号を入出力するメモリコントローラ1と、各信号を接続/切断可能なスイッチ20と、を備え、メモリコントローラ1は、セルフリフレッシュモードへの移行時に、スイッチを切り替えて複数のメモリ2,3を、セルフリフレッシュモード時に電源供給されるメモリ2と、セルフリフレッシュモード時に電源遮断されるメモリ3と、に分け、電源遮断されるメモリ3上における保持が必要なデータを電源供給するメモリ2上に格納する。

(もっと読む)

半導体装置

【課題】供給先回路の電流消費量によらず、内部電圧を短時間で安定化させる。

【解決手段】半導体装置10は、外部電位VDDを降圧することによって内部電圧VPERDを生成し、電源配線L1へ供給するVPERD生成回路2aと、接地電圧が供給される接地配線と電源配線L1との間に接続されたスイッチ52と、スイッチ52の開閉制御を行うワンショット信号生成部51とを備え、ワンショット信号生成部51は、VPERD生成回路2aによる内部電圧VPERDの開始と同期してスイッチ52を導通させる。

(もっと読む)

状態検知回路および半導体記憶装置

【課題】より少ない素子数で回路を構成する。

【解決手段】動作制御の開始に係る一連の第1のコマンド信号を計数するカウンタ回路11aと、動作制御の終了に係る一連の第2のコマンド信号を計数する第2のカウンタ回路11bと、カウンタ回路11a、11bにおける計数値の一致を検出するカウンタ一致検出回路12と、第1のコマンド信号でセットされ、カウンタ一致検出回路が一致を検出した場合にリセットされるRSフリップフロップ回路13と、を備え、カウンタ回路11a、11bは、バイナリカウンタを構成要素として備える。

(もっと読む)

半導体装置およびデータ処理システム

【課題】ヒューズ素子などの不揮発性記憶素子から記憶内容を低消費電流で読み出す。

【解決手段】タイミング制御回路は、外部リセット信号の状態遷移を契機として、内部リセット信号PRESET1、2を活性化させる。ヒューズ回路30は、ヒューズ素子31と、内部リセット信号PRESET1に応答して、ヒューズ素子31の設定データを取得する読出回路RDと、設定データを一時的に保持し、内部リセット信号PRESET2によってリセットされるラッチ回路L1を備える。タイミング制御回路は、内部リセット信号PRESET2を活性化させることによりラッチ回路L1をリセットし、内部リセット信号PRESET1を所定期間だけ活性化させることにより設定データをラッチ回路L1に保持させる。

(もっと読む)

セルフリフレッシュ動作モードで内部の高電源電圧を使用する半導体メモリ装置及びその高電源電圧印加方法

【課題】内部高電源電圧を利用して希望の動作をうまく行える半導体メモリ装置を提供する。

【解決手段】セルフリフレッシュ動作モードで内部の高電源電圧を使用する半導体メモリ装置及びその高電源電圧の印加方法が開示される。

複数のメモリバンクからなるメモリセルアレイを具備した半導体メモリ装置を動作させるために高電源電圧を印加する方法は、半導体メモリ装置の動作モードによって区別され得る。セルフリフレッシュ動作と同一である特定動作モードで外部の高電源電圧を受ける必要なく、内部から生成された高電源電圧を受けてメモリバンク別、またはメモリバンクグループ別にセルフリフレッシュを行う方法によれば、高電源電圧発生器のパンピング効率低下の発生無し、動作に必要な高電源電圧が安定的に印加される。

(もっと読む)

半導体メモリ、半導体メモリの制御方法およびシステム

【課題】 モードレジスタにパワーダウン情報が設定されていないときに、半導体メモリのパワーダウン状態への遷移を外部信号により容易に行う。

【解決手段】 モードレジスタは、パワーダウン情報またはリフレッシュ情報が設定される。メモリセルアレイは、端子を介して供給される外部信号とリフレッシュ情報とに基づいて、リフレッシュが行われる。内部回路は、外部信号とパワーダウン情報とに基づいてパワーダウン状態に遷移するとともに、クロック信号に基づいて動作する。検出回路は、クロック信号を検出する。外部信号が活性化されたときに、検出回路がクロック信号を所定期間検出しないときには、モードレジスタにパワーダウン情報を設定する。

(もっと読む)

半導体記憶装置、メモリシステム、及び半導体記憶装置のリフレッシュ制御方法

【課題】リードライトアクセスが必要ないときに低消費電力で待機すると共に、リードライトアクセスが必要になったときに遅滞なくアクセスできる半導体記憶装置、メモリシステム及び半導体記憶装置におけるリフレッシュ制御方法を提供する。

【解決手段】クロックに同期して外部から与えられたコマンドに応答し、リードライト動作を行う動作モードと、外部からリードライトコマンドを受け付けないパワーダウンモードと、を有する半導体記憶装置であって、パワーダウンモードにおいて、外部から与えられた信号に応答してリフレッシュを行う。パワーダウンモードにおいてもメモリコントローラからリフレッシュ制御が行えるので、パワーダウン解除後に遅滞なくアクセスできる。

(もっと読む)

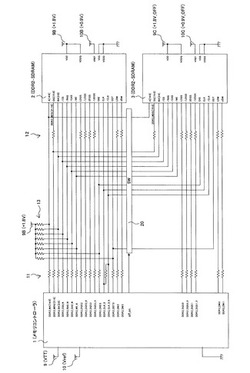

メモリ制御回路

【課題】メモリ動作時の消費電力を低減することができるメモリ制御回路を提供する。

【解決手段】メモリ制御回路は、メモリとして、例えばDDRメモリの動作を制御するものであり、DDRメモリのRASN端子,CASN端子,WEN端子,ADD端子およびBA端子に入力するそれぞれの信号を出力するスリーステートバッファと、DDRメモリが動作時に、該DDRメモリのCSN端子に入力されるCSN信号またはこれに対応する当該メモリ制御回路の内部信号に基づいて、スリーステートバッファに入力される出力イネーブル信号を生成する生成回路とを有する。ここで、スリーステートバッファは、出力イネーブル信号がアクティブ状態の期間、動作状態となり、出力イネーブル信号が非アクティブ状態の期間、出力がハイインピーダンス状態となることにより、上記課題を解決する。

(もっと読む)

ダイナミック型半導体記憶装置およびそのリフレッシュ制御方法

【課題】 低電流動作のために、SCRCを適用した場合にセルフリフレッシュ電流を低減すること。

【解決手段】 スタンバイ状態と活性状態を有するサブスレショルド電流低減回路(300)を適用したコマンド+行系制御回路SCRC領域(120)を備えたダイナミック型半導体記憶装置は、セルフリフレッシュモード時において、スタンバイ状態を解除してコマンド+行系制御回路SCRC領域(120)を活性化し、N本(Nは2以上の整数)のワード線を連続して活性化してメモリセルをリフレッシュした後、スタンバイ状態にしてコマンド+行系制御回路SCRC領域(120)を非活性化するリフレッシュ制御回路(201)を備える。

(もっと読む)

電源制御回路及びこれを用いた半導体メモリ装置

【課題】電源制御回路及びこれを用いた半導体メモリ装置を提供する。

【解決手段】外部コマンドに応答してイネーブル区間が決定されるバッファイネーブル信号を生成するバッファイネーブル信号生成回路と、該バッファイネーブル信号に応答して外部コマンド及び外部アドレス信号をバッファリングして出力するバッファ回路と、を含む入力回路を提供する。

(もっと読む)

半導体メモリ装置

【課題】本発明は、半導体メモリ装置のパワーダウン装置のパワーダウンモード又はセルフリフレッシュモードにおいて、漏れ電流を減少させるための半導体メモリ装置を提供する。

【解決手段】本発明は、バルク端子に第1の電圧が印加されるMOSトランジスタ;及び、前記MOSトランジスタのソース端子に接続され、パワーダウンモードイネーブル信号及びセルフリフレッシュモードイネーブル信号を受信して、パワーダウンモード又はセルフリフレッシュモードでは、前記ソース端子に第2の電圧を印加し、その他のモードでは、前記ソース端子に第1の電圧を印加する電流制御部を含む。

(もっと読む)

半導体記憶装置

【課題】 データリテンションモードへの移行、同モードからの復帰の際に、電源電圧VDDと基板電圧VBBの過渡的な電圧値のアンバランスにより、メモリセルの蓄積電荷の保持特性が悪化することを防止可能な半導体記憶装置を提供することを目的とする。

【解決手段】 第1の動作モードから第2の動作モードへ動作モードが遷移して電源電圧が降下する際の基板電圧の変動期間中に、基板電圧制御回路は、基板電圧を所定電圧に接続することにより第2の電源電圧と基板電圧との電圧のアンバランス状態を迅速に解消し、アンバランス状態における電荷保持性能の悪化現象を防止することが可能となる。

(もっと読む)

リフレッシュフラグを発生させる半導体メモリシステム

【課題】リフレッシュフラグを発生させる半導体メモリシステムを提供する。

【解決手段】本発明による半導体メモリシステムは、所定の出力リフレッシュフラグに応答してアドレス信号及び外部命令の発生を制御するメモリコントローラと、アドレス信号及び外部命令を受信し、メモリセルがリフレッシュされる間、第1ないし第Nリフレッシュフラグを発生する第1ないし第Nメモリ装置を具備するメモリモジュールを具備し、メモリモジュールは、第1ないし第Nフラグ信号のうち1つでも活性化されれば、活性化されたフラグ信号を出力フラグ信号として出力する出力演算部を具備する。

(もっと読む)

半導体記憶装置およびその駆動方法

【課題】データ保持期間におけるリフレッシュ動作の消費電力を低減した半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、フローティングボディ内の多数キャリアの数によって論理データを記憶するメモリセルMCと、複数のメモリセルに接続された複数のビット線BLと、複数のメモリセルに接続された複数のワード線WLと、メモリセルのデータを読み出し、メモリセルへデータを書き込むセンスアンプS/Aと、メモリセルからデータを一旦読出しかつ該データと同一論理データを該メモリセルへ書き戻すリフレッシュ動作を指示するリフレッシュコントローラREFCと、データ読出しモードまたはデータ書込みモードにおいては、或るリフレッシュ動作と次のリフレッシュ動作との間のリフレッシュ間隔を第1の間隔とし、データ保持モードにおいては、リフレッシュ間隔を第1の間隔よりも長い第2の間隔とするリフレッシュ間隔タイマTmr1、Tmr2とを備えている。

(もっと読む)

ダイナミックランダムアクセスメモリ用の低電力リフレッシュ回路および方法

【課題】DRAMの自動リフレッシュの間における消費電力を削減する。

【解決手段】省電力回路100は、DRAMの自動リフレッシュの間にコマンドおよびアドレス信号106に対する入力バッファ102をディセーブルする。入力バッファ102は、発生されるスプリアスコマンドを引き起こさない態様で自動リフレッシュの終了時に再度イネーブルされる。省電力回路は、「非動作」コマンドに対する内部コマンド信号116をバイアスすることによってスプリアスコマンドを回避する。DRAMはまた、DRAMによる電力消費をさらに低減するために、DRAMが自動リフレッシュの終了時に低電力プレチャージモードに自動的に遷移するモードに置かれ得る。

(もっと読む)

半導体記憶装置

【課題】低消費電力スタンバイモードにおいて、安定にメモリセルの記憶データを保持する。

【解決手段】高圧電源制御回路(15)は、電源供給が遮断されるスタンバイサイクル時、負電圧(VBB)を伝達するグローバル負電圧線(69)とサブアレイブロックに対応して設けられるローカル負電圧線(71)とを分離し、また、接地電圧(VSS)を伝達するグローバル接地線(72)とローカル接地線(77)を分離する。これらのローカル接地線およびローカル負電圧線は、対応の電源からの遮断前に、高電圧線(67)を介して高電圧(VPP)レベルに充電される。ワード線(WL<0>−WL<m>)から負電圧線または接地線へのリーク電流経路は遮断され、非選択状態のワード線を確実に非選択電圧(VPPレベル)に維持することができる。

(もっと読む)

SDRAM制御回路及び情報処理装置

【課題】省電力モード時の消費電力が少なく、かつ、省電力モードから通常モードへの復帰に時間がかからないSDRAM制御回路を、提供する。

【解決手段】SDRAM制御回路(メモリ制御ASIC20)を、SDRAM25に定期的にリフレッシュ動作を行わせる機能と、所定の省電力モード移行要イベントが発生した場合には、SDRAM25へのCKEのレベルをローレベルに変更してから、出力するCLKの周波数を下げ、所定の通常モード移行要イベントが発生した場合には、出力するCLKの周波数を通常周波数に戻してから、CKEのレベルをハイレベルに変更する機能とを有する回路としておく。

(もっと読む)

半導体メモリ装置、半導体装置、メモリシステム及びリフレッシュ制御方法

【課題】複数のバンクに付随するキャッシュメモリの有効活用とPASRによるセルフリフレッシュ時の消費電流の低減を両立可能な半導体メモリ装置等を提供する。

【解決手段】本発明の半導体メモリ装置は、複数のバンク(A、B、C、D)に区分されたメモリセルアレイと、複数のバンクにそれぞれ付随しワード線のデータを保持する複数のキャッシュメモリとを備える。各バンクにはセルフリフレッシュ期間中にデータを保持する保持領域と非保持領域とが共通に含まれるように設定されている。セルフリフレッシュ期間中に所定の間隔t0で、PASR状態制御部19とバンク活性化制御部20の動作により、ロウアドレスの一部(X5〜X8)に基づき選択ワード線が保持領域に含まれる場合は全バンクが同時に活性化されてリフレッシュが実行され、選択ワード線が非保持領域に含まれる場合は全バンクが非活性状態となってリフレッシュが実行されない。

(もっと読む)

メモリクロック信号を送信するための、方法および回路

【課題】メモリクロック信号を送信するための、方法および回路を提供する。

【解決手段】メモリ装置において、第1のクロック信号および第2のクロック信号を受信する工程を含む。上記第1のクロック信号の周波数は、上記第2のクロック信号の周波数より小さくてもよい。上記方法は、さらに、上記第2のクロック信号を用いる2以上の各データアクセス動作を実行する工程を含む。上記2以上の各データアクセス動作の1つは、読み出し動作を含んでもよい。また、上記2以上の各データアクセス動作の1つは、書き込み動作を含んでもよい。また、上記方法は、上記第1のクロック信号を用いるコマンド処理動作を実行する工程を含んでもよい。

(もっと読む)

半導体記憶装置

【課題】安定化容量の直列接続された複数のセルキャパシタの接続点の中間電位を適切に制御できるようにすることを目的とする。

【解決手段】電源電圧を昇圧し昇圧電圧VPPをメモリコア12に供給する昇圧電源回路11、昇圧電圧VPPを供給する電源線と接地の間に直列接続された安定化容量14を構成するセルキャパシタC1,C2、及びセルキャパシタC1,C2の接続点に中間電位Vbiasを供給するバイアス発生回路13に加え、さらに昇圧電圧VPPを設定値に下げるクランプ回路15を備え、昇圧電源回路11が昇圧動作を停止する場合に、クランプ回路15により昇圧電圧VPPを設定値にクランプし、その後の通常動作への移行時に中間電位Vbiasが昇圧電圧側や接地電位側に大きく逸脱することを防止できるようにする。

(もっと読む)

1 - 20 / 45

[ Back to top ]