Fターム[5M024LL17]の内容

Fターム[5M024LL17]の下位に属するFターム

端子の共通化 (17)

Fターム[5M024LL17]に分類される特許

1 - 20 / 43

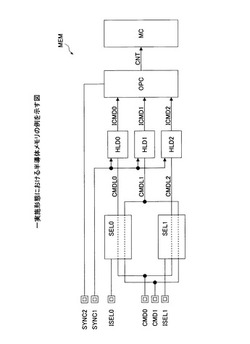

半導体メモリ、半導体メモリの動作方法、システムおよび半導体メモリの製造方法

【課題】少ない数のコマンド端子を用いて、半導体メモリを効率よくアクセスする。

【解決手段】半導体メモリMEMは、選択信号に応じて選択される1つが動作し、複数の第1コマンド端子CMD0、CMD1にそれぞれ供給される複数の第1コマンド信号を受け、受けた第1コマンド信号を出力する複数の第1選択部SEL0、SEL1と、第1選択部の出力に接続され、第1コマンド端子の数より多く、少なくとも1つが第1選択部の複数に共通に接続され、第1選択部の1つから出力される第1コマンド信号を、第1同期信号SYNC1に応答して保持し、第2コマンド信号として出力する複数の保持部HLD0、HLD1、HLD2と、第2コマンド信号に応じた動作制御信号CNTを、第1同期信号に比べて発生頻度が低い第2同期信号SYNC2に応答して出力する動作制御部OPCと、動作制御信号に応じてアクセスされるメモリセルMCとを有している。

(もっと読む)

半導体装置

【課題】小規模な論理回路によって基準レイテンシとオフセットレイテンシを用いた演算を行う。

【解決手段】例えば、基準レイテンシCLの値を示す複数のビットA0〜A3のそれぞれと、オフセットレイテンシSRLの値を示す複数のビットC0〜C2のそれぞれと、を論理合成して複数の制御信号E0〜E3を生成する論理回路100と、複数の制御信号E0〜E3をデコードして複数の制御信号ULPCL4〜ULPCL15を生成する論理回路200とを備える。本発明によれば、基準レイテンシCLの値とオフセットレイテンシSRLの値をデコードする前に演算していることから、より小規模な論理回路によって調整レイテンシULPCLを算出することが可能となる。

(もっと読む)

完全に独立のパーシャルアレイリフレッシュ機能を有するダイナミックランダムアクセスメモリ

【課題】独立パーシャルアレイリフレッシュ機能を有する改善されたダイナミックランダムアクセスメモリ(DRAM)を提供する。

【解決手段】DRAMデバイスが、複数のメモリサブブロックを有する。各サブブロックは、複数のワード線を有し、これらのワード線に、複数のデータ記憶セルが接続される。パーシャルアレイセルフリフレッシュ(PASR)構成セッティングが、独立に作られる。PASRセッティングに従って、メモリサブブロックが、リフレッシュのためにアドレッシングされる。PASRセッティングは、メモリコントローラによって作られる。サブブロックアドレスのすべての種類の組合せを選択することができる。したがって、メモリサブブロックは、完全に独立にリフレッシュされる。データ保持に関するユーザ選択可能メモリアレイは、特に低消費電力モバイル応用の有効なメモリ制御プログラミングをもたらす。

(もっと読む)

半導体装置

【課題】Y方向に隣接する2つの回路ブロックに対しX方向に延在する制御線からタイミング信号を同時に供給する。

【解決手段】例えば、Y方向に配列されたポートPT1,PT2と、ポートPT1,PT2にそれぞれ接続された回路C1,C2と、X方向に延在し回路C1,C2それぞれに含まれるサブ回路SC1,SC2を共通に制御する制御線CTL1を備える。サブ回路SC1,SC2のY方向における中間座標である座標Y1は、ポートPT1,PT2のY方向における中間座標Y0とは異なる。制御線CTL1からサブ回路SC1,SC2へのY方向における距離は互いに等しい。本発明によれば回路C1,C2の動作タイミングを正確に一致させることが可能となる。しかも、複数の制御線を必要とする場合であっても、制御線ごとに対応するサブ回路までの距離を一定とすることが可能となる。

(もっと読む)

情報処理システム

【課題】セルフリフレッシュモードにエントリしている期間中においてもデータ端子のインピーダンス制御を可能とする。

【解決手段】例えば、コントローラ50は、半導体装置10に対してセルフリフレッシュコマンドSREを発行することによってセルフリフレッシュモードにエントリさせる。半導体装置10は、インピーダンス制御信号ODTを受信する入力バッファ回路72をセルフリフレッシュモード中においても常時活性化させるとともに、セルフリフレッシュモード中においては、内部クロック信号ICLK0に同期してインピーダンス制御信号IODT0をラッチするラッチ回路84をバイパスさせる。これにより、外部クロック信号CKを使用することなく、セルフリフレッシュモード中におけるインピーダンス制御信号ODTの入力が可能となる。

(もっと読む)

モノランクとマルチランクとに互換可能なメモリ装置

【課題】モノランクとマルチランクとに互換可能なメモリ装置を提供する。

【解決手段】モノランクとマルチランクとに互換可能なメモリ装置に係り、該メモリ装置は、多数層のメモリレイヤを積層し、該メモリ装置は、チップ識別信号及びモノランクまたはマルチランクを決定するモード信号に応答し、アドレス信号またはチップ選択信号を受信し、多数層のメモリレイヤは、アドレス信号によってアクセスされるモノランクで動作するか、あるいはチップ選択信号によってアクセスされるマルチランクで動作する。

(もっと読む)

半導体記憶装置

【課題】メモリセルアレイと入出力バッファ間の遅延の最大値を抑制し高速に入出力動作が行える半導体記憶装置を提供する。

【解決手段】複数のメモリセルアレイが配置されたメモリセルアレイ部と、外部入出力回路が配置された周辺回路部と、複数のメモリセルアレイと周辺回路部とを接続する内部バス4と、を備え、周辺回路部は、複数の外部入出力バッファ23と、メモリセルアレイとの間で内部バスを並列に入出力するデータと複数の外部入出力バッファを直列に入出力するデータとを相互に変換する複数のバスインターフェース回路24と、を備え、複数のバスインターフェース回路間の距離d1が、複数の外部入出力バッファ間の距離d2及び内部バスの配線幅の最大値d3より狭くなるように、複数のバスインターフェース回路24は、内部バス4と複数の外部入出力バッファとの間にまとめて配置されている。

(もっと読む)

半導体メモリ装置、半導体メモリパッケージ、及び半導体メモリ装置の集積度増大方法

【課題】半導体メモリ装置、半導体メモリパッケージ、及び半導体メモリ装置の集積度増大方法を提供すること。

【解決手段】半導体メモリ装置は、2の指数ビットの集積度で形成された揮発性メモリセル及び揮発性メモリセルのデータ入出力のための入出力端子を各々具備し、1つのチップに形成することによってインテリム集積度(interim density)を有する複数のメモリ領域、並びに、外部から入力されるコマンド及びアドレスに基づいて複数のメモリ領域にデータを書き込みするか、または、複数のメモリ領域からデータを読み出しする動作を制御する少なくとも1つ以上の周辺領域を含む。従って、半導体メモリ装置は、インテリム集積度、即ち、2m+2n+2o…(ただし、m、n、oは0以上の整数として互いに相異する)の集積度を有することができる。

(もっと読む)

半導体装置

【課題】積層型の半導体装置においていずれかのバンクがアクティブ状態であるか否かを判定する。

【解決手段】バンクアドレス信号BA及びアクティブ信号ACT0を出力するインターフェースチップIFと、インターフェースチップIFに積層され、それぞれ対応するバンクアドレス信号BA及びアクティブ信号ACT0を受けて独立にアクティブ状態となる複数のメモリバンクを備えるコアチップCC0〜CC7とを備える。コアチップCC0〜CC7は、其々に含まれる複数のメモリバンクの少なくとも1つがアクティブ状態であるか否かを示すローカルバンクアクティブ信号MCIDTをインターフェースチップIFに其々出力し、インターフェースチップIFは、ローカルバンクアクティブ信号MCIDTの少なくとも1つが活性状態を示すときにバンクアクティブ信号PMCITを活性化させる。

(もっと読む)

半導体装置

【課題】センスアンプのイコライズ速度を高めつつ、イコライズ動作とワード線のリセット動作との同期を取る。

【解決手段】ビット線対BLT,BLBをイコライズするイコライズ回路を含むセンスアンプSAと、イコライズ信号EQBの振幅をVDDレベルに変換するイコライズ制御回路64と、タイミング信号に基づいてサブワード線SWLを制御するワードドライバWDとを備える。ワードドライバWDは、VDDレベルに応じてサブワード線SWLの動作タイミングを変化させるためのレベルシフト回路LV1を含んでおり、これによりVDDレベルが変化した場合であっても、イコライズ動作の完了タイミングとサブワード線のリセットタイミングが連動する。

(もっと読む)

半導体装置

【課題】複数のランクに分類された積層型の半導体装置において、異なるランクに対して連続アクセスされた場合のデータの衝突を防止する。

【解決手段】ライトデータを伝送する貫通電極TSVWとリードデータを伝送する貫通電極TSVRとをそれぞれ有する互いに積層された複数のコアチップCC0〜CC7と、これらコアチップCC0〜CC7に共通接続されたインターフェースチップIFとを備える。インターフェースチップIFは、データ入出力端子16と、データ入出力端子と貫通電極TSVWとの間に設けられた52入力バッファと、データ入出力端子16と貫通電極TSVRの間に設けられた出力バッファ51とを有する。本発明によれば、ライトデータとリードデータを互いに異なる貫通電極を介して伝送していることから、異なるランクに対して連続アクセスされた場合であってもデータの衝突が生じない。

(もっと読む)

半導体デバイス

【課題】チップの入出力構成が異なる場合でも、高い順応性を有し、異なる仕様を構成可能な半導体デバイスを提供する。

【解決手段】内部回路と、内部回路とデバイスの外部とでデータ、アドレス、コマンドまたは電圧の入力、出力または入出力を行う複数の入出力端子31と、複数の入出力端子31の各経路を内部回路の各々が接続された複数の内部経路に選択的に接続させるセレクタ50と、セレクタ50を制御して、データ、アドレス、コマンドまたは電圧と端子との対応関係を変更する経路制御回路(経路選択信号発生回路70)と、を有する。

(もっと読む)

メモリモジュールとコントローラ

【課題】フラッシュメモリのアクセス時間とSDRAMのアクセス時間との整合を図り、大容量フラッシュメモリを含むメモリモジュールとコントローラを提供する。

【解決手段】フラッシュメモリと、SDRAMと、フラッシュメモリ及びSDRAMの夫々のアクセスを制御し、外部からのストア命令に従って、SDRAMに記憶されるデータをフラッシュメモリに転送するための制御回路とそれに結合された複数の入出力端子を含む。制御回路は、ストア命令に従ってSDRAMに記憶されるデータをフラッシュメモリに転送している間に、SDRAMからのデータ読出し命令が入力された場合において、そのデータ転送を中断し、読み出し命令に従ってSDRAMに記憶されるデータを外部に出力するよう制御する。

(もっと読む)

半導体装置

【課題】単一の半導体メモリチップを互いに異なるピン配列を備えたパッケージに実装する場合に、半導体メモリチップのパッド数の増加を防止する。

【解決手段】製品指定情報が、ボンディンク回路、ヒューズ回路等の製品指定情報回路228から与えられる。デコーダ回路224は、この製品指定情報をデコードして、該デコード結果に応じて複数の信号回路220の1つを選択的にチップ・パッド210に接続する。

(もっと読む)

半導体装置及び半導体モジュール

【課題】DDP構造の半導体モジュールにおいて、上下のメモリのいずれにおいても、基板との間の信号経路を、DQ信号とDQS信号とで等長にすること。

【解決手段】本発明の半導体装置は、×N動作から×M(M=N/2)動作への切替を指示する信号が入力される入力端子と、偶数番目のDQピンまたは奇数番目のDQピンを指示する切替信号が入力される入力端子と、DQSピンからDQS信号が供給されると、供給されたDQS信号にしたがって、対応するDQピンを介してDQ信号を入出力するN個のDQ制御回路と、×M動作時に、偶数番目のDQピンが指示された場合、偶数番目のDQピンに対応するDQ制御回路にDQS信号を供給する第1のDQS制御回路と、×M動作時に、奇数番目のDQピンが指示された場合、奇数番目のDQピンに対応するDQ制御回路にDQS信号を供給する第2のDQS制御回路と、を有する。

(もっと読む)

半導体記憶装置及びこれを備えた情報処理システム

【課題】2次元のデ−タ配列の各行を複数のバンク内のページに分散配置してアクセス(スキャッタ・ギャザーアクセス)する場合に、アクセス時間を短縮するとともに消費電力を削減すること。

【解決手段】半導体装置は、複数のデータ入出力ピンと、それぞれ複数の記憶情報を記憶する複数のバンクと、セレクタと、制御回路と、を備え、制御回路は、第1のアクセスモードとして、外部からの1回の読み出し又は書き込み命令に応じて、複数のバンクに対して同時にアクセスし、セレクタは、第1のアクセスモードとして、複数のデータ入出力ピンと複数のバンクとを所定の関係で対応付ける。

(もっと読む)

半導体メモリ

【課題】 半導体メモリのデータ端子を任意に選択可能にし、1つの半導体メモリを様々な端子仕様のコントローラに接続する。

【解決手段】 半導体メモリは、複数のデータ端子と、データ端子にそれぞれ対応して設けられ、対応するデータ端子に供給されるデータを保持するメモリセルを含み、第1許可禁止信号にそれぞれ応じて動作が許可または禁止される複数の内部回路と、設定期間にデータ端子にそれぞれ供給される論理を許可レベルまたは禁止レベルとしてそれぞれ保持し、第1許可禁止信号として出力するレジスタとを有している。

(もっと読む)

半導体装置

【課題】予備の貫通電極を用いて貫通電極の不良を救済する場合に、置換の前後における信号パスの長さの差を短縮する。

【解決手段】ドライバ回路101〜108を有する半導体チップIFと、レシーバ回路201〜208を有する半導体チップCCと、半導体チップCCに設けられた貫通電極301〜309とを備える。半導体チップIFは、i番(iは1〜nの整数)のドライバ回路の出力端をi番からi+m番の貫通電極のいずれかに排他的に接続する出力切り替え回路120を有し、半導体チップCCは、i番(iは1〜nの整数)のレシーバ回路の入力端をi番からi+m番の貫通電極のいずれかに排他的に接続する入力切り替え回路220を有する。これにより、置換前の信号パスと置換後の信号パスとの間にほとんど配線長差が生じないことから、信号品質が高められる。

(もっと読む)

半導体装置及びこれを備える情報処理システム

【課題】貫通電極に接続されているすべての双方向バッファ回路の出力バッファがハイインピーダンスとなった場合でも、貫通電極が論理不定状態となることを防止する。

【解決手段】半導体装置10は、積層された複数のコアチップCC0〜CC7及びインターフェースチップIFとを備えている。複数のコアチップCC0〜CC7及びインターフェースチップIFの各々は、半導体基板を貫通する複数の貫通電極TSV1と、貫通電極TSV1を駆動する双方向バッファ回路BUとを含み、インターフェースチップIFは、貫通電極TSV1の論理レベルを保持する論理レベル保持回路26をさらに含んでいる。双方向バッファ回路BUは、入力バッファIB及び出力バッファOBを含み、論理レベル保持回路26の第1のインバータINV1の駆動能力は、双方向バッファ回路BUの出力バッファOBの駆動能力よりも小さい。

(もっと読む)

半導体装置及びその制御方法並びにデータ処理システム

【課題】複数のコアチップから出力されるリードデータをインターフェースチップにおいて正しく取り込む。

【解決手段】コアチップCC0〜CC7は、パラレルデータの出力に同期したタイミング信号DRAOIFをインターフェースチップIFに出力するタイミング制御回路100を含み、インターフェースチップIFは、タイミング信号DRAOIFに同期してパラレルデータを取り込むデータ入力回路25iを含む。これにより、パラレルデータの出力タイミングと、パラレルデータの取り込みタイミングがいずれもコアチップによって生成されるタイミング信号に同期することから、各コアチップとインターフェースチップとの間に動作速度差がある場合であっても、インターフェースチップ側においてパラレルデータを正しく取り込むことが可能となる。

(もっと読む)

1 - 20 / 43

[ Back to top ]