国際特許分類[C30B25/16]の内容

化学;冶金 (1,075,549) | 結晶成長 (9,714) | 単結晶成長;そのための装置 (9,714) | 反応ガスの化学反応による単結晶成長,例.化学蒸着による成長 (895) | エピタキシャル層成長 (890) | 制御または調整 (42)

国際特許分類[C30B25/16]に分類される特許

1 - 10 / 42

キャリアライフタイムが改善された基板を製造する方法

【課題】得られるコーティングが0.5マイクロ秒〜1000マイクロ秒のキャリアライフタイムを有するように、シリコンカーバイドコーティングを基板上に堆積させる方法を提供する。

【解決手段】a.ジクロロシランガス、メチルハイドロジェンジクロロシランガス、ジメチルジクロロシランガス、及びそれらの混合物から選択されるクロロシランガスと、炭素含有ガスと、水素ガスとを含む混合ガスを、単結晶シリコンカーバイド基板を含有する反応チャンバ内に導入すること、及びb.1200℃より高いが1800℃より低い温度に基板を加熱すること、を含むが、但し、反応チャンバ内の圧力は10torr〜250torrの範囲に維持されるものとする。

(もっと読む)

エピタキシャルウエハ及び半導体素子

【課題】エピタキシャル成長層の結晶品質を向上させることができ、厚膜のエピタキシャル成長層を形成する場合においてもキャリア移動度の低下が生じず、素子抵抗の低い炭化珪素エピタキシャルウエハおよび炭化珪素半導体素子を提供する。

【解決手段】炭化珪素半導体素子は、ドーピングにより格子定数が減少するドーパントを濃度Aでドーピングした基板と、ドーパントを基板よりも小さい濃度Bでドーピングしたエピタキシャル成長層と、基板とエピタキシャル層との間に、ドーパントをドーピングした2層以上積層した多層構造で形成されたバッファ層とを有し、多層構造の各層のドーパントのドーピング濃度Cが、バッファ層の厚さをd、エピタキシャル成長層からの各層までの平均距離をx、所定の割合をPとして、[B+(A−B)×x/d]×(1−P)≦C≦[B+(A−B)×x/d]×(1+P)とした。

(もっと読む)

炭化珪素単結晶エピタキシャルウエハの製造方法

【課題】加工変質層の除去処理にかかる時間を減少させつつも、加工変質層に由来するエピタキシャル膜の欠陥の発生を抑制できる炭化珪素単結晶エピタキシャルウエハの製造方法を提供する。

【解決手段】炭化珪素単結晶エピタキシャルウエハの製造において、炭化珪素単結晶基板100を1600℃以上に加熱し、C/Si比が1.0以下となるように、原料ガスを供給し、エピタキシャル膜の成長速度を2.0μm/h以下にする。このとき、キャリアガスの流量を50slm以上にし、原料ガスとしてモノシランの流量を20sccm以下にし、成長装置の前記炭化珪素単結晶基板100が配置された空間の圧力を100mbar以上にすることにより、エピタキシャル膜の成長速度を2.0μm/h以下にすることができる。

(もっと読む)

窒化物半導体薄膜およびその成長方法

【課題】従来よりも原子レベルで平坦な表面を有する窒化物半導体薄膜及びその成長方法を提供する。

【解決手段】ミスカットを有するGaN基板101のステップフロー成長(工程1)により制限領域内に形成されたテラス202に、工程1よりもキャリアガスに含まれる水素の組成を少なくして、トリメチルガリウム(TMG)又はトリエチルガリウム(TEG)を供給し、テラス202の上にGaNの2次元核301を1個以上100個以下発生させる(工程2)。次に、工程2よりもキャリアガスに含まれる水素の組成を多くする(工程3)。これにより、複数の2次元核301が横方向成長して1分子層の厚さの連続的なGaN薄膜302となる。工程2と工程3を交互に繰り返すことにより、2分子層以上の厚さのGaN薄膜303を成長させる。

(もっと読む)

窒化物半導体基板の製造方法及び窒化物半導体自立基板の製造方法

【課題】窒化物半導体単結晶の反り(面方位分布)を抑制するとともに、均質な結晶成長を行うことができる窒化物半導体基板の製造方法及び窒化物半導体自立基板の製造方法を提供する。

【解決手段】窒化物半導体基板の製造方法は、HVPE炉20において、石英リアクタ7内の結晶成長領域の温度分布を略均一に保持してGaN薄膜2及びストライプマスク4を有する基板1上にGaN厚膜5を成長させるとともに、成長中のGaN厚膜5の反りが予め定めた範囲内になるように当該HVPE炉20を加熱するヒータ8の制御温度を変化させる。

(もっと読む)

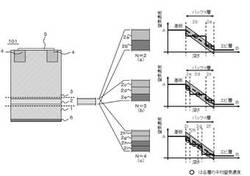

シリコンエピタキシャルウエーハ製造システム及びシリコンエピタキシャルウエーハの製造方法

【課題】一定量のシリコン原料ガスをシリコンエピタキシャル成長装置の反応室に供給できるシリコンエピタキシャルウエーハ製造システム及びシリコンエピタキシャルウエーハの製造方法を提供する。

【解決手段】原料混合ガス集中供給装置1で生成した原料混合ガス中のシリコン原料ガスの濃度値を常時測定する複数の濃度値測定装置18a,18bと、前記濃度値、又は前記濃度値から計算された補正値を各シリコンエピタキシャル成長装置11,12,13にデジタル信号で伝達する伝達手段17と、前記濃度値若しくは前記補正値に基づいて、各シリコンエピタキシャル成長装置11,12,13内の反応室11c,12c,13cに供給する前記原料混合ガスの量を随時補正する流量制御装置14,15,16と、を具備するシリコンエピタキシャルウエーハ製造システム10とする。

(もっと読む)

単結晶、マイクロエレクトロニクス・デバイス構造、ウエハおよび製品

【課題】マイクロエレクトロニクス・デバイス構造の組み立てのために用い得るブールの提供。

【解決手段】相応する天然III−V族窒化物シード結晶上で、気相エピタクシーによって、1時間に20μmを上回る成長速度で、III−V族窒化物材料を成長させることにより、III−V族窒化物ブールを形成する。形成されるブールは、マイクロエレクトロニクス・デバイス品質を含み、例えば、1cmより大きい断面寸法、1mmを超える長さ、および1cm2あたり107未満欠陥の上面欠陥密度を有する。

(もっと読む)

GaN結晶自立基板およびその製造方法

【課題】全表面でイエロー発光が少なく、導電性を有するGaN結晶自立基板およびその製造方法を提供する。

【解決手段】本GaN結晶自立基板は、HVPE法により、結晶側面を除く結晶成長面として、(0001)面と{10−11}面および{11−22}面の少なくともいずれかの面とが混在する状態で成長させたものであり、(0001)面成長結晶領域において炭素濃度が5×1016個/cm3以下かつ珪素濃度が5×1017個/cm3以上2×1018個/cm3以下かつ酸素濃度が1×1017個/cm3以下であり、{10−11}面および{11−22}面の少なくともいずれかの面を結晶成長面として成長したファセット結晶領域において炭素濃度が3×1016個/cm3以下かつSi濃度が5×1017個/cm3以下かつ酸素濃度が5×1017個/cm3以上5×1018個/cm3以下である。

(もっと読む)

エピタキシャルウエーハの製造方法

【課題】p型層を形成する際に混入するSiによって発生する順方向電圧(Vf)の不良を従来より低減させ、順方向電圧が良好なエピタキシャルウエーハの製造方法を提供する。

【解決手段】少なくとも、化合物半導体からなる基板上に、ハイドライド気相成長法によってp型層をエピタキシャル成長させる工程を有するエピタキシャルウエーハの製造方法であって、前記p型層をエピタキシャル成長を開始する前の前記基板の昇温時に、p型ドーパントガスを前記p型層のエピタキシャル成長時より多く流すことを特徴とするエピタキシャルウエーハの製造方法。

(もっと読む)

SiC単結晶の製造方法

【課題】所望の口径の結晶を得ることができるSiC単結晶の製造方法及び製造装置を提供する。

【解決手段】SiC種結晶13からSiC単結晶14を成長させる際において、X線発生装置21とイメージ管22を用いて結晶口径を測定する。そして、上下動機構17により結晶14のガイド部材6aへの挿入量を変化させて、測定した結晶口径を任意の設定値に合わせ込む。

(もっと読む)

1 - 10 / 42

[ Back to top ]