国際特許分類[G05F3/26]の内容

物理学 (1,541,580) | 制御;調整 (21,505) | 電気的変量または磁気的変量の調整システム (3,201) | 自己調整特性を有する一つの非制御素子,または複数の素子から成る組合せであって自己調整特性を有するものによって,電気的変量を調整する非反作用系 (687) | 電流または電圧の調整 (687) | 直流のもの (678) | 非線形特性を有する非制御素子を使用するもの (675) | 半導体装置であるもの (675) | ダイオードトランジスタの組合せを用いるもの (666) | カレントミラー (269)

国際特許分類[G05F3/26]の下位に属する分類

国際特許分類[G05F3/26]に分類される特許

1 - 10 / 266

半導体集積回路、および、半導体記憶装置

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

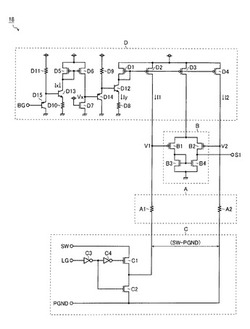

過電流保護回路及びこれを用いたスイッチング電源装置

【課題】過電流保護値に適切な負の温度特性を持たせる。

【解決手段】過電流保護回路18は、抵抗値の異なる抵抗A1、A2を含む抵抗部Aと、抵抗A1、A2に現れる電圧V1、V2を比較して過電流保護信号S1を生成する比較部Bと、抵抗A1、A2にスイッチ素子12の降下電圧(SW−PGND)を印加する入力部Cと、電流値の等しい電流I1、I2を生成して抵抗A1、A2に供給する電流生成部Dとを有し、電流生成部Dは、抵抗A1、A2と同一の温度特性を有しており、温度特性のフラットな基準電圧BGから基準電流Ixを生成する抵抗D10と;スイッチ素子12と同一の温度特性を有しており、基準電流Ixから基準電圧Vxを生成する抵抗D7と;負の温度特性を有しており、基準電圧Vxから基準電流Iyを生成する抵抗D8と;基準電流Iyから電流I1、I2を生成するカレントミラー(D1〜D4)と;を含む。

(もっと読む)

定電流回路

【課題】付加する起動回路を小面積とし、高電源電圧でも低消費電流を実現した定電流回路を提供すること。

【解決手段】PNP型のトランジスタQ1,Q2からなる第1のカレントミラー回路と、NPN型のトランジスタQ3,Q4、抵抗R1からなる第2のカレントミラー回路より構成された起動回路において、PNP型のバイポーラトランジスタQ5とN型のJFETトランジスタJ1からなる起動回路を設けた。

(もっと読む)

定電流回路及び基準電圧回路

【課題】高温時でもエンハンスメント型Nチャネルトランジスタが弱反転状態で動作できる定電流回路を提供する。

【解決手段】カレントミラー回路と定電流生成ブロック回路とオフリーク回路を備えた定電流回路において、オフリーク回路は、ゲートとソースが接地端子に接続され、ドレインが定電流回路の出力に接続される第一のエンハンスメント型Nチャネルトランジスタで構成される。これにより、定電流を生成するエンハンスメント型Nチャネルトランジスタのゲート−ソース間電圧の上昇を抑えることで、弱反転状態での動作を保つ。

(もっと読む)

DC−DCコンバータの異常電流防止回路

【課題】回路規模が小さくて遅延が少なく且つ特性に与える素子バラツキの影響が小さいDC-DCコンバータの異常電流防止回路を提供する。

【解決手段】電流検出抵抗12を流れる電流を所定の基準電流と比較して過電流の有無を判定する電流コンパレータ30を備える。検出抵抗12の電圧は通常時(正常時)には負電圧であるが異常時に逆電流が生じた場合には正電圧が現れるようになる。電流コンパレータ30は検出抵抗12の電圧を監視し、検出抵抗12の電圧が負電圧の間はハイ出力をラッチ10を介してAND回路20に送ってPWM比較器9の出力信号がローサイド側スイッチ素子14,19に伝わるようにし、検出抵抗12の電圧が正電圧になると電流コンパレータ30の出力電圧はローになり、ローサイド側スイッチ素子14,19を強制的にOFFにする。

(もっと読む)

定電流回路の出力設定装置

【課題】電流値の設定が容易であり、且つ、装置構成を簡素化することが可能な定電流回路の出力設定装置を提供する。

【解決手段】基準電流Irefを流す基準電流発生回路11と、基準電流Irefに比例した電流を流すカレントミラー回路を少なくとも一つ備えた、4個のカレントミラー回路群、即ち、第1〜第4のカレントミラー回路群21〜24を備える。そして、各カレントミラー回路群21〜24は、それぞれ、基準電流Irefに対してα倍、2α倍、4α倍、8α倍となる電流を出力する。そして、各カレントミラー回路群を適宜選択して負荷に接続することにより、該負荷に供給する電流値が所望の電流値となるように設定することが可能となる。このため、操作性を容易とし、且つ、装置構成を簡素化することが可能となる。

(もっと読む)

スイッチング電源回路

【課題】バイパス容量の容量値を大きくすることなく、供給電流の変動を抑制する。

【解決手段】負荷の状態に応じて予め設定したピースワイズリニア信号に基づき、負荷が重負荷のとき所定の電流値、軽負荷のとき零となり、重負荷と軽負荷との間で切り替わるとき前記所定の電流値と零との間で線形に変化する電流Im12を入力電圧Vinから生成する。また、前記ピースワイズリニア信号に基づき、負荷が前記重負荷のとき零、前記軽負荷であるとき前記所定の電流値となり、重負荷と軽負荷との間で切り替わるとき零と前記所定の電流値との間で線形に変化する電流Im13を出力電圧Voutから生成する。前記電流Im12と前記電流Im13との和を供給電流Isup1とし、これを制御回路Ctrl1に供給する。

(もっと読む)

基準電圧回路

【課題】プロセス変動によるバラつき要因が少ない基準電圧回路の提供。

【解決手段】第1のMOSトランジスタと、ゲート端子が第1のMOSトランジスタのゲート端子に接続され、第1のMOSトランジスタのしきい値の絶対値とK値より高いしきい値の絶対値とK値を有する第2のMOSトランジスタと、第1のMOSトランジスタと第2のMOSトランジスタのしきい値の絶対値の差に基づく電流を流すカレントミラー回路と、カレントミラー回路の電流を流す第3のMOSトランジスタと、第3のMOSトランジスタのしきい値の絶対値とK値より高いしきい値の絶対値とK値を有し、カレントミラー回路の電流を流す第4のMOSトランジスタを備え、第3のMOSトランジスタと第4のMOSトランジスタのしきい値の絶対値とK値の差に基づく定電圧を基準電圧として出力する、構成とした。

(もっと読む)

定電圧発生回路

【課題】定電圧発生回路の回路面積及び消費電流を削減しながら、負荷の直流的及び過渡的な変化に対する出力電圧の変化を小さくする。

【解決手段】FET4は、電圧源端子に接続されたドレインと出力端子に接続されたソースとを備える。FET2は、FET4のソースに接続されたゲートと、FET4のゲートに接続されたドレインとを有する。FET1は、FET2のソースと接地端子との間に設けられ、ダイオード接続されている。FET3は、電圧源端子とFET2のドレインとの間に接続され、そのドレインとソースとの間に所定の電位差を有し、第1の定電流源として機能する。FET5は、出力端子と接地端子との間に接続される。FET1及びFET5によりカレントミラー回路を構成することにより、FET5は第2の定電流源として機能する。

(もっと読む)

電圧生成回路およびパワーオンリセット回路

【課題】電源電圧が一時的に低下した場合であっても、その後電源電圧が上昇すれば基準電圧を素早く出力できるようにした電圧生成回路、および、リセット信号を素早く出力できるようにしたパワーオンリセット回路を提供する。

【解決手段】トランジスタMP5およびMP6が第1電源線N1およびノードN6間に直列接続されている。トランジスタMP5が起動電流Isをセンシングし、トランジスタMP6が基準電流Ipをセンシングする。電源電圧VDDが低下したとしても、両トランジスタMP5およびMP6には閾値電圧以上となる電圧がゲートソース間に与えられる虞がなくなり、充電回路8には充電電流Ioが充電されにくくなる。したがって、電源電圧VDDが再復帰して電源電圧が上昇したときには、トランジスタMP4が起動電流IsをノードN5に素早く供給でき、電流生成回路6は基準電流Ipを素早く生成できる。

(もっと読む)

1 - 10 / 266

[ Back to top ]