国際特許分類[G06F11/28]の内容

物理学 (1,541,580) | 計算;計数 (381,677) | 電気的デジタルデータ処理 (228,215) | エラー検出;エラー訂正;監視 (10,741) | 処理順序の正しさを検査することによるもの (1,742)

国際特許分類[G06F11/28]に分類される特許

41 - 50 / 1,742

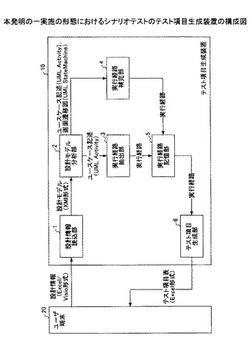

シナリオテストのテスト項目生成装置及び方法及びプログラム

【課題】 ユースケース記述の欠落部分を検出し、網羅的なシナリオテストを実行する。

【解決手段】 本発明は、入力されたユーザとシステム間のインタラクションの流れを示すユースケース記述に基づいて実行経路を抽出し、実行経路記憶手段に格納し、ユースケース記述と、画面間の遷移を示す画面遷移図のマッチングを行い、該画面遷移図には存在するが該ユースケース記述には存在しない遷移がある場合は、該ユースケース記述が不完全であると判断し、ユースケース記述が不完全であると判断された場合に、欠落している遷移について新たな実行経路を生成し、実行経路記憶手段に格納し、実行経路記憶手段から実行経路を読み出して、該実行経路に対するテスト項目を生成する。

(もっと読む)

異常系シナリオの組合せのテスト項目生成装置及び方法及びプログラム

【課題】 複数種類の異常系シナリオの実行順序に依存しない組合せにより発生するエラーを検出するための最小限のテスト経路(テスト項目)生成する。

【解決手段】 本発明は、入力された設計モデルからユーザとシステムの間のインタラクションの流れを示すユースケース記述を取得し、ループ無し経路を抽出し、テスト経路集合に加え、ユースケース記述からループ有り経路を抽出し、ループ無し経路と該ループ有り経路をつなぎ合わせた新たなテスト経路を、新規追加分テスト経路集合に加え、新規追加分テスト経路集合からユースケース記述の基本フローである正常系シナリオを除外した集合をテスト経路集合に加え、該テスト経路集合を実行経路記憶手段に格納し、実行経路記憶手段からテスト経路を読み出して、該テスト経路に対するテスト項目を生成する。

(もっと読む)

ソフトウェアデバッグ支援プログラム、ソフトウェアデバッグ支援装置およびソフトウェアデバッグ支援方法

【課題】ソフトウェアデバッグに必要となるソースコードに関する情報を自動的に提供すること。

【解決手段】ソフトウェアデバッグ支援装置100は、ハードウェアモデル112によって検証対象のソフトウェアが実行されると、ソフトウェアのソースコードごとの実行結果に当該ソースコードのアドレスを関連付つけたログデータ105を生成すると、生成されたログデータ105を記録領域に蓄積する。ソフトウェアデバッグプログラム120は、蓄積されたログデータ105の中の任意のログデータの選択を受け付けると、任意のログデータの実行結果に関連付けられているソースコードのアドレスを参照して検証対象のソフトウェアから任意のログデータ105に対応するソースコード132を検索してGUI130に出力する。

(もっと読む)

リグレッションテスト支援プログラム及びリグレッションテスト支援装置

【課題】リグレッションテストにおいて期待値として使用されるデータの中から編集対象とするデータを見付け易くすること。

【解決手段】リグレッションテスト支援プログラムは、ディプレイ上に表示されている一以上のブラウザ画面のいずれかの表示内容の更新を検知し、前記更新が検知されるたびに、表示されている全ての前記ブラウザ画面の表示内容を示す情報と、当該更新に係る前記ブラウザ画面の識別情報とを含むデータを第一の記憶部に記録し、前記データの編集指示に応じ、前記第一の記憶部を参照し、前記識別情報に係る前記ブラウザ画面の表示内容を示す画像の一覧を表示させる処理をコンピュータに実行させる。

(もっと読む)

プログラム検査装置

【課題】プログラムの問題箇所を容易に発見できる妥当性検査を行うことができ、システムプログラマのデバック効率を向上する。

【解決手段】IEC 61131-3に準拠した命令語を用いるプログラムのオブジェクトファイルを取得し、ステップ順に機械語のスタック操作をシミュレーションして得られた変数、あるいは定数を用いて、プログラムの動作不備を引き起こす可能性のある箇所および要因を検出する検出部12Cと、検出部12Cで検出された箇所および要因を表示する表示処理部12Dと、を備え、検出部12Cは、シミュレーションの過程で得られる変数、あるいは、定数を用いて、変数の領域外アクセスの箇所を検出する機能12C1と、無限ループの可能性がある箇所を検出する機能12C2と、データの精度が欠落する可能性がある箇所を検出する機能12C3と、条件が成立しない可能性のある箇所を検出する機能12C4と、の少なくとも1つを含む。

(もっと読む)

電力遷移中におけるデジタル信号プロセッサデバッギングに関する方法

【課題】デジタル信号プロセッサ電力遷移中におけるデバッギング動作を制御する。

【解決手段】ウォームブートパワーダウンシーケンス220が開始されると、ポイント228において、電力崩壊割り込みが生じ、カーネル遮断ハンドラーが動作し、電力崩壊割り込みが無効にされる(230)。ポイント232において、ISDB_CORE_READYレジスタが0を読み取り、JTAGread/writeが無効状態を戻す。コアプロセッサは、ISDBコンフィギュレーションの変更が進行中である場合は、パワーダウンシーケンスの取り消しを行わせる。コンフィギュレーションが進行中でない場合は、パワーダウンシーケンス220は、ISDBコンフィギュレーションレジスタの内容をメモリにセーブする。ウォームブートフラグマーカーがセットされる。次に、パワーダウンシーケンスが全スレッドを停止させ、DSPがパワーダウンされる。

(もっと読む)

シミュレーション装置、シミュレーション方法、及びプログラム

【課題】IOレジスタを用いた周辺機器の呼び出しに対応し、シミュレーション速度を向上させたシミュレーション装置、シミュレーション方法、及びプログラムを提供すること

【解決手段】CPUシミュレーション部20は、CPUを模擬してシミュレーションを実行する。周辺機器シミュレーション部50は、IOレジスタへのアクセスにより動作させる周辺機器を模擬してシミュレーションを実行する1つ以上のコンポーネント(タイマシミュレーション部51等)を備える。検出部60は、シミュレーション実行時に前記周辺機器に対応するIOレジスタへのアクセスを検出する。接続管理部70は、検出部60の検出結果に応じてシミュレーション実行時に動作させるコンポーネントを設定する。

(もっと読む)

データフロー検証支援装置およびデータフロー検証支援方法

【課題】所定のデータフローについてシミュレーションを実施したかどうかを自動的に確認する。

【解決手段】プログラミング言語やハードウェア記述言語等により記述されたシステムの動作検証を支援する装置であって、前記システムの構造を表現するためのブロック図を作成してブロック図情報を生成するブロック図作成手段と、前記ブロック図に対して前記システムにおけるデータの流れる経路を示すデータフローの表記を受け付け、データフロー情報を生成するデータフロー表記手段と、入力パターンに基づいて前記システムの動作をシミュレーションしてシミュレーション結果情報を生成するシミュレーション手段と、前記データフロー情報のデータフローの示す経路が前記シミュレーション結果情報の示す経路と同じであるかをチェックするデータフローチェック手段とを備える。

(もっと読む)

JTAGの電力崩壊のデバッグ

【課題】電力崩壊の後にプロセッサ上でデバッグ動作を実行する。

【解決手段】プロセッサの状態レジスタが、デバッガを使用してスキャンされる。基準クロックのクロックエッジが、ある期間内にJTAGインターフェースの再同期されたタイミングクロックRTCKのピン上に現れないとき、タイムアウトの条件が検出される。デバッガは、デバッグ論理リセット状態に入る。デバッガは、プロセッサが再びアクティブになったことを示す次のRTCK信号のエッジを検出する。デバッガは、状態レジスタをスキャンしてプロセッサの現在の状態を決定する。デバッガが、プロセッサが電力崩壊が原因で停止されたと決定すると、デバッガは、通常は4ミリ秒以内に、デバッグレジスタ、ETMレジスタ、ETBレジスタ、またはそれらの任意の組合せを復元する。デバッガは、レジスタが復元されるとプロセッサを再始動する。

(もっと読む)

情報処理装置及びプログラム

【課題】制御プログラムの動作検証を行い、リソースへの不適切なアクセスを検出する情報処理装置を提供する。

【解決手段】情報処理装置は、制御プログラム実行するCPUシミュレータ301がリソースにアクセスする場合、当該リソースを特定する情報及び当該アクセス種別がデータの読み込みであるか書き込みであるかを示す情報を含むアクセス情報を出力するシミュレータ部101と、アクセス情報を受け取り、各リソースに対するアクセス種別の履歴を示す履歴パターン情報を保存する履歴情報保存部106と、履歴情報保存部106がアクセス情報を受け取ることにより、当該アクセス情報のリソースを特定する情報が示すリソースの履歴パターン情報を更新すると、当該リソースの履歴パターン情報と、検出パターン情報を比較することで、検出パターン情報が示すアクセス種別の時間順序でのリソースへのアクセスを検出する検出部108と、を備えている。

(もっと読む)

41 - 50 / 1,742

[ Back to top ]