国際特許分類[G06F7/76]の内容

物理学 (1,541,580) | 計算;計数 (381,677) | 電気的デジタルデータ処理 (228,215) | 取扱うデータの順序または内容を操作してデータを処理するための方法または装置 (915) | データ内容から独立して定められたルールによるデータの再配置,並べ替え,または選別のための装置 (42)

国際特許分類[G06F7/76]の下位に属する分類

国際特許分類[G06F7/76]に分類される特許

21 - 30 / 41

組み込み制御装置

【課題】浮動小数点数形式のデータによる演算精度を確保し、且つ、記憶装置の記憶領域の不足を回避することができる組み込み制御装置を提供する。

【解決手段】本発明による組込み制御装置によると、浮動小数点数形式の離散的データを読み取り専用記憶装置に格納するとき、浮動小数点数形式の離散的データを、仮数部短縮型浮動小数点数形式のデータに変換してから格納する。ここに、仮数部短縮型浮動小数点数とは、浮動小数点数の仮数部のうち下位ビットを削除したものである。更に、離散的データから補間演算を行うとき、読み取り専用記憶装置に格納された仮数部短縮型浮動小数点数形式の離散的データを浮動小数点数形式の離散的データに戻してから、補間演算を行う。

(もっと読む)

単精度浮動小数点データの格納方法およびプロセサ

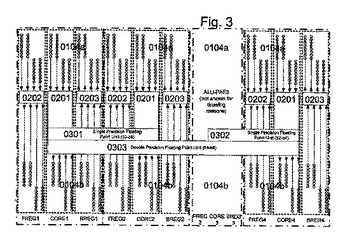

【課題】単精度浮動小数点データおよび倍精度浮動小数点データを扱うプロセサにおいて、新しい単精度浮動小数点データの格納方式を提案し、バイパス機能のための依存関係検出回路を構成するハードウェア量を可能な限り低減すること。

【解決手段】倍精度浮動小数点データを格納可能な大きさを有する、倍精度浮動小数点データと単精度浮動小数点データとが格納されるレジスタを備えるプロセサにおいて、単精度浮動小数点データ処理が指定された場合、前記レジスタの上位半分に入力した単精度浮動小数点データを書き込むとともに、前記レジスタの下位半分にオールゼロを書き込む、単精度浮動小数点データ格納方式。

(もっと読む)

リコンフィギュラブルな浮動小数点レベルおよびビットレベルのデータ処理ユニット

リコンフィギュラブルなデータ処理ユニットの複数の固定小数点ユニットのブロックが、該ブロック内に固定実装された共通の同じハードウェアによって、浮動小数点数を効率的に演算する機能を支援する。  (もっと読む)

(もっと読む)

マイクロコントローラ及び制御システム

【課題】浮動小数点演算を行うためのプログラムコード、特にその変数によるコード量の増加を抑制し、また、固定小数点データを浮動小数点データに変換するための処理オーバヘッドを軽減する。

【解決手段】制御システムに、固定小数点データとして整数データとそれに対する小数点位置データとを入力し、入力データから浮動小数点型の仮数部、指数部及び符号を求めて浮動小数点型データに変換する浮動小数点変換器(32)と、前記浮動小数点変換器の出力を受け浮動小数点データの演算を行う浮動小数点演算器(38)と、を有するマイクロコントローラ(1)を採用する。前記浮動小数点変換器は、前記整数データに対する仮数部のシフト量と前記小数点位置データ(EXP2)との加減算により指数部を取得する。

(もっと読む)

変換装置

【課題】マルチキャリア信号に対して、浮動小数点数から固定小数点数への変換を実行する場合に、信号の値に応じてビット幅の位置を調節したい。

【解決手段】ビット変換部34は、FFT部32から、周波数領域に変換されたマルチキャリア信号であって、かつ浮動小数点数として示されたマルチキャリア信号を入力する。ビット変換部34は、マルチキャリア信号を形成している複数のサブキャリアのそれぞれに対して、最上位のビット位置を特定し、特定した最上位のビット位置をもとに、複数のサブキャリアのそれぞれに対して共通に使用すべきビット幅の位置を決定する。また、ビット変換部34は、決定したビット幅の位置を使用しながら、浮動小数点数から固定小数点数へマルチキャリア信号を変換する。ビット変換部34は、変換したマルチキャリア信号を、固定小数点数の演算を実行する受信処理部38へ出力する。

(もっと読む)

固定小数点表示と浮動小数点表示との間で数を変換するデータ処理装置および方法

【課題】固定小数点表示と浮動小数点表示との間で数を変換するデータ処理装置および方法を提供する。

【解決手段】データ処理装置は、インストラクションを実行するよう動作可能なデータ処理ユニットを備え、そのデータ処理ユニットは、フォーマット変換インストラクションに応答し、数にフォーマット変換演算を適用してその数の固定小数点表示と浮動小数点表示との間で変換を行う。更には、その数の固定小数点表示内の小数点位置を特定するプログラム可能な値を提供する制御フィールドが配置され、データ処理ユニットは、その制御フィールドを参照し、かつプログラム可能な値に従ってフォーマット変換演算を制御する。これによって、単一インストラクションを用いて、小数点の位置がプログラム可能である固定小数点フォーマットと浮動小数点表示との間で直接変換することが可能となる。

(もっと読む)

データ処理装置

【課題】ソフトウェア処理よりも所要時間を短縮でき、しかも複数種類のデータフォーマット変換処理を実行可能な、データ処理装置を得る。

【解決手段】フォーマット変換処理部3は、入力データIDを格納可能な第1入力バッファ10と、出力データODを格納可能な出力バッファ14と、第1入力バッファ10と出力バッファ14との間に接続された変換処理部12と、変換処理部12が参照可能なレジスタ13とを備える。レジスタ13には、所望のデータフォーマット変換に応じて、複数種類の変換パターンCPを設定可能である。変換処理部12は、レジスタ13に設定されている変換パターンCPに従って、入力データIDに基づいて出力データODを生成する。

(もっと読む)

浮動小数点演算のための再構成アレイプロセッサ

【課題】既存の整数演算用PEを利用している従来の再構成アレイプロセッサとほぼ類似したハードウェアのサイズを有しつつも、浮動小数点演算(floating point operation)を比較的速く行うことができ、低電力であり、かつ性能対価格の高特性を有する再構成アレイ(reconfigurable array)プロセッサ、及びそのプロセッサを含んだマルチメディア・プラットホームである。

【解決手段】浮動小数点演算を行うためのプロセッサは浮動小数点演算を行うことができるように配されたプロセッシング要素アレイを含む。各プロセッシング要素は、2つの入力値を受け、入力値に対する整数演算を行う演算装置を含む。該アレイ内のプロセッシング要素は、浮動小数点演算のために、2つ以上のグループに共に連結される。

(もっと読む)

計算装置及び計算プログラム

【課題】従来と比較して装置の大型化を防ぎつつ、計算誤差の有無を判断する。

【解決手段】関数電卓1は、演算桁数「n」を記憶する演算桁数格納領域62と、ユーザ操作に基づいて数値計算式を入力する入力部20と、数値計算式を演算桁数「n」で計算する十進演算器70と、入力された数値計算式に含まれる各計算数値の仮数部の桁数が演算桁数「n」以下であるか否かに基づいて、当該各計算数値中の誤差の有無を判別し、何れかの計算数値が誤差有りと判別された場合に、十進演算器70による計算結果が誤差有りであると判別するCPU40と、十進演算器70による計算結果及びCPU40による判別結果を表示する表示部30と、を備える。

(もっと読む)

3項入力の浮動小数点加減算器

【課題】演算過程で無限の精度をもって演算した後丸めを行った場合と同一の結果を得ることができる3項入力の浮動小数点加減算器を提供する。

【解決手段】入力される3項の指数の大きさが最大の仮数、中間の仮数、最小の仮数に振り分け、指数の大きさが中間の仮数と最小の仮数とをそれぞれ2n+3ビット幅で右シフトして桁合わせを行った仮数と最大の仮数とを出力する前処理回路100と、前処理回路100からの3項の仮数を2項に減らす桁上げ保存加算器(CSA)101と、2項になった仮数の加算を行う桁上げ先見加算器(CLA)102と、最上位ビットが1になるように左シフトする正規化回路103と、上位からn+3ビット目を新たなStickyビットとし、それより下位のビットとの論理和を取って丸めを行う丸め処理回路104と、最終的な指数を出力する指数演算器100とを備える。

(もっと読む)

21 - 30 / 41

[ Back to top ]