国際特許分類[G11C11/4091]の内容

物理学 (1,541,580) | 情報記憶 (112,808) | 静的記憶 (17,688) | 特定の電気的または磁気的記憶素子の使用によって特徴づけられたデジタル記憶装置;そのための記憶素子 (6,432) | 電気的素子を用いるもの (5,515) | 半導体装置を用いるもの (5,114) | トランジスタを用いるもの (5,110) | リフレッシングまたは電荷再生,すなわちダイナミック・セル (3,594) | 周辺回路,例.アドレス用,デコード用,駆動用,書込み用,検出用,または同期用 (1,832) | 電界効果型のメモリ・セル用の周辺回路,例.アドレシング,復号化,駆動,書込み,検知または同期用 (1,832) | 読出し−書込み回路 (638) | センスまたはセンス/リフレッシュ増幅器,またはセンス関連回路,例.ビット・ライン対のプリチャージ,イコライズ,または分離 (191)

国際特許分類[G11C11/4091]に分類される特許

1 - 10 / 191

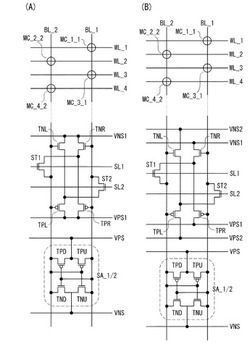

半導体メモリ装置およびその駆動方法

【課題】従来のDRAMでは微細化と共にデータの読み出しエラーが発生しやすくなる。

【解決手段】第1のビット線BL_1の微弱な電位の変動はNチャネル型トランジスタTNRとPチャネル型トランジスタTPRで構成される第1のインバータで反転され、第1のスイッチである第1の選択トランジスタST1を介して、第2のビット線BL_2に出力される。第2のビット線BL_2の電位は、第1のビット線BL_1の電位とは反転した電位であるため、第1のビット線BL_1と第2のビット線BL_2の電位差は拡大する。この拡大した電位差を公知のセンスアンプSA_1/2あるいは、第2のインバータ(Nチャネル型トランジスタTNLとPチャネル型トランジスタTPLで構成される)と第1のインバータで構成されるフリップフロップ回路等で増幅する。

(もっと読む)

半導体記憶装置

【課題】低電圧駆動時における動作完了直後のビット線のプリチャージ電圧復帰するまでの時間を高速化し、読み取りエラーを防止する。

【解決手段】メモリセルBLCELL<0>、BLCELL<1>と、メモリセルのビット線対bl/blbと、ビット線対の電位差を増幅するセンスアンプ回路BLSAと、センスアンプ回路BLSAのグローバルビット線対gbl/gblbと、を有する半導体記憶装置である。センスアンプ回路BLSAは、Pチャネル型MOS電界効果トランジスタP1及びP2と、Nチャネル型MOS電界効果トランジスタN1〜N6と、を含むSRAM型であり、該SRAMの接続ノードa及び接続ノードbに専用のイコライズ線eqcを設けることによって、各駆動信号線に分布する寄生容量を分散させる。

(もっと読む)

半導体記憶装置

【課題】センス動作のマット間でのノイズマージン差をなくすことを可能にした半導体記憶装置を提供する。

【解決手段】メモリセルを含む複数のマットと、複数のマットのうち、隣り合う2つのマットの間に設けられ、隣り合う2つのマットのそれぞれに設けられたビット線と接続されるセンスアンプ回路と、複数のマットのうち、端に配置されたマットに設けられたダミービット線と、端に配置されたマットに設けられたビット線に印加される電位に対応して、ダミービット線に印加する電位を制御する制御回路とを有する。

(もっと読む)

半導体装置

【課題】オーバドライブ時間を変更せずに、センスアンプ列の過昇圧の発生を回避する。

【解決手段】半導体装置は、複数のセンスアンプ列に対応するオーバドライブ配線23−1と、オーバドライブ配線に一端が接続される第1の容量素子61−1と、オーバドライブ配線に第1のスイッチ62−1を介して一端が接続される第2の容量素子61−2と、オーバドライブ配線に対する第1の電圧の供給及び供給停止を制御する第2のスイッチ27−1と、複数のセンスアンプ列の活性化を制御するとともに、第1のスイッチ及び第2のスイッチを制御する制御部とを備える。

(もっと読む)

半導体装置

【課題】半導体装置のアンプ領域は、回路素子のサイズよりも各種の配線のための領域が広い状態となっており、半導体装置のチップサイズを削減する際の妨げになっている。そのため、アンプ領域を縮小し、チップサイズの削減を実現する半導体装置が、望まれる。

【解決手段】半導体装置は、其々に対応するデータを保持する複数のメモリセル、及び、複数のメモリセルのデータを第1の電圧に基づいて其々増幅する複数のセンスアンプ、を含む第1の領域と、第1の電圧を第2の電圧に基づいて発生する第1の電源生成回路を含み、第1の領域の一辺に沿って設けられた第2の領域と、を備えている。さらに、第2の電圧は、第1の領域上を、第1の領域の一辺に平行な第1の方向に延在する第1の電源配線を経由して第1の電源生成回路に供給される。

(もっと読む)

スイッチトランジスタを有しない差動センス増幅器

【課題】回路全体の面積を増やし、製造コストを押し上げるため、センス増幅器に使用される面積を最小限に抑える技術を提供する。

【解決手段】第1のビットライン(BL)に接続された出力と第2のビットライン(/BL)に接続された入力を有する第1のCMOSインバータと、第2のビットライン(/BL)に接続された出力と、第1のビットライン(BL)に接続された入力を有する第2のCMOSインバータと、第1のビットラインおよび第2のビットラインをそれぞれ第1のグローバルビットラインおよび第2のグローバルビットラインに接続するように配列された一対のパスゲートトランジスタを有し、それぞれのCMOSインバータはプルアップトランジスタM21、M22およびプルダウントランジスタM31、M32を備え、パスゲートトランジスタは、プルアップトランジスタ又はプルダウントランジスタによって構成される。

(もっと読む)

低電圧用半導体メモリ装置の駆動方法

【課題】ブリード電流の発生を防止し、プリチャージ動作の電力消費を節減する。

【解決手段】オープンビットライン構造を有する半導体メモリ装置の駆動方法において、第1セルアレイ300aに設置されている第1ビットラインにデータ信号を出力するデータ伝送ステップと、第2セルアレイ300bに設置されている第2ビットラインに基準信号を出力する基準信号伝送ステップと、第1ビットライン及び第2ビットラインのうち、電圧の低い方のビットラインの電圧を接地電圧に増幅して維持する補助センシングステップと、第1センスアンプノード及び第2センスアンプノードの電圧を等価化し、フローティングさせるプリチャージステップとを含み、センシングステップ動作を、接地電圧より低いレベルの低電圧、及び電源電圧よりも高いレベルの高電圧を用いて実行し、低電圧が第1ビットライン及び前記第2ビットラインに伝送されないようにクランピングする。

(もっと読む)

半導体装置

【課題】リフレッシュ動作時に消費電流量を低減する半導体装置を提供する。

【解決手段】ビット線(BL、/BL)と、電源線(SA電源線)を有し、電源線に供給される電圧を用いてビット線の電位を増幅させるセンスアンプ(SA)と、アクティブコマンドが入力されたことに応じて活性化した時には、アクティブコマンドに対応する電圧供給期間の最初の所定期間にオーバードライブをして電源線に第1の電圧(第1電源線LVOD_kの電圧)を供給して、所定期間後に第1の電圧よりも低い第2の電圧(第2電源線LVARY_kの電圧)を供給し、一方、リフレッシュコマンドが入力されたことに応じて活性化した時には、オーバードライブをすることなくリフレッシュコマンドに対応する電圧供給期間の最初から電源線に第2の電圧を供給する電源電圧発生回路と、を備える。

(もっと読む)

ローカル列デコーダに関連付けられた互い違いに配置されたセンスアンプを有する半導体メモリ

【課題】本発明は、少ししか列アドレスバスを必要としない半導体メモリを提供する。

【解決手段】本発明は、半導体メモリであって、ビット線と、メモリセルアレイと、少なくとも1組のセンスアンプバンクであって、各センスアンプは、交互の配列により、対応するビット線に接続されていることによって、ビット線と平行な各センスアンプバンクの組で利用可能なスペースに相互接続することを備え、各センスアンプバンクは、センスアンプバンクの少なくとも1つのセンスアンプを選択する、少なくとも1つのローカル列デコーダを備え、前記ローカル列デコーダは、ビット線と平行な利用可能な相互接続スペース内に走っている出力線によってセンスアンプバンクの少なくとも1つのセンスアンプと電気的に結合されたことを特徴とする半導体メモリに関するものである。

(もっと読む)

半導体記憶装置

【課題】リフレッシュ動作時の消費電流を減少させること。

【解決手段】タイミングチャート100では、WL0のリフレッシュ動作時に、メモリバンク101のSA00とメモリバンク102のSA10をオーバードライブさせ、メモリバンク103のSA20とメモリバンク104のSA30をオーバードライブさせない。タイミングチャート100では、WL1のリフレッシュ動作時に、メモリバンク101のSA00とメモリバンク103のSA20をオーバードライブさせ、メモリバンク102のSA10とメモリバンク104のSA30をオーバードライブさせない。タイミングチャート100では、WL2のリフレッシュ動作時にメモリバンク101のSA00とメモリバンク104のSA30をオーバードライブさせ、メモリバンク102のSA10とメモリバンク103のSA20をオーバードライブさせない。

(もっと読む)

1 - 10 / 191

[ Back to top ]