国際特許分類[H01L21/768]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 1つの共通基板内または上に形成された複数の固体構成部品または集積回路からなる装置またはその特定部品の製造または処理;集積回路装置またはその特定部品の製造 (40,275) | グループ21/70で限定された装置の特定部品の製造 (8,583) | 装置内の別個の構成部品間に電流を流すため使用する相互接続を適用するもの (5,422)

国際特許分類[H01L21/768]に分類される特許

1,121 - 1,130 / 5,422

窒素ドープされたアモルファスカーボンハードマスク

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

半導体装置の製造方法

【課題】ゲート電極と第1のコンタクトプラグとが接触する接触幅を充分に確保する。

【解決手段】半導体基板10の上に、エッチングストッパー膜17、第1の層間絶縁膜18及び第2の層間絶縁膜19を順次形成する。次に、第1,第2の層間絶縁膜18,19を貫通し、且つ、エッチングストッパー膜17を露出する第1のホール23を形成する。次に、酸素ガスを含むプラズマを用いたプラズマ処理により、第2の層間絶縁膜19における第1のホール23の側壁に露出する部分を変質して、第1の変質層25を形成する。次に、第1の変質層25を除去して、第2のホール27を形成する。次に、エッチングストッパー膜17における第2のホール27に露出する部分を除去して、第1のコンタクトホール29を形成する。次に、第1のコンタクトホール29に、第1のコンタクトプラグ32Aを形成する。

(もっと読む)

ミクロスケール構造中でのシード層堆積

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

光電変換装置及びその製造方法

【課題】 層間絶縁膜の厚膜化を抑制しつつ、周辺回路領域の配線層数を増加させることのできる光電変換装置を提供する。

【解決手段】 画素領域と、画素領域よりも多くの配線層を有する周辺回路領域とが配された半導体基板と、半導体基板の上部に配された配線部とを有する光電変換装置において、配線部は、第1の配線層と接続する第1の層間絶縁膜に配されたプラグを周辺回路領域に有し、第1の配線層よりも上部に配された第2の配線層と接続する第1の層間絶縁膜に配されたプラグと第2の層間絶縁膜に配されたプラグとを画素領域に有し、

半導体基板に最も近接して配された配線層は、周辺回路領域において第1の配線層であり、画素領域において第2の配線層である。

(もっと読む)

半導体デバイス及びその製造方法

本願は、半導体デバイス及びその製造方法に関するものである。本発明の半導体デバイスの製造方法は、半導体基板を提供する工程と、半導体基板に、該半導体基板に形成されたゲート絶縁層及び該ゲート絶縁層に形成された犠牲ゲートを含むゲート領域と、ソース/ドレイン領域とを含むトランジスタ構造を形成する工程と、第1の層間絶縁層を堆積し、犠牲ゲートを露出させるように該第1の層間絶縁層に対して平坦化を行う工程と、犠牲ゲートを除去して、リプレースメントゲートホールを形成する工程と、第1の層間絶縁層におけるソース/ドレイン領域に対応する位置に、第1のコンタクトホールを形成する工程と、第1のコンタクトホール及びリプレースメントゲートホールに第1の導電材料を充填して、ソース/ドレイン領域に接触する第1のコンタクト部と、リプレースメントゲートとを形成する工程とを含む。本発明によれば、リプレースメントゲートと第1のコンタクト部は、同一の工程で同じ材料を堆積して形成することができるため、製造プロセスを簡単化できた。  (もっと読む)

(もっと読む)

電界効果トランジスタを形成するための方法および電界効果トランジスタ・デバイス

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

半導体デバイス障壁層

【課題】本発明は、半導体デバイス要素のメタライゼーション及び誘電体材料の不活性化に使用される障壁層に関する。

【解決手段】半導体デバイスメタライゼーション要素用の障壁層は、要素くぼみ中に形成されたシリコン窒化物薄膜とシリコン窒化物薄膜上に形成された耐熱性金属薄膜を供する。デバイス要素は誘電体材料及び誘電体中に形成されたくぼみを含む。くぼみ内の誘電体材料の表面は、制御されたパラメータ下で窒素に露出される。くぼみの内部に隣接した誘電体材料の部分は、シリコン窒化物に変換される。

耐熱性金属は次に、くぼみの側壁に沿って、適合して堆積される。次に、耐熱性金属薄膜上にシード層が堆積され、次にくぼみ内に導電性金属が堆積される。次に、くぼみの外の過剰の金属を除去し、デバイスを平坦化するため、デバイスを研磨する。

(もっと読む)

洗浄組成物及び半導体装置の製造方法

【課題】配線構造や層間絶縁構造を損傷することなく、半導体基板上のプラズマエッチング残渣を十分に除去しうる洗浄組成物、及び前記洗浄組成物を用いた半導体装置の製造方法を提供すること。

【解決手段】57〜95重量%の(成分a)水、1〜40重量%の(成分b)第2級水酸基及び/又は第3級水酸基を有するヒドロキシ化合物、(成分c)有機酸、並びに、(成分d)第4級アンモニウム化合物、を含有し、pHが5〜10であることを特徴とする、半導体基板上に形成されたプラズマエッチング残渣除去用の洗浄組成物、並びに、前記洗浄組成物により、半導体基板上に形成されたプラズマエッチング残渣を洗浄する工程を含む、半導体装置の製造方法。

(もっと読む)

絶縁膜および半導体装置

【課題】誘電率の低い絶縁膜であって、半導体装置の製造においてCMP法により当該絶縁膜上の膜を好適に除去することができるとともに、キャップ層を備えておらず、かつ、信頼性に優れた半導体装置の製造に好適に用いることができる絶縁膜を提供すること。

【解決手段】本発明の絶縁膜は、分子内に、アダマンタン型のかご型構造を含む部分構造と、重合反応に寄与する重合性反応基とを有する重合性化合物および/または当該重合性化合物が部分的に重合した重合体を含む組成物を用いて形成された絶縁膜であって、0.03〜20μmの膜厚を有し、ナノインデンターを用いて、膜厚の2分の1以上の最大押し込み深さにおいて、弾性率測定変位を膜厚の10分の1とする測定から求められる弾性率が、4.0GPa以上であることを特徴とする。

(もっと読む)

半導体装置及びその製造方法

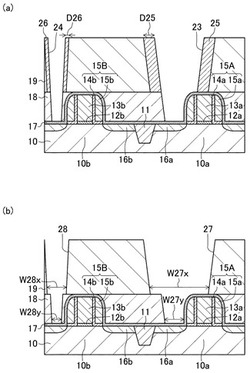

【課題】深さの異なるコンタクトホールを同時に形成することを可能とした半導体装置を提供する。

【解決手段】第1の溝部7内に形成された第1の埋め込み配線11と、第2の溝部12内に形成された第2の埋め込み配線14と、第1の埋め込み配線11上に第1のコンタクトプラグ24が形成される第1のコンタクト形成領域23と、第2の埋め込み配線14上に第2のコンタクトプラグ26が形成される第2のコンタクト形成領域25とを備え、第1のコンタクト形成領域23の上面23aが第1の埋め込み配線11の上面11aよりも高い位置にあり、第2のコンタクト形成領域25の上面25aが第2の埋め込み配線14の上面14aと同じかそれよりも高い位置にあり、第1のコンタクト形成領域23の上面23aが第2のコンタクト形成領域25の上面25aと同じかそれよりも高い位置にある。

(もっと読む)

1,121 - 1,130 / 5,422

[ Back to top ]