国際特許分類[H01L21/768]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 1つの共通基板内または上に形成された複数の固体構成部品または集積回路からなる装置またはその特定部品の製造または処理;集積回路装置またはその特定部品の製造 (40,275) | グループ21/70で限定された装置の特定部品の製造 (8,583) | 装置内の別個の構成部品間に電流を流すため使用する相互接続を適用するもの (5,422)

国際特許分類[H01L21/768]に分類される特許

1,091 - 1,100 / 5,422

半導体装置の製造方法

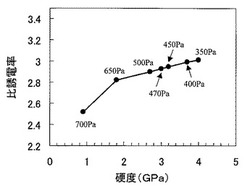

【課題】有機シロキサン系絶縁膜を用いて電気的特性に優れた半導体装置を製造する方法を提供する。

【解決手段】下層配線の上にこの順で形成された第1〜第3の絶縁膜をドライエッチングして該下層配線に至る開口部を形成し、該開口部の内面と該第3の絶縁膜の上にバリアメタル膜を形成し、該バリアメタル膜の上に該開口部を埋める導電層を形成し、該第3の絶縁膜上の該導電層と該バリアメタル膜、及び該第2、第3の絶縁膜の一部を除去し該下層配線に電気的に接続する上層配線を形成し、露出した該第2の絶縁膜と該導電層の表面を還元性プラズマ処理し、

該第2の絶縁膜は下記式で表されるアルキルアルコキシシランと非酸化性ガスとを用い、500Pa以下でプラズマCVD法により形成する

RwSixOy(OR´)z

R及びR´はCH3、wxzは正の整数、yは0または正の整数、(w/x)=2である。

(もっと読む)

空隙組込みの構造体及び方法

【課題】 空隙を組み込んだ構造体及びその形成方法を提供する。

【解決手段】 VLSI及びULSI用の空隙含有金属・絶縁体相互接続構造体を、光パターン化可能低k材料を用いて作成する方法、及び形成した空隙含有金属・絶縁体相互接続構造体を開示する。より具体的には、本明細書で説明する方法は、内部に種々異なる深さの空隙がフォトリソグラフィにより画定された光パターン化可能低k材料の内部に構築される相互接続構造体を提供する。本発明の方法においては、空隙を形成するのにエッチ・ステップは必要としない。光パターン化可能低k材料内部の空隙を形成するのに、エッチ・ステップを必要としないで、本発明において開示する方法は、高信頼性の相互接続構造体を提供する。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】記憶素子の下にあるコンタクトプラグの上面の平坦性を改善し、信頼性の高い半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、半導体基板と、半導体基板上に設けられた複数のスイッチングトランジスタと、隣接する2つのスイッチングトランジスタ間に埋め込まれ、該隣接する2つのスイッチングトランジスタの各ゲートから絶縁されかつ該隣接する2つのスイッチングトランジスタのソースまたはドレインに電気的に接続され、上面がスイッチングトランジスタの上面よりも高い位置にあるコンタクトプラグと、コンタクトプラグの上面上に設けられ、データを記憶する記憶素子と、記憶素子上に設けられた配線とを備えている。

(もっと読む)

低k誘電体と導電材料との接着改善

【課題】銅ダマシン配線上への誘電体層の形成において、導電材料と誘電体層間の密着性を向上する半導体装置の製造方法を提供する。

【解決手段】オルガノシロキサンからなる第2誘電体層118に、TaNからなる金属バリア層124とCuからなる導電性金属特徴部126を形成する。平坦化後アンモニアプラズマ処理還元により表面の酸化物を除去する。連続して真空を破壊せずに、トリメチルシランからなる有機ケイ素化合物を導入し、プラズマプロセスによりSiCN膜130を形成し、さらに連続してSiC膜132を堆積する。酸化物の除去から誘電体層の形成までインサイチュで行うことが可能である。

(もっと読む)

半導体集積回路装置および半導体集積回路装置の製造方法

【課題】TSVを形成した後の工程においては、Cuの拡散防止膜である絶縁膜形成後に、当該絶縁膜に割れが発生し、その後のエッチングやアッシングなどのパターン加工を行う工程において、露出したCuが変色する問題が発生する場合がある。これは、拡散防止膜の成膜工程における熱履歴によりCuが体積膨張したことが問題の要因と考えられる。このような、膜割れが発生した場合には、Cu拡散防止膜の機能破壊、TSV上部のCuの酸化による上部配線との導通不良等の種々の問題を誘発する。

【解決手段】本願の一つの発明は、貫通電極を有する半導体集積回路装置において、プリメタル配線層形成よりも後に貫通ビアを形成する場合において、貫通電極の上端に当たる層間絶縁膜の界面に、メタル拡散防止絶縁膜として、窒化シリコン系絶縁膜を使用し、それ以外の層間絶縁膜の界面に、メタル拡散防止絶縁膜として、炭化シリコン系の絶縁膜を使用するものである。

(もっと読む)

半導体装置およびその製造方法

【課題】吸湿性の高い絶縁膜を使用してもコンタクト又は配線の劣化を抑制することができる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置の製造方法は、基板10上に第1の絶縁膜15を形成する工程(a)と、第1の絶縁膜15にホール24を形成する工程(b)と、ホール24の側壁上に、第1の絶縁膜15よりも水分を通しにくい第2の絶縁膜17を形成する工程(c)と、工程(c)の後、ホール24に導電体30を埋め込むことにより、プラグ19を形成する工程(d)とを備えている。

(もっと読む)

半導体集積回路装置およびその製造方法

【課題】多層配線構造を使って、キャパシタンスが大きく、かつキャパシタンス値が安定なキャパシタ素子を半導体基板上に集積化する。

【解決手段】多層配線構造18は、少なくとも第1層目の層間絶縁膜16と、第1層目の層間絶縁膜中に埋設された第1配線層と、を含み、第1配線層は、第1の電源に接続され前記第1の層間絶縁膜中に埋設された第1の配線パタ―ン15C1と、第2の電源に接続され前記第1の層間絶縁膜中に埋設された第2の配線パタ―ン15C2と、を含み、第1の配線パタ―ンと前記第2の配線パタ―ンとは容量結合して第1のキャパシタを形成し、第1の配線パタ―ンは積層配線パタ―ン13C上に形成されて、前記第4の電極パターン13Gと容量結合して第2のキャパシタを形成し、第4の電極パターンは第2の配線パタ―ンに電気的に接続されている。

(もっと読む)

基板の製造方法、半導体装置の製造方法、電気光学装置

【課題】任意の方向に傾斜した開口部を形成可能な基板の製造方法、半導体装置の製造方法、およびこれを適用した半導体装置を備えた電気光学装置を提供すること。

【解決手段】本適用例の素子基板101の製造方法は、素子基板101上に設けられた半導体装置としてのTFT110を覆うと共に第1開口部としての孔104aが設けられた第2絶縁膜としての層間絶縁膜104をマスクとして、素子基板101の面法線101aと交差する一の方向からドライエッチングを第1絶縁膜としてのゲート絶縁膜103に施して、孔104aに連通すると共にTFT110のドレイン電極110dに開口する第2開口部としての孔103aを形成する。

(もっと読む)

薄膜のパターニング方法及び表示パネルの製造方法

【課題】コンタクトホールをより微細に形成することができる薄膜のパターニング方法及び表示パネルの製造方法を提供する。

【解決手段】所定の段差部を有した絶縁層25を形成する工程と、スパッタ法により前記段差部を覆うようにして前記絶縁層25上に犠牲層28を成膜する工程と、前記段差部に対応する領域における前記犠牲層28のうちの少なくとも一部の除去と、前記除去により前記犠牲層28から露出された領域における前記絶縁層25の除去とを、ドライエッチングにより連続して行う工程と、前記ドライエッチングで残存した前記犠牲層28の少なくとも一部をウェットエッチングにより除去する工程と、を有する。

(もっと読む)

配線構造、表示装置、および半導体装置

【課題】Cu系合金配線膜と半導体層との間に通常設けられるバリアメタル層を省略しても優れた低接触抵抗を発揮し得、さらに密着性に優れた配線構造を提供する。

【解決手段】本発明の配線構造は、基板の上に、基板側から順に、半導体層と、Cu合金層とを備えた配線構造であって、前記半導体層と前記Cu合金層との間に、基板側から順に、窒素、炭素、フッ素、および酸素よりなる群から選択される少なくとも一種の元素を含有する(N、C、F、O)層と、CuおよびSiを含むCu−Si拡散層との積層構造を含んでおり、前記(N、C、F、O)層を構成する窒素、炭素、フッ素および酸素のいずれかの元素は前記半導体層のSiと結合しており、前記Cu合金層は、Cu−X合金層(第一層)と第二層とを含む積層構造である。

(もっと読む)

1,091 - 1,100 / 5,422

[ Back to top ]