国際特許分類[H01L21/768]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 1つの共通基板内または上に形成された複数の固体構成部品または集積回路からなる装置またはその特定部品の製造または処理;集積回路装置またはその特定部品の製造 (40,275) | グループ21/70で限定された装置の特定部品の製造 (8,583) | 装置内の別個の構成部品間に電流を流すため使用する相互接続を適用するもの (5,422)

国際特許分類[H01L21/768]に分類される特許

1,061 - 1,070 / 5,422

配線回路基板及びその製造方法

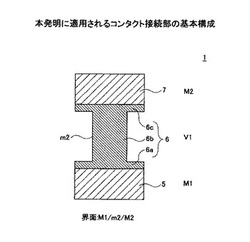

【課題】配線回路基板において、コンタクト抵抗の上昇を抑制し、熱応力による断線を防止することのできるコンタクト構造を提供する。

【解決手段】 配線回路基板は、第1配線層(5)、第2配線層(7)、及び前記第1配線層と前記第2配線層を電気的に接続するコンタクト配線(6)を有する。前記コンタクト配線は、前記第1配線層のコンタクト面を被覆する第1被覆部(6a)と、前記第2配線層のコンタクト面を被覆する第2被覆部(6c)と、前記第1被覆部と前記第2被覆部の間に延びるプラグ部(6b)を有する。前記第1被覆部、前記プラグ部、及び前記第2被覆部は、同一の導電性材料で一体的に形成された内部に界面のないコンタクト配線である。

(もっと読む)

半導体装置とその製造方法

【課題】 相互接続配線とその上方のキャップ層との接着力を向上することが可能な半導体装置とその製造方法を提供する。

【解決手段】 半導体基板101上の誘電体層305中にその上面に自然酸化膜を含む金属の相互接続配線310を形成し、誘電体層及び前記金属の相互接続配線の少なくとも一部を覆いマンガン原子又はイオンを含む第1のキャップ層405を形成し、第1のキャップ層405上に絶縁体である第2のキャップ層410形成し、自然酸化膜及び第1のキャップ層は、第1のキャップ層と相互接続配線との間に酸化マンガンを形成するために反応する。

(もっと読む)

半導体装置

【課題】MEMSキャパシタとその制御用集積回路を反りの抑えられた1枚の基板上に有する半導体装置を提供する。

【解決手段】貫通孔を含む貫通孔領域を有する基板と、前記基板の上方のMEMSキャパシタと、前記MEMSキャパシタの下方の前記MEMSキャパシタの制御用集積回路とを有する半導体装置を提供する。前記制御用集積回路は、前記基板上のトランジスタを含む。前記MEMSキャパシタの真下の前記基板上の領域と前記貫通孔領域とは、少なくとも一部において重なる。

(もっと読む)

半導体装置及びその製造方法

【課題】下層の金属配線のダメージがなく上層の金属配線が形成され、かつ、配線間の寄生容量が低減された半導体装置及びその製造方法を提供する。

【解決手段】本発明に係る半導体装置は、半導体基板上に設けられた第1の金属配線層と、

前記第1の金属配線層上に設けられ、該第1の金属配線層の金属の拡散を防止する拡散防止膜と、前記拡散防止膜上に設けられた第1の絶縁膜と、前記第1の絶縁膜上に設けられた、前記拡散防止膜と同じ材料からなる第2の絶縁膜と、前記第2の絶縁膜上に設けられた第3の絶縁膜と、前記拡散防止膜、前記第1の絶縁膜、前記第2の絶縁膜及び前記第3の絶縁膜に形成された接続孔に充填され、前記第1の金属配線層に電気的に接続された第2の金属配線層と、を備えたことを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】ビット線材料埋設体の形状のばらつきに起因するビット線の配線抵抗値のばらつきを防ぐ半導体装置の製造方法を提供する。

【解決手段】製造方法は、第一溝4内に第一のビット線材料埋設体6および第二のビット線材料埋設体10からなるビット線11を形成する第一工程と、ビット線11に含まれる不純物を拡散させて第一不純物拡散領域13を形成する第二工程と、ピラー部1bを形成する第三工程と、ピラー部1bに対向する配線17を第二溝15内に形成する第四工程と、ピラー部1bの先端部に、第二不純物拡散領域19を形成する第五工程と、を具備し、第一工程が、第一溝4を完全に埋め込むように第一ビット線材料を形成した後に第一ビット線材料表面を平坦化し、第一溝4底部に残るように第一ビット線材料をエッチバックする工程を具備する。

(もっと読む)

半導体装置の製造方法

【課題】安定した形状の信頼性の高いエアギャップを効率良く形成する半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法では、半導体基板上に、ビアホール及びエアギャップ用トレンチを含む複数のホールを有する層間絶縁膜を形成する。次に、エアギャップ用トレンチ内に有機材料を埋め込んだ後、硬化させる。また、ビアホール内にビアプラグを形成する。この後、エアギャップ用トレンチ内に埋め込まれた有機材料を除去することにより、エアギャップを形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明ではフォトリソグラフィー技術解像限界付近のパターン形成を安定して形成すると共に、コンタクトプラグなどの構造物における目合わせずれや接触面積の縮小による接触電気抵抗の増大や接続不良を解決する。

【解決手段】半導体基板上に形成された絶縁材料層100に、第1の方向に延在し、底部の幅W1より上部の幅W2が広い第1の溝101を形成する工程と、第1の溝101内に、溝の上端より低い位置まで埋め込み層102を形成する工程と、埋め込み層102上に露出している第1の溝101の側壁を覆うサイドウォール103を形成する工程と、サイドウォール103をマスクとして埋め込み層102をエッチングして第1の方向に分離する工程と、

を含むことを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】コンタクトホール形成時の重ね合わせずれに起因したリークの増大やコンタクト抵抗の上昇が抑制された半導体装置とその製造方法を提供する。

【解決手段】半導体装置は、半導体基板100と、半導体基板100上にゲート絶縁膜101を介して形成されたゲート電極102と、ゲート電極102の側壁上に形成されたサイドウォールスペーサ150と、半導体基板100のうち、ゲート電極102及びサイドウォールスペーサ150を間に挟んで両側に形成されたソースドレイン領域106と、ゲート電極102、サイドウォールスペーサ150、及び半導体基板100の上面を覆う応力絶縁膜110とを備えている。サイドウォールスペーサ150は、少なくとも中央部のゲート長方向膜厚よりも上部のゲート長方向膜厚の方が大きくなっている。

(もっと読む)

半導体装置およびその製造方法

【課題】SOI基板上に形成されたMOSFETを有する半導体装置の信頼性を向上させる。また、半導体装置の製造工程を簡略化する。

【解決手段】SOI基板SB上に形成された複数のnチャネル型MOSFETQnを有する半導体装置において、BOX膜の下部の支持基板の上面に拡散層であるn+型半導体領域を形成し、n+型半導体領域と電気的に接続され、素子分離領域1を貫くコンタクトプラグCT2を形成することで、支持基板の電位を制御する。SOI基板SBの平面において、各nチャネル型MOSFETQnは第1方向に延在しており、第1方向に複数形成されて隣り合うコンタクトプラグCT2同士の間に配置された構造とする。

(もっと読む)

半導体装置の製造方法

【課題】コンタクトの抵抗値のばらつきを抑え、歩留りを安定させることが可能な半導体装置の製造方法を提供する。

【解決手段】半導体基板上に形成された導電層上に、絶縁膜を形成し、ハロゲンガスを含む第1のガスを用いて絶縁膜をドライエッチングして、導電層の表面を露出させ、露出した導電層に対しハロゲンガスを還元可能な第2のガスを用いて第1のプラズマ処理を行い、露出した導電層に対しC元素及びO元素を含みハロゲン元素を含まない第3のガスを用いて、第2のプラズマ処理を行う。

(もっと読む)

1,061 - 1,070 / 5,422

[ Back to top ]