国際特許分類[H01L21/8236]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 1つの共通基板内または上に形成された複数の固体構成部品または集積回路からなる装置またはその特定部品の製造または処理;集積回路装置またはその特定部品の製造 (40,275) | 1つの共通基板内または上に形成される複数の固体構成部品または集積回路からなる装置の製造または処理 (31,691) | 複数の別個の装置に基板を分割することによるもの (31,691) | それぞれが複数の構成部品からなる装置,例.集積回路の製造 (31,684) | 基板がシリコン技術を用いる半導体であるもの (27,844) | 電界効果技術 (17,660) | MIS技術 (17,448) | エンハンスメントトランジスタとデプリーショントランジスタの組み合わせ (60)

国際特許分類[H01L21/8236]に分類される特許

1 - 10 / 60

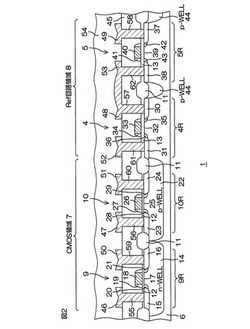

半導体装置および半導体装置の製造方法

【課題】基準電圧発生回路を構成するエンハンスメント型MOSFETとデプレッション型MOSFETとの間の温度特性の差を小さくすることができ、基準電圧発生回路の出力電圧の温度特性を改善することができる半導体装置およびその製造方法を提供する。

【解決手段】半導体基板6上においてRef回路領域8およびCMOS領域7に跨るようにゲート絶縁膜66を形成した後、CMOS領域7の部分を選択的に除去する。次に、熱酸化により、ゲート絶縁膜66が除去されたCMOS領域7に第1ゲート絶縁膜12を形成し、同時に、Ref回路領域8に残っているゲート絶縁膜66を厚くして第1ゲート絶縁膜12よりも厚い第2ゲート絶縁膜13を形成する。

(もっと読む)

半導体装置

【課題】消費電力の増加を招くことなくオフの状態を実現することのできる半導体装置を

提供する。

【解決手段】ゲートに電圧が印加されていない状態でオン状態であるパワー素子と、パワ

ー素子のゲートに第1の電圧を印加するためのスイッチング用の電界効果トランジスタと

、パワー素子のゲートに第1の電圧より低い電圧を印加するためのスイッチング用の電界

効果トランジスタと、を有し、上記スイッチング用の電界効果トランジスタはオフ電流が

小さい半導体装置である。

(もっと読む)

ターンオン防止付き複合半導体デバイス

【課題】ターンオン防止付き複合半導体デバイスを提供する。

【解決手段】本明細書は、ターンオン防止制御を有する複合III-窒化物半導体デバイスの種々の実現を開示する。1つの好適な実現では、ノーマリオフ複合半導体デバイスが、ノーマリオンIII-窒化物パワートランジスタ、及びこのノーマリオンIII-窒化物パワートランジスタとカスコード接続された低電圧(LV)デバイスを具えて、ノーマリオフ複合半導体デバイスを形成する。このLVデバイスは、ノイズを伴う環境内で、ノイズ電流が、ノーマリオンIII-窒化物パワートランジスタのチャネルを通って流れることを防止することによって、ノーマリオフ複合半導体デバイスに、ターンオン防止制御を与えるように構成されている。

(もっと読む)

半導体装置および基準電圧生成回路

【課題】所望の温度特性を有することによって回路規模を小さくできるMOSトランジスタを提供する。

【解決手段】ゲート電極はP型半導体層及びN型半導体層からなるので、P型半導体層とN型半導体層との接合面に、空乏層13が生じる。温度が変化すると、空乏層13の領域の面積が変化し、P型半導体層11及びN型半導体層12の領域の面積もそれぞれ変化することで、MOSトランジスタに所望の温度特性を与えられる。その結果、温度補正回路を簡単にする、あるいは不要にすることができる。

(もっと読む)

半導体装置

【課題】安定した静電気保護機能を有する半導体装置を提供すること。

【解決手段】半導体装置は、シリコン柱を有するシリコン基板、シリコン柱の側壁に沿って形成されたゲート電極、ゲート電極とシリコン柱との間に形成されたゲート絶縁膜シリコン柱の上部に形成された上部拡散層、及びシリコン基板において上部拡散層より下方に形成された下部拡散層、を有する縦型MOSトランジスタと、下部拡散層と電気的に接続されたパッドと、を備える。サージ電圧が印加された際に下部拡散層と基板との間においてブレイクダウンが発生する。

(もっと読む)

半導体集積回路装置

【課題】SOI基板に形成されたMOSトランジスタを含む半導体集積回路装置において、半導体集積回路装置に入力される電源電圧が高い場合であっても、SOI基板のBOX酸化膜やシリコン層を厚くすることなく、回路動作を安定させる。

【解決手段】MOSトランジスタM1〜M9は、シリコン基板、BOX酸化膜及びシリコン活性層を有するSOI基板に形成され、かつ、ソース拡散層の底部及びドレイン拡散層の底部がBOX酸化膜に到達して形成されている。エンハンスメント型PchMOSトランジスタM3,M4、M5,M7は、デプリーション型NchMOSトランジスタM10を介して、電源電圧が入力される電源端子VDDに接続されている。MOSトランジスタM10は、ソース、ゲート及びボディが結線されて定電流源として機能し、ソース電位がシリコン基板電位よりも高くなることで飽和電流が減少する電気的特性をもっている。

(もっと読む)

半導体装置

【課題】従来よりも低消費電力かつ小面積であるとともに設計性のよいパワーオンリセット回路またはスタートアップ回路を備えた半導体装置を提供する。

【解決手段】半導体装置1は、出力部10と、第1および第2の電位設定部8,9とを備える。出力部10は、電源投入時に、中間電位ノードN1の電位に応じた制御信号RSを内部回路3に出力する。第1の電位設定部8は、第1の基準電位ノードVDDと中間電位ノードN1との間に接続された第1の導電型を有するエンハンスメント型の第1のMOSトランジスタEPを含む。第2の電位設定部9は、第2の基準電位ノードGNDと中間電位ノードN1との間に直列接続された第2の導電型を有するディプレッション型の複数の第2のMOSトランジスタDN1_〜DN_nを含む。複数の第2のMOSトランジスタDN1_〜DN_nの各々において、ソースとウェルとが互いに接続される。

(もっと読む)

不揮発性記憶装置およびその製造方法

【課題】閾値電圧の制御性を向上させて形成された複数種類のトランジスタを備える不揮発性記憶装置、および、それに適した製造方法を提供する。

【解決手段】1つの半導体基板2の表面に形成された複数種類のMOSトランジスタを有する不揮発性記憶装置であって、n形のソース領域14およびドレイン領域15と、その間の半導体基板2の表面上に設けられたゲート絶縁膜17と、ゲート電極18と、ゲート絶縁膜17の直下に位置し、n形不純物とp形不純物との両方を含むチャネル領域42と、を有するMOSトランジスタ10と、n形のソース領域24およびドレイン領域25と、その間の半導体基板2の表面上に設けられたゲート絶縁膜27と、ゲート電極28と、ゲート絶縁膜27の直下に位置し、n形不純物の濃度プロファイルがチャネル領域42と同じであるチャネル領域43と、を有するMOSトランジスタ20と、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】製造コスト削減、サイズ縮小ができる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置の製造方法であって、P型Si基板21の主面にトレンチ22を形成することによって、エンハンスメント型FET形成用の幅狭部分とでプレション型FET形成用の幅広部分とを含むアクティブ領域25を形成する工程と、主面の法線に対して30度〜45度の範囲内の注入角で、且つ、注入方向が法線を中心に相対的に回転するように、Si基板21に対してP型不純物を注入して、幅広部分にP型のチャンネルストッパー領域25aを形成すると共に、幅狭部分にP型チャンネル拡散領域25bを形成する工程と、トレンチ22をトレンチ素子分離絶縁層26で埋める工程と、ゲート絶縁膜27を形成する工程と、Si基板21上にN型不純物を注入して第2の部分にN型チャンネル拡散領域28を形成する工程と、ゲート電極29を形成する工程とを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】エンハンスメント型FETとディプレッション型FETとを集積する場合に製造工程数の削減を実現できる半導体装置の製造方法を提供する。

【解決手段】この製造方法は、アクティブ領域11を横断しゲート電極10Aよりも長さが短いゲート電極10Bを形成する工程と、ゲート電極10A,10Bをマスクとして、アクティブ領域11に不純物を斜めイオン注入することにより、ゲート電極10Aのゲート長方向両側の領域に互いに連続しない不純物拡散領域20a,20bを形成するとともに、ゲート電極10Bのゲート長方向両側の一方の領域から他方の領域に亘って連続する不純物拡散領域20g,20hを形成する斜めイオン注入工程とを含む。

(もっと読む)

1 - 10 / 60

[ Back to top ]