国際特許分類[H01L27/04]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 1つの共通基板内または上に形成された複数の半導体構成部品または他の固体構成部品からなる装置 (52,733) | 整流,発振,増幅またはスイッチングに特に適用される半導体構成部品を含むものであり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁を有する集積化された受動回路素子を含むもの (38,321) | 基板が半導体本体であるもの (36,153)

国際特許分類[H01L27/04]の下位に属する分類

複数の個々の構成部品を反復しない形で含むもの (2,326)

1種類の半導体構成部品だけを含むもの (8,288)

複数の個々の構成部品を反復した形で含むもの (15,853)

国際特許分類[H01L27/04]に分類される特許

2,001 - 2,010 / 9,686

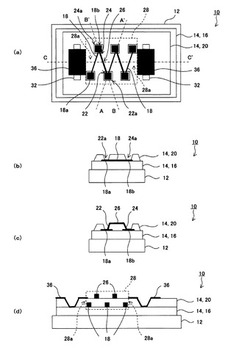

チップ一体型パッケージ、半導体装置

【課題】チップ一体型パッケージ、半導体装置を提供する。

【解決手段】半導体基板12上に積層した絶縁層14と、前記絶縁層14に横倒しに埋め

込んだ態様で形成され、前記半導体基板12に形成された回路または外部回路と電気的に

接続するソレノイド型のインダクタ28と、前記絶縁層14において前記インダクタ28

の両端の開口部28aを塞ぐ位置に埋め込んだ態様で形成した一対の磁性部材(磁性板3

5、磁性膜36、磁性樹脂38)と、を有することを特徴とする。

(もっと読む)

半導体集積回路

【課題】回路設計の余裕を拡大すること。

【解決手段】半導体集積回路100は、トランジスタ124a,124bと、検出回路131と、バイアス生成回路132と、を備えている。トランジスタ124aおよびトランジスタ124bは、基板にバイアスが印加される。検出回路131は、トランジスタ124aおよびトランジスタ124bの閾値電圧を検出する。バイアス生成回路132は、検出回路131による検出結果に基づいてバイアスを生成する。

(もっと読む)

半導体集積回路

【課題】回路部が停止状態から動作状態に移行するときに、チップ内電源に対する電圧降下を低減すること。

【解決手段】動作期間T10で、回路部210内の寄生容量221の電位とデカップリング容量220の電位は、チップ内電源201の電位に維持され、停止期間T11で、寄生容量221の電位は徐々に降下してゼロになり、デカップリング容量220の電位はチップ内電源201の電位に維持される。移行期間T12〜T14で、デカップリング容量220の電位が第2スイッチSW2を介して寄生容量221に充電され、デカップリング容量220の電位は徐々に降下し、寄生容量221の電位は徐々に上昇していく。移行期間T12〜T14で、回路部210の電位がゼロの状態であるときに、回路部210が第1スイッチSW1を介してチップ内電源201と接続しないようにすることで、チップ内電源201に対する電圧降下を低減することができる。

(もっと読む)

半導体集積回路

【課題】順方向基板バイアス電圧をかけたときの、Vthの異なるトランジスタの速度の向上率をほぼ均等にすることのできる半導体集積回路を提供する。

【解決手段】低VthのPMOSトランジスタが形成されるNウェル領域(WN)11へは、基板バイアス供給部VP1から基板バイアスVbsP1を供給し、高VthのPMOSトランジスタが形成されるNウェル領域(WN)12−1、12−2、12−3へは、基板バイアス供給部VP2から基板バイアスVbsP2を供給する。

(もっと読む)

過温度検出回路

【課題】半導体素子の過温度を迅速に検出できる過温度検出回路を提供すること。

【解決手段】過温度検出回路1は、制御部10を備える。制御部10には、スイッチ素子Q1の温度が上昇するに従って低下する電圧が入力される。この制御部10は、入力される電圧に基づいて、スイッチ素子Q1の平均温度の単位時間あたりの変化量を求め、スイッチ素子Q1の平均温度の単位時間あたりの変化量が4.5度以上であれば、スイッチ素子Q1が過温度であると判別する。

(もっと読む)

広帯域ESD保護を与える方法とそれにより得られる回路

【課題】伝送ラインや分布増幅器などの分配電子回路を開示する。

【解決手段】本発明は、インプットターミナル(2)と、アウトプットターミナル(3)と、電力供給ライン(4、5)と、インプットターミナル(2)とアウトプットターミナル(3)との間に設けられ一つのセクションから別のセクションへ電気信号を伝送するように配置された一連セクション(61、62、63、64、65)とを含み、個々のセクション(61、62、63、64、65)は、電子放電静電(ESD)イベントの発生の際に対応するESD電流を電力供給ライン(4、5)に運ぶように構成されたESD保護(9)を含み、個々のセクション(61、62、63、64、65)のESD保護要素(9)は、ESDイベントの発生の際に、最初のセクション(61)の前に後続のセクション(62、63、64、65)が起動されるように選択されている分配電子回路である。

(もっと読む)

半導体装置

【課題】半導体基板の内部での発熱による異常を検知する。

【解決手段】半導体装置は、主活性領域が形成された半導体基板と、半導体基板の温度を検知する第1温度検知素子と、第1温度検知素子よりも半導体基板の深い位置の温度を検知する第2温度検知素子とを備える。第1温度検知素子と第2温度検知素子によって、半導体基板の深さ方向に異なる2つの位置の温度を検知することができる。半導体基板の内部および表面側での温度を検知することができるため、半導体基板の内部での発熱を検知し易くなる。

(もっと読む)

半導体集積回路

【課題】境界領域の遅延テストを効率的に実行する半導体集積回路を提供すること。

【解決手段】複数のスキャンフリップフロップを含む内部回路部10と、IOピン20と、内部回路部10の出力をIOピン20へ転送するデータパスに接続されるとともにデータパスを内部回路部側パスとIOピン側パスとに分割する、データパスの遅延時間を求める遅延テストのための遅延テスト回路部202と、を備え、遅延テスト回路部202は、内部回路部10から出力された第1のテストデータを内部回路部側パスを介して受け取る内部回路部側スキャンフリップフロップ203と、IOピン側パスを介してIOピン20に出力するための第2のテストデータを保持する複数のIOピン側スキャンフリップフロップ204、205と、を備える。

(もっと読む)

半導体装置の設計方法及び半導体装置の製造方法

【課題】溝内に配線を埋め込む際に層間絶縁膜の表面に深い凹部が生じるのを防止し得る半導体装置の設計方法等を提供する。

【解決手段】単位面積当たりの配線パターンの周囲長の総和を各々の単位領域毎に算出するステップS6と、単位領域内における配線パターンの周囲長の総和が第1の値以上である第1の領域と第2の値以下である第2の領域とを抽出するステップS7,S8と、第1の領域に隣接する第3の領域内に単位面積当たりの周囲長の総和が第3の値である第1のダミーパターンを配置し、第2の領域に隣接する第4の領域内に単位面積当たりの周囲長の総和が第4の値である第2のダミーパターンを配置するステップS9,S10と、第3の領域と第4の領域との間の第5の領域内に単位面積当たりの周囲長の総和が第3の値より小さく、第4の値より大きい第5の値である第3のダミーパターンを配置するステップS11とを有している。

(もっと読む)

半導体装置およびその製造方法

【課題】ヒューズのカットばらつきを防ぐとともに腐食(酸化等も含む)を良好に防ぐ。

【解決手段】半導体装置100は、基板102と、基板102上に形成されたヒューズ配線116と、少なくともヒューズ配線116の側壁を保護するように形成された耐湿性絶縁膜120と、を含む。耐湿性絶縁膜120は、ヒューズ配線116の上面には形成されていないか、またはヒューズ配線116の上面における積層方向の膜厚d1がヒューズ配線116の側壁における積層方向に垂直な方向の膜厚d2よりも薄くなるように形成されている。

(もっと読む)

2,001 - 2,010 / 9,686

[ Back to top ]