国際特許分類[H01L27/08]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 1つの共通基板内または上に形成された複数の半導体構成部品または他の固体構成部品からなる装置 (52,733) | 整流,発振,増幅またはスイッチングに特に適用される半導体構成部品を含むものであり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁を有する集積化された受動回路素子を含むもの (38,321) | 基板が半導体本体であるもの (36,153) | 1種類の半導体構成部品だけを含むもの (8,288)

国際特許分類[H01L27/08]の下位に属する分類

バイポーラ構成部品のみを含むもの (131)

電界効果構成部品のみを含むもの (6,291)

国際特許分類[H01L27/08]に分類される特許

1,861 - 1,866 / 1,866

発光装置およびその作製方法

【課題】アクティブマトリクス型の発光装置における光の取り出し効率を向上させる手段を提供する。

【解決手段】アクティブマトリクス型の発光装置において、第1の凹部101a〜第3の凹部101cを有する第1の基板100に金属膜102a〜第3の金属膜102cを形成することや、画素電極145、有機層148、凸部149aの表面を有する陰極149からなる発光素子150を形成することにより、光の損失や隣の画素への光漏れを防ぐことができる。

(もっと読む)

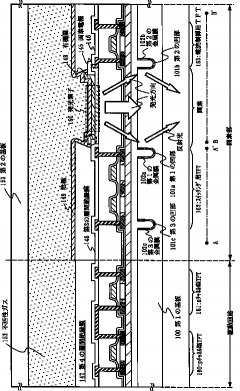

SOI基板の作製方法

【課題】 バックゲート電極を有するSOI基板を貼り合わせ法により形成する場合に、段差平坦化用polySi層の形成を不要とし、また、貼り合わせの歩留まりを向上させ、製造コストを低下させる。

【解決手段】基板貼り合わせ法によるSOI基板の作製方法において、第1の半導体基板1に段差を形成し、段差の形成面上に、所定の深さの開孔部8を有する研磨ストッパー用絶縁膜3を形成し、研磨ストッパー用絶縁膜3上にpolySiを堆積して開孔部8にpolySiを充填し、さらにディッシング防止用酸化膜9を形成し、これを平坦化することによりバックゲート電極BGを形成し、この平坦化面上に第2の半導体基板7を貼り合わせ用酸化膜10を介して貼り合わせることにより、バックゲート電極BGを有するSOI基100Aを作製する。

(もっと読む)

耐ラッチアップ構造及びその形成方法

【課題】 CMOSデバイスのラッチアップ耐性を高める方法及びデバイスを提供する。

【解決手段】 好適な方法は、Nウェル及びPウェルのエッジにインプラントを形成するためハイブリッド・レジストを使用する。インプラントは寄生トランジスタの少数キャリア存続期間を短縮し、よって寄生トランジスタのゲインを少なくする。これによりCMOSデバイスのラッチアップ傾向が小さくなる。好適な実施例の方法では、従来技術の方法にマスキング・ステップを追加することなくこれらのインプラントを形成できる。更にインプラントを形成する好適な方法により、ウェルのエッジと自己整合するインプラントが得られる。

(もっと読む)

半導体装置とその駆動方法

【課題】 原子炉などの放射線が照射される場所での半導体装置の特性劣化を防ぐ半導体装置とその駆動方法を得ること。

【解決手段】 放射線照射環境下にあるシステム回路素子5と第1の半導体回路素子1と、その第1の半導体回路素子1からの出力を放射線シールド材6を介して受ける第2の半導体回路素子2とを備え、第1の半導体回路素子1からの出力が一定となるように、第1の半導体回路素子1とシステム回路素子5とを構成する半導体素子の基板電極あるいは下層ゲート電極にバイアスを印加する半導体装置およびその駆動方法。

(もっと読む)

半導体装置

半導体装置及びその製造方法

【目的】 素子間分離領域の構造及びその形成方法に関し、製造工程が簡略化され、且つ高ドレイン耐圧が得られる素子間分離領域の構造及び製造方法を提供し、MOSLSI等の納期短縮、原価低減及び駆動能力の向上等を図ることを目的とする。

【構成】 一導電型半導体基板1上のトランジスタ領域4を画定する素子間分離用酸化膜7の該トランジスタ領域4側の端部に、該素子間分離用酸化膜7の底面から下方へ突出し、少なくとも該トランジスタ領域4内に該素子間分離用酸化膜7に接して設けられる反対導電型不純物拡散領域9、10よりも深い酸化膜に満たされた溝部7Pを有し、且つ該溝部7P及び素子間分離用酸化膜7の下部に該基板1より高濃度の一導電型チャネルカット領域が設けられないように構成する。

(もっと読む)

1,861 - 1,866 / 1,866

[ Back to top ]