国際特許分類[H01L27/082]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 1つの共通基板内または上に形成された複数の半導体構成部品または他の固体構成部品からなる装置 (52,733) | 整流,発振,増幅またはスイッチングに特に適用される半導体構成部品を含むものであり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁を有する集積化された受動回路素子を含むもの (38,321) | 基板が半導体本体であるもの (36,153) | 1種類の半導体構成部品だけを含むもの (8,288) | バイポーラ構成部品のみを含むもの (131)

国際特許分類[H01L27/082]に分類される特許

1 - 10 / 131

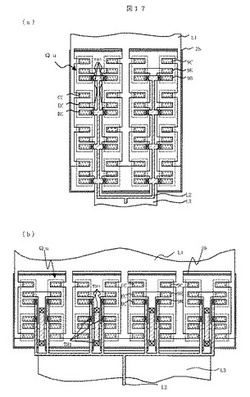

半導体装置

【課題】 放熱性を改善したバイポーラトランジスタを有する半導体装置を提供することにある。

【解決手段】 複数のバイポーラトランジスタQuが配列される半導体装置であって、エミッタ配線L3は幅広部と細長部とを有し、細長部におけるバイポーラトランジスタ素子数が、幅広部が配置された配列の外縁に沿う方向に配列されたバイポーラトランジスタ素子数よりも少なくなるように配置する。

【効果】エミッタ配線の寄生抵抗によるエミッタ−ベース間電圧ばらつきを低減する。

(もっと読む)

半導体装置およびそれを用いた無線通信機器

【課題】半導体装置の熱抵抗を低減すること、および小型化できる技術を提供する。

【解決手段】複数の単位トランジスタQを有する半導体装置であって、半導体装置は、単位トランジスタQを第1の個数(7個)有するトランジスタ形成領域3a、3b、3e、3fと、単位トランジスタQを第2の個数(4個)有するトランジスタ形成領域3c、3dとを有し、トランジスタ形成領域3c、3dは、トランジスタ形成領域3a、3b、3e、3fの間に配置され、第1の個数は、第2の個数よりも多い。そして、単位トランジスタは、コレクタ層と、ベース層と、エミッタ層とを備えており、エミッタ層上には、エミッタ層と電気的に接続されたエミッタメサ層が形成され、このエミッタメサ層上に、エミッタ層と電気的に接続されたバラスト抵抗層が形成されている。

(もっと読む)

半導体集積回路装置

【課題】絶縁素子分離型のバイポーラトランジスタの放熱性を改善する。

【解決手段】薄い半導体層の第1のエリアに配置された第1のトランジスタと、薄い半導体層の第2のエリアに配置された第2のトランジスタで構成される回路部と、を備え、第1のトランジスタは、並列接続された複数のバイポーラトランジスタ素子を構成する複数の単位能動領域の配列全体を囲って配置された素子分離溝を含み、素子分離溝を能動領域から少なくとも1μm離間して設け、能動領域で生成される熱を単位能動領域を囲んで存在する半導体領域から外方に放熱させる構成を備えてなり、第2のトランジスタは、バイポーラトランジスタ動作を行う単位能動領域と、単位能動領域を取り囲んで形成され単位能動領域から1μm以下の位置に配置された素子分離溝を含む。

(もっと読む)

トレンチにより制限された分離拡散領域を備えた相補型アナログバイポーラトランジスタ

【課題】表面上に素子をより高密度に実装する。

【解決手段】第1のトレンチと第2のトレンチとの間の位置において、エピタキシャル層の表面から基板へと下方に延在するドーパントのウェルは、エピタキシャル層の背景ドーピング濃度とは異なるドーピング濃度を有し、エピタキシャル層の残りの部分と第1および第2の接合を形成する。第1の接合は、第1のトレンチの底部から基板に延在し、第2の接合は、第2のトレンチの底部から前記基板に延在する。ウェルおよび第1および第2のトレンチは分離構造を構成し、分離構造は、分離構造の一方側のエピタキシャル層に形成された第1の素子と分離構造の他方側のエピタキシャル層に形成された第2の素子とを電気的に分離する。分離構造による電気的分離は第1および第2のトレンチとPN接合とによってもたらされ、ウェルは第1の導電型の材料でドープされ、基板およびエピタキシャル層は、第1の導電型とは反対の第2の導電型の材料でドープされ、第1および第2の接合はPN接合である。

(もっと読む)

半導体デバイスおよびその製造方法

【課題】CMOS回路側の仕様で不純物領域の深さや濃度が制約を受けるような場合でもhFEの向上を可能とする。

【解決手段】1つのバイポーラトランジスタが、横型の主トランジスタ部と、縦型の補助トランジスタ部とから形成されている。横型の主トランジスタ部は、エミッタ領域31と、ベース領域14Bの表面側部分とコレクタ側部領域13Bとを電流チャネルとして動作する。縦型の補助トランジスタ部は、エミッタ領域31と、その底面に接するベース領域14Bの深部側部と、コレクタ深部領域12Bとを電流チャネルとして動作する。

(もっと読む)

半導体装置の製造方法

【課題】異なる直流電流増幅率(hfe)を有する複数のバイポーラトランジスタを混載した半導体装置を、簡易且つ工程数が少なく得られる半導体装置の製造方法を提供すこと。

【解決手段】第2バイポーラトランジスタ20のエミッタ領域25又はその周囲上であって、当該エミッタ領域25におけるコンタクト領域25Aの周辺上にダミー層52を形成することで、その後、層間絶縁層53の厚みを厚層化することができるため、第2バイポーラトランジスタ20のエミッタ領域25では第1バイポーラトランジスタ10のエミッタ領域15に比べコンタクト深さを浅くしてコンタクトホール54が形成される。これにより、第1バイポーラトランジスタ10と第2バイポーラトランジスタ20との直流電流増幅率(hfe)を変更できる。ダミー層52の形成は第2バイポーラトランジスタ20のベース領域26、コレクタ領域27であってもよい。

(もっと読む)

高周波増幅器

【課題】回路面積を増加させることなく、動作状態のトランジスタからの発熱を抑制することによって、小型化及び低コスト化を図ることができる高周波増幅器を提供する。

【解決手段】複数の単位トランジスタ3が並列に接続されたトランジスタ列からなり、高周波を増幅する増幅素子と、トランジスタ列の隣り合った単位トランジスタ3のフィンガ間にそれぞれ形成された出力整合回路の回路素子2とを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】低コストで性能向上が可能なBiCMOS型半導体集積回路装置を実現することができる半導体装置およびその製造方法を提供する。

【解決手段】n型の半導体基板1の表面から所定の深さに、コレクタ領域を構成するn型の不純物領域26を備える。当該不純物領域26の上方、かつ半導体基板1に形成されたシャロートレンチ分離14で挟まれた領域18にはp型のベース領域20を備える。ベース領域20には、n型の半導体膜からなるエミッタ電極が接触して設けられている。当該半導体装置は、不純物領域26がベース領域20下からシャロートレンチ分離14下まで延在し、当該シャロートレンチ分離14を貫通して不純物領域26に電気的に接続するコンタクトプラグ52を備える。

(もっと読む)

高利得ワイドバンドギャップ・ダーリントン・トランジスタ及び関連する製造方法

パッケージ化電力電子デバイスが、ベース、コレクタ、及びエミッタ端子を有するワイドバンドギャップ・バイポーラ・ドライバ・トランジスタ(112)と、ベース、コレクタ、及びエミッタ端子を有するワイドバンドギャップ・バイポーラ出力トランジスタ(116)とを含む。出力トランジスタのコレクタ端子は、ドライバ・トランジスタのコレクタ端子に結合され、出力トランジスタのベース端子は、ドライバ・トランジスタのエミッタ端子に結合され、ダーリントン対をもたらす。平面図における出力トランジスタの面積は、ドライバ・トランジスタの面積より少なくとも3倍大きい。例えば、出力トランジスタのドライバ・トランジスタに対する面積比は、約3:1から約5:1までの間とすることができる。関連するデバイス及び製造方法についても説明される。 (もっと読む)

バイポーラ・トランジスタ及びその製造方法

【課題】 バイポーラ・トランジスタ構造体、バイポーラ・トランジスタを設計し製造する方法、及びバイポーラ・トランジスタを有する回路を設計する方法を提供する。

【解決手段】 バイポーラ・トランジスタを設計する方法は、バイポーラ・トランジスタの初期設計を選択するステップ(図25の240)と、バイポーラ・トランジスタの初期設計をスケーリングしてバイポーラ・トランジスタの縮小設計を生成するステップ(245)と、バイポーラ・トランジスタの縮小設計の応力補償が必要かどうかを、スケーリング後のバイポーラ・トランジスタのエミッタの寸法に基づいて判断するステップ(250)と、バイポーラ・トランジスタの縮小設計の応力補償が必要な場合に、縮小設計のトレンチ分離レイアウト・レベルのレイアウトを、縮小設計のエミッタ・レイアウト・レベルのレイアウトに対して調節して(255)バイポーラ・トランジスタの応力補償縮小設計を生成するステップ(260)と、を含む。

(もっと読む)

1 - 10 / 131

[ Back to top ]