国際特許分類[H01L29/866]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 整流,増幅,発振またはスイッチングに特に適用される半導体装置であり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁,例.PN接合空乏層またはキャリア集中層,を有するコンデンサーまたは抵抗器;半導体本体または電極の細部(31/00〜47/00,51/05が優先;半導体本体または電極以外の細部23/00;1つの共通基板内または上に形成された複数の固体構成部品からなる装置27/00 (54,759) | 半導体装置の型 (42,689) | 整流,増幅,発振またはスイッチされる電流を流す1つ以上の電極に電流または電圧のみの変化のみを与えることにより制御可能なもの (2,569) | ダイオード (2,495) | ツェナーダイオード (152)

国際特許分類[H01L29/866]に分類される特許

1 - 10 / 152

半導体装置

【課題】ホールド電圧が高いエミッタ・ベース短絡型の保護素子が設けられた半導体装置を提供する。

【解決手段】半導体装置1は、基板10と、前記基板上に形成された第1導電形の半導体層11と、前記基板と前記半導体層との間に形成された第1導電形の埋込層13と、前記半導体層上に形成された第2導電形のウェル14と、前記半導体層上であって、前記ウェルから離隔し、前記埋込層の直上域に形成された第1導電形の第1コンタクト層15と、前記ウェル上に形成された第2導電形の第2コンタクト層16と、前記ウェル上であって、前記第1コンタクト層と前記第2コンタクト層との間に形成された第1導電形の第3コンタクト層17と、前記埋込層と前記第1コンタクト層との間に形成され、前記第1コンタクト層に接した第1導電形のディープ層18と、を備える。

(もっと読む)

半導体装置

【課題】オン抵抗を増大させることなく、ゲート−ソース間のESD耐量を向上させることのできる半導体装置を提供すること。

【解決手段】ポリシリコンゲート層を利用して形成したツェナーダイオードをESD耐量を向上させるために、並列接続させる構造を有する半導体装置とするものであって、ストライプ状または矩形状のツェナーダイオードを並列接続させて、それぞれ活性部内部に形成する半導体装置とする。

【選択図】 図3  (もっと読む)

(もっと読む)

半導体装置

【課題】周辺領域で耐圧を確保する構造において、周辺領域に電界を集中させずに耐圧を確保することができる半導体装置を提供する。

【解決手段】セル領域1にはMOSFETのソース電極12が設けられ、周辺領域2においてチャージバランス変化領域27の周囲に位置すると共に半導体基板6に電気的に接続された最外周電極21が設けられている。また、周辺領域2には、スーパージャンクション構造の上にP型層7が形成され、P型層7の上に、ソース電極12と最外周電極21とを電気的に接続すると共にソース電極12と最外周電極21との間の電圧を複数段に分割する電位分割領域23が設けられている。そして、電位分割領域23は、その少なくとも一部が、半導体基板6の厚み方向から見て周辺領域2、好ましくはチャージバランス変化領域27と重なっている。

(もっと読む)

半導体装置

【課題】リーク電流の少ないダイオードを提供する。

【解決手段】実施形態の半導体装置は、AlXGa1−XN(0<x<1)またはInyAl1−yN(0≦y≦1)からなる第1の半導体層2と、第1の半導体層の同一面上に、ノンドープ、n型又はp型のGaNからなる第1の電子誘起領域1、絶縁膜5とアノード電極7と、第1の電子誘起領域上にカソード電極を備え、第1の電子誘起領域、絶縁膜とアノード電極は第1の半導体層と接合し、絶縁膜は第1の半導体領域とアノード電極の間で、第1の半導体層と接合し、アノード電極と第1の半導体層との接合はオーミック接合であり、カソード電極と第1の電子誘起領域との接合はオーミック接合であることを特徴とする。

(もっと読む)

不揮発性メモリ要素及びこれを含むメモリ素子

【課題】不揮発性メモリ要素及びこれを含むメモリ素子を提供する。

【解決手段】両電極の間にメモリ層を含み、該メモリ層は複数層構造を持つ不揮発性メモリ要素である。メモリ層は、ベース層及びイオン種交換層を含み、これらの間のイオン種の移動による抵抗変化特性を持つ。イオン種交換層は、少なくとも2つの層を含む複数層構造を持つ。不揮発性メモリ要素は、複数層構造のイオン種交換層によりマルチビットメモリ特性を持つ。ベース層は酸素供給層であり、イオン種交換層は酸素交換層である。

(もっと読む)

半導体装置

【課題】パワー半導体素子において、周辺の電界強度を緩和する構造を小さな面積で実現する。

【解決手段】周辺領域Qにおいては、半導体層との間に周辺層間絶縁層(絶縁層)を介して複数の多結晶シリコン層70が、ソース電極30から端部ドレイン電極41の間にかけて設けられる。多結晶シリコン層70には、その長手方向が水平方向から傾斜した(傾斜角θ、0<θ<90°)傾斜部が設けられている。多結晶シリコン層70の傾斜部においては、p型領域71と、n型領域72とが長手方向に交互に多数形成されている。

(もっと読む)

トレンチポリシリコンダイオード

【課題】シリコン内にダイオード構造を位置させた半導体製造方法を提供する。

【解決手段】トレンチポリシリコンダイオードを製造する方法は、N+(P+)型基板上にN−(P−)型エピタキシャル領域を形成すること、エピタキシャル領域内にトレンチを形成すること、さらに、前記トレンチ内に絶縁層を形成し、前記トレンチをポリシリコンで充填する。さらに、P+(N+)型ドーパントをインプラントして、前記トレンチ内に前記ポリシリコンのP+(N+)型領域を、N+(P+)型ドーパントをインプラントして、前記トレンチ内に前記ポリシリコンのN+(P+)型領域を形成しトレンチ内にポリシリコンダイオードを形成することを含み、ダイオードの一部は、トレンチの上面より低い。

(もっと読む)

半導体装置およびその製造方法

【課題】素子特性を悪化させず、アクティブ領域を終端領域に対して、簡単な方法により電気的に独立させることができ、さらには素子サイズの小型化を図ることができる半導体装置およびその製造方法を提供すること。

【解決手段】エピタキシャル層23のアクティブ領域12と終端領域11との間に、エピタキシャル層23の表面24を形成するように、当該表面24に沿って全体にわたって形成されたチャネル層26を、ゲートトレンチ28の深さD1と同じ深さD2を有するアイソレーショントレンチ39で分断する。互いに同じ深さのゲートトレンチ28およびアイソレーショントレンチ39は、同一のエッチング工程で形成される。

(もっと読む)

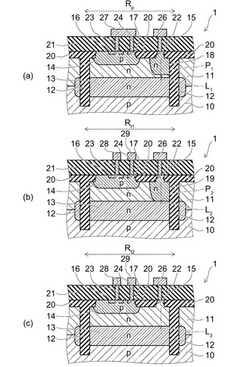

双方向ツェナーダイオードおよび双方向ツェナーダイオードの製造方法

【課題】携帯電話に搭載されるLSIは多機能化により低電圧化が進んでおり、LSIのサージ保護が重要となっている。サージは様々なインターフェースから侵入するため、携帯電話には多数のサージ保護素子が使われている。しかし、携帯電話の信号周波数が高周波であるため、それに使用されるツェナーダイオードには、超低容量特性が求められる。一方、サージ保護素子であるためサージ強度も重要である。端子間容量とサージ強度はトレードオフであり、両方を同時に改善することは困難である。本発明は、一定程度のサージ強度を確保しつつ、超低容量を実現できるサージ保護用ツェナーダイオードの開発に際して発案したものである。

【解決手段】本願発明は、高抵抗のエピタキシャル層の表面に一対のPN接合を設け、チップの上面より一対の電極を取り出すラテラル構造の双方向ツェナーダイオードである。

(もっと読む)

半導体記憶装置

【課題】低電圧化を可能にする。

【解決手段】実施形態は、第1の配線と、その上に積層されたメモリセルと、その上に第1の配線と交差するように形成された第2の配線とを有するセルアレイ層を備え、メモリセルが極性の異なる電気信号が印加されることにより電気的書き換えが可能な可変抵抗素子及び可変抵抗素子に双方向の電流を流す電流制御素子を直列に接続してなる。電流制御素子は、i型半導体とその両側に接する第1及び第2導電型半導体とを有する。第2導電型半導体中の第2の不純物の拡散長は第1導電型半導体中の第1の不純物の拡散長より長く、第1導電型半導体とi型半導体との接合部に、第2導電型半導体とi型半導体との接合部よりも多くのインパクトイオンを発生させるインパクトイオン化促進部が形成される。

(もっと読む)

1 - 10 / 152

[ Back to top ]