国際特許分類[H03B28/00]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | 振動の発生,直接のまたは周波数変換による振動の発生,スイッチング動作を行なわない能動素子を用いた回路による振動の発生;このような回路による雑音の発生 (3,506) | 正弦波振動を発生するために波形の変形を含み,かつ,波形の修正による正弦波状振動の発生を含み,グループ5/00から27/00に包含されない方法による振動の発生 (64)

国際特許分類[H03B28/00]に分類される特許

51 - 60 / 64

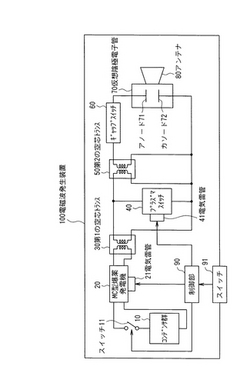

電磁波発生装置

【課題】 プラズマスイッチにて仮想陰極電子管を動作させるに必要な高電圧で且つ立ち上がりの速い電圧パルスを発生することができ、これによって高出力の電磁波を放射すること。

【解決手段】 コンデンサ群10から供給される電流をMC型爆薬発電機20で増幅し、この増幅電流を電気エネルギーとして第1の空芯トランス30に蓄積し、この電気エネルギーをプラズマスイッチ40を通過させることで高電圧パルスとし、この高電圧パルスを第2の空芯トランス50によって更に所定倍数増幅する。この高電圧パルスの電圧値が所定値になるとギャップスイッチ60が作動し、これにて高速な立ち上がりパルス電圧波形が仮想陰極電子管70へ印加される。ここで高出力の電磁波を発生してアンテナ80から放射する。

(もっと読む)

信号生成回路、周波数変換回路、周波数シンセサイザ及び通信システム

【課題】 小さな回路面積でスプリアスが低減された正弦波を生成することができる信号生成回路を提供する。

【解決手段】 方形波状の信号を出力する方形波出力回路12と、方形波出力回路12から出力された信号が入力され、この入力される信号に含まれる第3次高調波に自己の周波数領域の極を対応させたポリフェーズフィルタ14を備えることを特徴とする。これにより、スプリアスの発生要因として最も影響の大きい第3次高調波が低減された正弦波状の信号を、小さな回路面積で得ることができる。

(もっと読む)

マイクロ波発生装置、マイクロ波供給装置、プラズマ処理装置及びマイクロ波発生方法

【課題】動作効率が高く、しかも装置自体も小型化されて低コストで、バランス調整も不要にできるマイクロ波発生装置を提供する。

【解決手段】マイクロ波帯域の基本周波数を有する方形波状のスイッチ信号を発生するスイッチ信号発生部68と、スイッチ信号に基づいてスイッチング電力増幅を行って増幅信号を出力するスイッチング電力増幅部70と、スイッチング電力増幅部に増幅用の駆動電圧を可変的に供給することができる可変電圧供給部71と、増幅信号からスイッチ信号の基本周波数と同じ周波数の正弦波信号を取り出してマイクロ波として出力するためのマイクロ波選択部72と、マイクロ波を検出する出力信号検出部74と、出力信号検出部の検出結果に基づいて可変電圧供給部を制御する駆動電圧制御部76とを備える。

(もっと読む)

全高調波歪みが非常に小さい正弦波成形器

正弦波形状の出力信号を出力(Sn,Sp)に発生させる装置(20)である。この装置(20)は、差動ペア(22)として配置された第1のトランジスタ(M1)および第2のトランジスタ(M2)を具備する。差動ペア(22)は所与の振幅(A)をもつ三角波入力信号(Vin(t))を第1のトランジスタ(M1)のゲート(Tp)と第2のトランジスタ(M2)のゲート(Tn)との間に印加することを可能にする2個の入力ノード(Tp,Tn)を有する。差動ペア(22)は、第1のトランジスタ(M1)のソースと第2のトランジスタ(M2)のソースが接続されるノード(X)をさらに具備する。正弦波形状の信号が第1のトランジスタ(M1)のドレイン(Sp)と第2のトランジスタ(M2)のドレイン(Sn)との間に供給される。カレントミラー(21)が所定のテール電流(Iss)を前記差動ペア(22)のノード(X)に流入/流出させるため利用される。差動ペア(22)は、正弦波形状の出力信号(Io;Vout)が三角波入力信号(Vin(t))の非線形関数であるように、第1のトランジスタ(M1)および第2のトランジスタ(M2)が飽和領域で動作させられることを可能にする。  (もっと読む)

(もっと読む)

電磁波発生素子

【課題】プラズマ波の位相が合わないことによりプラズマ波強度が低下すること。

【解決手段】半導体基板5と、複数のナノワイヤ状の半導体層4と、絶縁膜6と、ゲート長をプラズマ波の周期の1/4とした複数のゲート電極1と、複数のナノワイヤに対応した複数のドレイン電極3と、ソース電極2を含み、複数のドレイン電極間を注入同期により電磁結合することで逆位相によるキャンセリングを抑制してプラズマ波の強度をナノワイヤの本数倍する。

(もっと読む)

周波数掃引を生成するためのデジタル周波数シンセサイザおよび方法

選択可能な周波数掃引の周波数掃引合成出力信号を合成する単一チップのデジタル周波数シンセサイザ(1)は、直接デジタルシンセサイザ(5)を含み、直接デジタルシンセサイザ(5)は、オンチップのデータ処理回路(25)によって直接デジタルシンセサイザ(5)の周波数制御入力(8)に与えられた周波数制御デジタルワードの値に応答して、出力端子(7)上で周波数掃引合成出力信号を生成する。オンチップのプログラム可能なデータ格納回路(12)は、デジタル周波数シンセサイザ(1)が動作する選択されたモードを示すデータを格納し、生成される周波数掃引合成出力信号の選択可能な周波数および時間領域を示すデータを格納するようにプログラム可能である。  (もっと読む)

(もっと読む)

位相持続アジャイル信号発生方法、機器、およびコンピュータプログラム製品

位相持続アジャイル信号発生方法、機器、および/またはコンピュータプログラム製品は、直接ディジタルシンセサイザ(DDS)クロック速度を提供し、所望の出力周波数のための周波数同調ワード(FTW)を提供し、所望のDDS更新速度のためのDDS更新を提供し、所望のDDS更新速度のための等価周波数最下位ビット(LSB)を提供し、LSBアキュムレータの現在位相を提供し、DDSクロック速度、FTW、DDSへのDDS更新速度、所望のDDS更新速度のための等価LSB、およびLSBアキュムレータの現在位相に基づいて、所望の出力周波数のコヒーレント位相を生成する。コヒーレント位相は、FTWとLSBアキュムレータの現在位相とを乗算して得られた結果の小数部分とし得る。 (もっと読む)

波形発生装置

【目的】 外部から入力したトリガ信号に応じて任意の波形データを優先順位の高い方から順次出力する波形発生装置を提供する。

【構成】 外部入力制御部11からトリガ信号が入力されると、このトリガ信号と、現在出力している波形データとの優先度を比較し、現在出力している波形データの方がトリガ信号よりも優先度が高い場合は、状態遷移制御部2にトリガ信号が一旦記憶され、現在出力している波形データの出力が完了した後、トリガ信号に応じた波形データに切り替えて出力する。現在出力している波形データの方がトリガ信号よりも優先度が低い場合は、現在出力している波形データの出力を停止し、トリガ信号に応じた波形データに切り替えて出力する。

(もっと読む)

ROM容量削減方法

【課題】本発明は、データの1/nデータのみを記憶する容量にROMを形成し、複数回読み出して正弦波等のデータを形成し、ROMの容量を大幅に少なくすることを目的とする。

【解決手段】本発明によるROM容量削減方法は、データの1/nデータ(2A)のみをROM(1A)に記憶し、1/nデータ(2A)をm回読み出して各1/nデータ(2A)を連続させ、データを生成することにより、ROM(1A)の容量は1/nデータ(2A)を記憶するのみの容量とする方法である。

(もっと読む)

周波数合成装置及び周波数合成方法

【課題】 正確に位相が合わされた複数のキャリア周波数を生成する。

【解決手段】 基準周波数4224MHzを8分周して、528MHzを生成する。DLLを用いて生成した120度位相差のある528MHz矩形波の加算により基本波を打ち消して3逓倍した後、2分周して796MHzを得る。また、528MHzの複素信号対を2分周して45度ずつ位相が異なる264MHz波形を生成し、これらを重み付け電流加算して、3次と5次の高調波が抑圧されたデジタル正弦波を得る。そして、796MHzと264MHzを4224MHzに選択的に周波数加算して、所要の周波数帯を得る。

(もっと読む)

51 - 60 / 64

[ Back to top ]