国際特許分類[H03B5/12]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | 振動の発生,直接のまたは周波数変換による振動の発生,スイッチング動作を行なわない能動素子を用いた回路による振動の発生;このような回路による雑音の発生 (3,506) | 出力から入力への再生帰還による増幅器を用いた振動の発生 (3,166) | 周波数決定素子が集中定数インダクタンスと集中定数キャパシタンスとからなるもの (396) | 増幅器の能動素子が半導体装置であるもの (289)

国際特許分類[H03B5/12]に分類される特許

281 - 289 / 289

電圧制御デジタルアナログ発振器およびこれを用いた周波数シンセサイザ

本発明は、発振器および周波数シンセサイザに関する。特に、電圧制御デジタルアナログ発振器およびこれを用いた周波数シンセサイザに関する。

本発明は、アナログ入力端に入力される電圧およびデジタル入力端に入力されるデジタル値によって出力信号の周波数が決定される発振器と、間欠的に前記アナログ入力端に入力される電圧を第1の閾値電圧および第2の閾値電圧と大小を比較し、その結果に応じて前記デジタル入力端に入力されるデジタル値を変化させるデジタル同調器と、を備える電圧制御デジタルアナログ発振器を提供する。また、これを用いた周波数シンセサイザを提供する。本発明に係る発振器および周波数シンセサイザは、雑音が少ないながらも、広帯域の周波数出力を得ることができる長所がある。

(もっと読む)

(もっと読む)

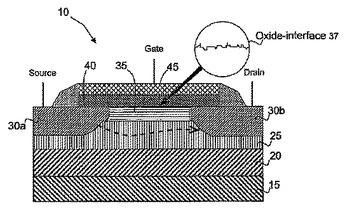

ストレインド・シリコン電圧制御発振器(VCO)

ストレインド・シリコン電圧制御発振器(VCO)は、ストレインド・シリコン層を有する第1Pチャネル金属酸化膜半導体(PMOS)装置を含み、ストレインド・シリコン層を有する第2PMOS装置に結合される。  (もっと読む)

(もっと読む)

マルチループ構成から形成されたインダクタンスループを有する集積回路パッケージ

集積回路パッケージが、リードワイアと1つまたは複数の入出力(I/O)パッケージピンとの接続から形成されるインダクタループを含む。一実施形態では、インダクタループは、集積回路チップ上の第1のボンディングパッドをパッケージの第1のI/Oピンに接続する第1および第2のワイアと、チップ上の第2のボンディングパッドをパッケージの第2のI/Oピンに接続する第3および第4のワイアとから形成される。インダクタループを完成するために、第1のI/Oピンと第2のI/Oピンは、ピン間の第3の導体によって接続される。第3の導体は、1つまたは複数のボンディングワイアを含むことができ、I/Oピンは、互いに隣接するものであることが好ましい。しかし、ループは、例えばループ長要件、空間の考慮すべき点、および/または他の設計要因もしくは機能要因に基づいて、I/Oピンの非隣接接続から形成することができる。他の実施形態では、第1のI/Oピンと第2のI/Oピンの間の接続が、I/Oピンに単一構造を持たせることによって確立される。他の実施形態では、第1のI/Oピンと第2のI/Oピンの間の接続が、パッケージ基板の表面上に、またはこの基板内に位置するメタライゼーション層によって確立される。集積回路パッケージの境界線内でインダクタループを形成することにより、空間要件における実質的な削減が実現され、これは小型化を促進する。また、集積回路は、その少なくとも1つのパラメータがパッケージのインダクタループの長さによって制御される様々なシステムのいずれか1つで実装することができる。

(もっと読む)

(もっと読む)

発振回路

【課題】 VCO発振周波数の調整を容易にする。

【解決手段】 VCO用共振回路が接続されるボンディングパッド5下のエピタキシャル層2Aの電位を、従来のフローティング状態から抵抗6を介して所定(Vcc)電位に固定することで、エピタキシャル層2Aの電位変化を速くして、寄生容量値が速やかに安定することから、電源ON時のドリフトが改善する。

(もっと読む)

圧電発振回路

【課題】 圧電発振回路において、発振周波数の位相雑音特性が、電源電圧の低電圧化にともなって劣化することを防止するに好適な圧電発振回路を提供すること。

【解決手段】 圧電発振回路において、トランジスタのベースに流れるベース電流を決定づけるバイアス抵抗(ブリーダ抵抗)に対して、直列にコイルLを挿入するよう構成する。電源電圧の低電圧化にともなってバイアス抵抗を小さな値に設計した場合においても、発振周波数領域においてバイアス抵抗部がコイルLによってハイインピーダンスになる。このような作用によれば、回路損失が小さくですみ、発振回路の実効Q値が低下しないから、信号純度の良好な発振器を得ることができる。

(もっと読む)

可変周波数発振回路

【課題】 本発明の目的は電圧制御水晶発振器(VCXO)における周波数可変範囲を拡大する回路手段に関することにある。

【解決手段】 目的を達成するために、安価でしかも広範囲な周波数可変が出来るような回路構成を実現するために、発振回路に接続された圧電振動子と可変容量ダイオードと、インダクタンスと容量を並列接続した回路網とを直列に配置し電圧に対する周波数可変範囲を拡大したことで課題を解決するものである。

(もっと読む)

回路デバイスとその製造方法

【課題】 高周波の集積回路用の構造体を改善する。

【解決手段】本発明の集積回路は、高抵抗の多結晶シリコン製基板に接合された、単結晶半導体材料の薄い層に形成した能動デバイスと受動デバイスを含む。単結晶基盤に支持された従来の集積回路と比較すると、高抵抗の多結晶基板に接合された単結晶フィルムの回路は、浮遊キャパシタンスと、クロストークと、渦電流の影響を受けづらい。通常のSOIウェハと比較すると、多結晶基板は高抵抗で、この高抵抗は単結晶基板よりも汚染による影響をはるかに受けづらい。シリコンオンサファイア、あるいは他の絶縁材料上に形成されたシリコンの比較すると、多結晶基板は結晶性のシリコン製フィルムの機械的、熱的、光学的特性により適合可能である。

(もっと読む)

発振器及びこれを用いた受信機

CMOS水晶発振器

CMOS水晶発振器

【目的】 スタンバイ動作時の消費電力を極力低減し得るCMOS発振器を提供する。

【構成】 CMOSインバータの入出力間に抵抗と水晶振動子を並列に接続して発振回路を形成し、外部からの制御信号により前記発振回路の出力を一時的に停止させるCMOS水晶発振器おいて、 上記制御信号に基づき、CMOSインバータの動作電圧をON、OFFした構成とする。

(もっと読む)

281 - 289 / 289

[ Back to top ]