国際特許分類[H03F3/34]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | 増幅器 (10,074) | 増幅素子として電子管のみまたは半導体装置のみをもつ増幅器 (6,434) | 全段が直流結合された直流増幅器 (833)

国際特許分類[H03F3/34]の下位に属する分類

半導体装置のみをもつもの (287)

電子管のみをもつもの (1)

国際特許分類[H03F3/34]に分類される特許

1 - 10 / 545

正帰還増幅器およびインターポレーション回路

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

可変利得増幅システム

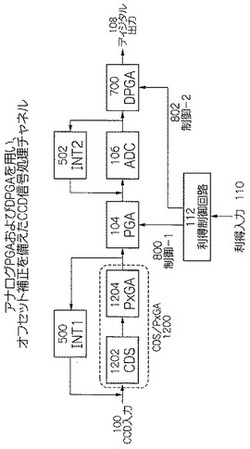

【課題】入力および出力オフセット補正機能を備えたCCD信号処理チャネルを提供する。

【解決手段】本可変利得増幅回路は、入力信号から不要の相関ノイズ成分を除去する相関二重サンプリング回路1202と、相関二重サンプリング回路の下流側に位置する第1プログラマブル利得増幅器104と、入力が前記第1プログラマブル利得増幅器の入力に接続され、出力が相関二重サンプリング回路の入力に接続され、入力信号のオフセットおよび相関二重サンプリング回路のオフセットのうちの少なくともいずれか一方のために第1オフセット補正を提供する第1オフセット補正回路500と、第1プログラマブル利得増幅器の下流側に位置するアナログ/ディジタル変換器106と、第1プログラマブル利得増幅器の下流側に位置し、第2オフセット補正を提供する第2オフセット補正回路502と、相関二重サンプリング回路の下流側であって、かつ、第1プログラマブル利得増幅器の上流側に位置する画素利得増幅器1204を備えている。

(もっと読む)

オペアンプ補償回路

【課題】出力バッファを有するオペアンプA1であつて、オフセット電位を従来よりも抑えられるオペアンプ補償回路を提供する。

【解決手段】バッファの出力と接地間に、入力信号が接地から電源電圧まで変化されるMOSトランジスタT1を有し、あるいは、NチャンネルトランジスタTN1と、PチャンネルトランジスタTP1とを並列接続し、それぞれ入力信号と反転された入力信号が入力されている構成を有し、オフセット電位が接地となることを特徴とする。

(もっと読む)

絶縁アンプ

【課題】機械振動を応用した絶縁アンプは、1次側から2次側へ伝達する振動振幅は振動体のQ値に依存するため、変調レベルが安定せずアナログ信号を高精度で伝達できない。また、Q値が高い振動体を使うと入力信号の変化への追従性が悪くなり、帯域幅がほとんど得られない。

【解決手段】Q値の高い同一の振動体上に、第1の振動数を有する発振用振動子と第2の振動数を有する絶縁用振動子とを形成し、特に第1の振動数と前記第2の振動数とには所定の差を持たせる。発振用振動子により第1の振動数で発振するAGC機能付きの発振器を構成し、この発振信号に絶縁アンプ入力信号による振幅変調をかけて絶縁用振動子の1次側を振動させ、絶縁用振動子の2次側から得られる信号をAGCモニタ信号をもとに復調することで絶縁アンプ出力信号を得る。

(もっと読む)

駆動回路

【課題】消費電流が小さな駆動回路を提供する。

【解決手段】オフセット補償機能付き駆動回路190は、入力電位に応じたレベルの出力電位を出力するプッシュ型駆動回路160と、駆動回路160のオフセット電圧VOFを補償するオフセット補償回路とを備える。オフセット補償回路は、キャパシタ122およびスイッチS1〜S4を含む。スイッチS1,S2をオンしてキャパシタ122をオフセット電圧VOFに充電し、次にスイッチS3をオンしてVI+VOFを駆動回路160に与え、次いでスイッチS4をオンしてVO=VIとする。したがって、消費電流を低減し、オフセット電圧VOFを補償できる。

(もっと読む)

電流出力回路

【課題】アイドリング電流の影響を受けることなく高精度に電流検出を行うことが可能な電流出力回路を小規模な回路で実現すること。

【解決手段】第1の増幅器と、第1の増幅器の出力を入力するプッシュプル形出力段と、プッシュプル形出力段の第1のトランジスタ及び第2のトランジスタに対して夫々カレントミラー接続した電流検出器の第3のトランジスタ及び第4のトランジスタと、第3のトランジスタのドレインを第1のトランジスタのドレインの電位と等しくするバッファ回路と、第4のトランジスタのドレインに接続された電流検出抵抗と、を備える。プッシュプル形出力段の増幅信号は、負荷を介して第1の増幅器の反転入力端子に接続される。この構成により、電流検出抵抗にアイドリング電流を流さないようにすることができる。

(もっと読む)

オフセット電圧補償装置

【課題】オフセット電圧補償装置において、部品点数の増加を抑えながら、増幅器のオフセット電圧を補償して、センサ部の直流出力信号の真値を検出する。

【解決手段】オフセット電圧補償装置1は、電源2と接続され物理量を計測して出力信号に変換するセンサ部3と、センサ部3の入力を短絡する切替器4と、センサ部3の出力信号を増幅する増幅器5と、増幅器5の出力に基づいて電気量を演算する演算器6とを備える。演算器6は、センサ部3の入力を短絡していない時の増幅器5の出力から、短絡時の増幅器5の出力を減算して信号成分の差分を抽出する。次に、当該信号成分の差分と、センサ部3の抵抗値及び切替器4の抵抗値から定められる所定の係数とを用いて、センサ部3の出力信号の真値を検出する。

(もっと読む)

対数/逆対数変換回路

【課題】温度補正を行なわなくても、逆対数変換した際に得られる出力信号が線形性を保つことができる対数/逆対数変換回路を提供する。

【解決手段】対数変換回路1の電流帰還用トランジスタTR2を通過した電流信号Iinを逆対数変換回路2に入力し、電流/電圧変換回路3でこの電流信号Iinをこれに対応した電圧値に変換した後、引算回路4で電流/電圧変換回路3の出力電圧と予め設定された基準電圧との差分を出力する構成とし、かつ引算回路4はその差分出力が電流信号Iinに比例した線形性をもつように回路定数を設定している。

(もっと読む)

定電流回路

【課題】1または複数の他の定電流回路との間で共通インピーダンスを共有する定電流回路の出力電流に、他の定電流回路の出力電流に起因した誤差が生じることを防ぐ。

【解決手段】オペアンプと、当該オペアンプの出力端子にゲートが接続されドレインが当該定電流回路の出力端となる電界効果トランジスタと、この電界効果トランジスタのソースと共通インピーダンスとの間に介挿された抵抗と、を有する定電流回路に、共通インピーダンスおよび抵抗の共通接続点の電圧を第1の基準電圧とし、オペアンプの非反転入力端子には、第2の基準電圧と第1の基準電圧と電位差を所定の分圧比で分圧した電圧を印加し、同反転入力端子には、電界効果トランジスタのソースおよび抵抗の共通接続点の電圧と第3の基準電圧との電位差を所定の分圧比で分圧した電圧を印加する分圧回路を設ける。

(もっと読む)

電子回路およびその制御方法

【課題】ドレインアイドル電流のドリフトを直接補償すること。

【解決手段】入力信号が入力するゲートと、出力信号が出力するドレインとを有するFETを含む電子回路の制御方法であって、前記FETのゲートに前記入力信号が入力してからの時間t経過後における前記入力信号x(t)に対応するドレインアイドル電流の変化量ΔIdq(t)を算出するステップS10と、前記変化量ΔIdq(t)を補償するためのゲートバイアス電圧Vgを算出するステップS12と、前記ゲートバイアス電圧を前記FETのゲートに印加するステップS14と、を含むことを特徴とする電子回路の制御方法。

(もっと読む)

1 - 10 / 545

[ Back to top ]