国際特許分類[H03K23/40]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | パルス技術 (16,231) | 計数連鎖を包含するパルス計数器;計数連鎖を包含する周波数分割器 (291) | ゲート信号またはクロック信号がすべての段に印加されるもの,すなわち.同期形計数器 (94)

国際特許分類[H03K23/40]の下位に属する分類

位相ずれのゲートまたはクロック信号が計数段に印加されるもの (39)

底または基数が2のべきでないもの (4)

双安定再生トリガ回路を用いるもの (32)

国際特許分類[H03K23/40]に分類される特許

1 - 10 / 19

バッファ回路

【課題】TFT特性のばらつきにかかわらず画像ムラがなく、高精細・高解像度の良好な画像を得ることができる半導体表示装置の駆動回路および半導体表示装置を提供する。

【解決手段】半導体表示装置はソース信号線側駆動回路と、ゲイト信号線側駆動回路とを有し、駆動回路はシフトレジスタ回路からのタイミング信号をバッファする複数のインバータ回路を有するバッファ回路を有し、インバータ回路は複数のインバータ回路を並列に接続して構成される。

(もっと読む)

レジスタ制御ディレイロックループを備えた半導体デバイス

【課題】DLLクロックの無用なトグリングによる電流の消耗を低減することができるレジスタ制御ディレイロックループを備えた半導体デバイスを提供する。

【解決手段】レジスタ制御ディレイロックループから出力されたDLLクロックを用いる内部回路を備えた半導体デバイスにおいて、半導体デバイスに対する作動信号及び非作動信号に応答して、内部回路に印加されるDLLクロックをイネーブルしたりディスエーブルしたりするクロックイネーブル信号を生成する手段を備える。その場合、クロックイネーブル信号を生成する手段は、作動信号又は非作動信号に応答してプルダウン又はプルアップ動作を行う駆動手段と、半導体デバイスに対する作動信号に応答して駆動手段の出力ノードをリセットするリセット手段と、駆動手段の出力ノードに印加された信号をラッチし、バッファリングして出力する出力手段とを備えている。

(もっと読む)

可変分周回路

【課題】より高速な分周動作を行う。

【解決手段】クロック信号clkを共通に受け、縦続接続される複数個のフリップフロップ回路CT0〜CT5と、分周比設定用の設定値cnum0〜cnum5に基づいて前段のフリップフロップ回路の出力値を次段のフリップフロップ回路へ伝達するか否かを制御する複合ゲートCG0〜CG5と、を備え、最終段のフリップフロップ回路CT0の出力値が所定の論理値となった場合に、複合ゲートCG0〜CG5によって伝達可能に制御されるフリップフロップ回路を初期化する。

(もっと読む)

分周回路

【課題】 不要な周波数の信号の生成を抑制可能な分周回路を提供する。

【解決手段】 分周回路は、入力信号をクロック信号に同期して順次シフトする少なくともnビットのシフトレジスタと、シフトレジスタのnビットの出力信号のうち、入力信号をnビットシフトしたビットの出力信号の論理レベルの変化に応じて、入力信号をパルス状に変化させるパルス生成回路と、クロック信号をnビットのビット数に応じた分周比で分周するために、シフトレジスタの何れか1ビットの出力信号、または、入力信号の論理レベルの変化に応じて論理レベルが反転する分周信号を生成する分周信号生成回路と、を備える。

(もっと読む)

半導体装置のカウンタ

【課題】 本発明は、カウンタの伝搬時間の遅延を減少させ、データスキューを最小化するカウンタを提供することを可能にすることを目的としている。

【解決手段】 本発明のnビットカウンタは、Dフリップフロップと、データロッド信号により外部データと前記Dフリップフロップの第2の出力信号のいずれか一つを選択して出力する第2のマックスと、カウンタイネーブル信号またはデータロッド信号により前記Dフリップフロップの第1の出力信号と前記第2のマックスの出力信号のいずれか一つを前記Dフリップフロップの入力信号に伝達する第1のマックスをそれぞれ含むn個のカウンタブロックを含むが、第mのカウンタブロックは、第1〜第m−1のカウンタブロックに含まれた第2のマックスの出力信号が全て第1のレベルであり、前記カウンタイネーブル信号が第2のレベルである区間でトグリングされる第mのビット信号を出力することを特徴とする。

(もっと読む)

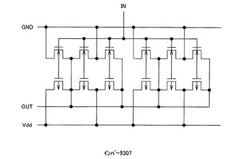

カウンター回路

【課題】常時動作を行うカウンター回路では、低消費電力化が求められている。

【解決手段】本発明は、入力クロックに応じて、所定のビット幅の値をカウントして記憶するmビットの第1のカウンターと、前記第1のカウンターがカウントした結果に応じて出力される値に基づき、前記入力クロックを伝達するか否かを制御するクロック伝達制御回路と、前記クロック伝達制御回路から伝達された入力クロックに応じて、前記所定のビット幅の値をカウントして記憶するnビットの第2のカウンターとを有するカウンター回路である。

(もっと読む)

半導体集積回路

【課題】ラッチ回路のデータ信号を強誘電体キャパシタに保持させる半導体集積回路において、強誘電体キャパシタのインプリント特性の劣化を防止すること。

【解決手段】データ信号Dを保持する信号保持部12と、信号保持部12にスイッチTR1、TR2を介して電気的に接続された強誘電体キャパシタF1、F2とを備えたラッチ回路10を有し、所定の期間内のみスイッチスイッチTR1、TR2をオン状態にし、データ信号Dの電位に応じた残留分極量を強誘電体キャパシタF1、F2に保持させる半導体集積回路による。

(もっと読む)

インバータ回路、シフトレジスタ回路、否定論理和回路、否定論理積回路

【課題】出力の最大振幅の幅が狭まることを軽減することができるインバータ回路を提供する。

【解決手段】第1トランジスタの一方のソース/ドレイン領域は第2トランジスタの一方のソース/ドレイン領域に、第2トランジスタの他方のソース/ドレイン領域は一方の電圧供給線に、ゲート電極は第3トランジスタの一方のソース/ドレイン領域に、第3トランジスタのゲート電極は他方のソース/ドレイン領域に、第3トランジスタの他方のソース/ドレイン領域は一方の電圧供給線に接続され、第2トランジスタのゲート電極と第3トランジスタの一方のソース/ドレイン領域とが接続されたノード部には第4トランジスタの一方のソース/ドレイン領域が、第1トランジスタ及び第4トランジスタの他方のソース/ドレイン領域は他方の電圧供給線に接続され、第1トランジスタのゲート電極及び第4トランジスタのゲート電極には入力信号が印加される。

(もっと読む)

インバータ回路、シフトレジスタ回路、否定論理和回路、否定論理積回路

【課題】同一導電型のトランジスタから成るインバータ回路を提供する。

【解決手段】インバータ回路は否定論理構成部と出力回路部とから構成されており、出力回路部は同一導電型の2つのトランジスタから構成されており、出力回路部を構成する2つのトランジスタを、第1出力トランジスタ、及び、第2出力トランジスタと表すとき、第1出力トランジスタの一方のソース/ドレイン領域と第2出力トランジスタの一方のソース/ドレイン領域とは接続されており、第2出力トランジスタのゲート電極は、否定論理構成部の出力側に接続されており、第1出力トランジスタの他方のソース/ドレイン領域には第1電圧が印加され、第2出力トランジスタの他方のソース/ドレイン領域には第2電圧が印加され、第1出力トランジスタのゲート電極、及び、否定論理構成部の入力側には、入力信号が印加される。

(もっと読む)

分周回路及び分周方法

【課題】複数段の1/2分周器により分周された各信号において、全ての分周信号同士が同期し、かつクロック信号の同一のエッジに同期した分周信号を出力することが可能な分周回路及び分周方法を提供する。

【解決手段】第1の同期回路群は、分周器群と第1の同期回路群との間に設けられ、分周器群からの各分周信号を入力とし、その出力が第1の同期回路群のラッチ回路の各入力端子に接続されたN段のラッチ回路からなり、第1段目から第M段目のラッチ回路のクロック入力端子にはクロック信号が入力され、クロック信号に同期した信号を出力し、第(M+1)段目から第N段目までのラッチ回路のクロック入力端子には第M段目のラッチ回路の出力信号が入力され、M段目のラッチ回路の出力に同期した信号を出力する第2の同期回路群を有する。

(もっと読む)

1 - 10 / 19

[ Back to top ]