国際特許分類[H03K5/02]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | パルス技術 (16,231) | このサブクラス中の他のメイングループの1によっては包括されないパルス操作 (3,125) | パルスの整形 (700) | 増幅によるもの (32)

国際特許分類[H03K5/02]に分類される特許

1 - 10 / 32

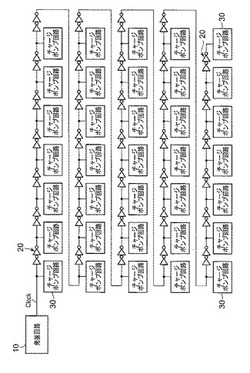

昇圧回路及びその給電方法

【課題】簡略化された回路構成でノイズ低減効果を持つ多相駆動型の昇圧回路を実現する。

【解決手段】昇圧回路は、所定周期のクロック信号を出力する発振回路と、前記クロック信号の1本の配線に直列接続され、トータル遅延時間が前記所定周期よりも長い複数の遅延回路と、前記複数の遅延回路に対応して前記1本の配線に接続された複数の分割昇圧回路と、を含む。

(もっと読む)

パルス電力増幅装置

【課題】熱時定数による増幅利得の時間的な変化を補償でき、良好な直線性を有するパルス増幅装置を提供する。

【解決手段】パルス電力増幅装置10は、高周波信号を変調するパルス信号を入力され、前記パルス信号を入力され第1の増幅器の熱時定数に対応する時定数を有する第1の微分回路と、前記パルス信号を入力され第2の増幅器の熱時定数に対応する時定数を有する第2の微分回路と、励振回路及び最終段増幅器の入力側の負バイアス端子に供給される負バイアス電圧を出力する負バイアス電源18と、この負バイアス電源の出力する負バイアス電圧に前記第1の微分回路の出力を加算して前記第1の増幅器の入力側の負バイアス端子に供給する第1の加算回路と、前記負バイアス電源の出力する負バイアス電圧に前記第2の微分回路の出力を加算して前記第2の増幅器の入力側の負バイアス端子に供給する第2の加算回路と、を有する。

(もっと読む)

レベルシフタ誤動作防止回路

【課題】本発明は、レベルシフタ誤動作防止回路に係り、レベルシフタの誤動作を、信号伝達の過大な遅延と消費電流の増大とを招くことなく防止することにある。

【解決手段】伝達すべき信号に応じて駆動されるN型トランジスタ30と、N型トランジスタ30の出力に応じて駆動されるP型トランジスタ32と、P型トランジスタ32を駆動するために設けられるプルアップ抵抗34と、を有する、基準電圧が互いに異なる2つの回路系の間で信号伝達を行うレベルシフタ16の誤動作を防止する回路において、2つの回路系の基準電圧が相対変位した際、N型トランジスタ30に存在する寄生容量36へプルアップ抵抗34を介して充電電流が供給される前に、その寄生容量36へ充電電流を供給する急速充電手段を設ける。

(もっと読む)

ブースト回路およびそれを用いたΔΣ変調器、電子機器

【課題】ブースト回路におけるビットエラーを防止する。

【解決手段】ビットストリーム信号BSINを受け、その振幅をブーストして出力するブースト回路100が提供される。第1クロックブースタ10aは、クロック信号CKを受け、その振幅をブーストする。第2クロックブースタ10bは、反転されたクロック信号CK#を受け、その振幅をブーストする。スイッチ22は、クロックブースタ10a、10bの出力信号CK’、CK#’を受け、ハイレベルである一方を選択する。第1キャパシタC1は、スイッチ22の出力端子にカップリングされる。レベルシフタ28は、ビットストリーム信号BSINのハイレベルを、第1キャパシタC1に生ずる電圧レベルにレベルシフトする。

(もっと読む)

デューティ補正回路、及びデューティ補正方法

【課題】本発明は、入力信号のデューティ比や周波数、温度、電源電圧、プロセスによらず、出力信号のデューティ比を補正することが出来るデューティ補正回路、及びデューティ補正方法を提供することを課題とする。

【解決手段】コモンモード比較回路13からのフィードバック信号により、レベルシフト回路11はレベルを補正する。またコモンモード比較回路15からのフィードバック信号により、TrTf制御回路12は、信号のエッジの角度を補正する。

(もっと読む)

I2Cインタフェースを有するシステム及びその方法

【課題】本発明の目的は、I2Cインタフェースを有するシステムを提供することである。

【解決手段】本発明の第1の態様によると、マスター装置と前記マスター装置により制御されるスレーブ装置との間のインタフェースをとるI2Cインタフェースを有するシステムが提供される。前記マスター装置は第1のデータ・バスと接続され第1の駆動電圧で動作し、前記スレーブ装置は第2のデータ・バスと接続され第2の駆動電圧で動作し、前記システムは、それぞれ前記第1及び第2の駆動電圧の間のレベルシフト機能を有する第1及び第2の双方向デジタル入出力回路、及び前記第1及び第2の双方向デジタル入出力回路を制御するシーケンサ回路、を有し、前記シーケンサ回路は、前記第1及び第2の双方向デジタル入出力回路の出力に基づき、データの伝達方向を前記マスター装置から前記スレーブ装置へ、又は前記スレーブ装置から前記マスター装置へ切り替える。

(もっと読む)

ジッタ増幅回路、信号発生回路、半導体チップ、及び試験装置

【課題】入力信号に含まれるジッタを増幅するジッタ増幅回路150。

【解決手段】入力信号に含まれるジッタを増幅するジッタ増幅回路であって、入力信号を受け取り、入力信号の波形を歪ませることにより、入力信号の高調波成分を生じさせる歪回路と、歪回路が出力する歪信号を、ジッタを増幅すべき増幅率に応じた次数の高調波成分以外の成分を除去して通過させるフィルタとを備えるジッタ増幅回路。

(もっと読む)

インターフェイス回路およびそれを備える表示装置

【課題】波形整形回路の周波数特性の測定を可能にする。

【解決手段】波形整形回路11は、入力差動信号INN,INPを波形整形する。出力切換回路12は、通常モードのときには、波形整形回路11からの整形差動信号SP,SNを2値化して出力する。一方、出力切換回路12は、テストモードのときには、波形整形回路11からの整形差動信号SN,SPを正弦波信号として出力する。

(もっと読む)

電源回路及び携帯機器

【課題】昇圧動作を行う電源回路においてバックゲートにかかる電圧の影響を抑制することである。

【解決手段】電源回路10において、入力電源の他方側端子GNDと一方側端子VCCとの間に直列に第1のスイッチングトランジスタ20、第2のスイッチングトランジスタ22を、入力電源の一方側端子VCCと昇圧出力端子OUTとの間に直列に第3のスイッチングトランジスタ24、第4のスイッチングトランジスタ26をそれぞれ設け、第1と第2のスイッチングトランジスタの接続点と、第3と第4のスイッチングトランジスタの接続点との間にシフト用コンデンサ40を設け、昇圧出力端子OUTに保持用コンデンサ42を接続する。第3のスイッチングトランジスタ24にはバックゲートにかかる電圧を切り換えるバックゲート切換回路30が設けられる。

(もっと読む)

受信回路および2値信号生成回路

【課題】簡易な回路構成で消費電力の増大を抑制しつつ、受信信号からデジタル信号を再生する際のノイズの発生を抑制できる受信回路を提供する。

【解決手段】ベースバンド信号S1のレベルが参照信号S2のレベルより高くなると、コンパレータ50において出力されるデジタル信号Doutが「0」から「1」へ変化し、ヒステリシスアンプ40のゲインが低下し、コンパレータ50に入力される参照信号S2のレベルが低くなる。また、ベースバンド信号S1のレベルが参照信号S2のレベルより低くなると、デジタル信号Doutが「0」へ変化し、ヒステリシスアンプ40のゲインが上昇し、コンパレータ50に入力される参照信号S2のレベルが高くなる。何れの場合も、デジタル信号Doutの値を維持した状態でベースバンド信号S1と参照信号S2との電圧差が広がるため、コンパレータ50の誤動作が起こりにくくなる。

(もっと読む)

1 - 10 / 32

[ Back to top ]