国際特許分類[H03K5/151]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | パルス技術 (16,231) | このサブクラス中の他のメイングループの1によっては包括されないパルス操作 (3,125) | パルスを異った時間にいくつかの出力に発生させる装置,すなわちパルス分配器 (247) | 二つの相補的な出力をもつもの (21)

国際特許分類[H03K5/151]に分類される特許

1 - 10 / 21

半導体装置

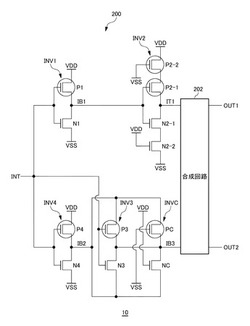

【課題】入力信号に基づいて位相の一致した相補の出力信号を生成する。

【解決手段】半導体装置に含まれるスプリッター回路10は、入力信号INTを受けて反転信号IB1を出力するインバータINV1と、反転信号IB1を受けて非反転信号IT1(第1の出力信号)を出力するインバータINV2が縦続接続される信号パスPASS1を含む。また、スプリッター回路10は、入力信号INTを受けて反転信号IB3(第2の出力信号)を出力するインバータINV3を含む信号パスPASS2を含む。また、インバータINV3と補助インバータINVCは出力信号線を共有する。インバータINV3と補助インバータINVCは、共に、入力信号INTの反転信号を電源とする。

(もっと読む)

クロックバッファ回路及びこれを用いたクロック分配回路

【課題】小さな回路規模により広帯域のクロック信号に対応できるクロックバッファ回路を提供すること。

【解決手段】本発明の一態様であるクロックバッファ回路100は、ドライバ部11及びLCタンク部21を有する。ドライバ部11は、クロック入力IN及びINBからの入力クロック信号の少なくとも正転出力を、それぞれクロック出力OUT及びOUTBへ出力する。LCタンク部は、ドライバ部11とクロック出力OUT及びOUTBとの間に配置される。ドライバ部11は、入力クロック信号の周波数に対応した制御信号に応じて、ドライバ部11の入力と出力とを短絡させるスイッチSW1及びSW2を有する。

(もっと読む)

半導体装置

【課題】マルチプレクサとクロック分割回路との間における相互の電源ノイズの影響を低減する。

【解決手段】外部クロック信号CKに基づいて内部クロック信号LCLK1を生成するDLL回路100と、内部クロック信号LCLK1に基づいて、互いに位相の異なる内部クロック信号LCLK2,LCLK2Bを生成するクロック分割回路200と、内部データ信号CD,CEに基づいて、クロック信号LCLK2,LCLK2Bにそれぞれ同期した内部データ信号DQP,DQNを出力するマルチプレクサ300とを備える。クロック分割回路200に供給される内部電源電圧VPERI2とマルチプレクサ300に供給される内部電源電圧VPERI3は、互いに異なる電源回路82,83によって生成され、且つ、該半導体装置内で分離されている。これにより、相互にノイズの影響を及ぼし合うことがなくなる。

(もっと読む)

電子機器

【課題】複数の接続部に動作クロックを出力すると、それぞれのクロックの立ち上がり及び立ち下がりにより生じる電磁波の周りへの影響が大きい。

【解決手段】電子機器は、信号の授受する動作クロックの周波数が同じ複数の外部機器が接続される複数の接続部と、複数の接続部に対して互いに位相をずらした動作クロックを出力するクロック出力部とを備える。クロック出力部は、複数の接続部のうちの2つに対して互いに逆位相の動作クロックを出力する。

(もっと読む)

クロック分配回路及びその回路を含む半導体回路装置

【課題】

半導体チップを製造する際の製造バラツキ又は半導体チップ内の半導体回路の動作条件による、複数の最終バッファから出力される複数のクロック間の位相差を軽減することが可能なクロック分配回路を提供することを目的とする。

【解決手段】

回路装置内に配置されたクロック分配回路であって、リング状のクロック配線と、前記クロック配線に接続し、自己発振により、前記クロック配線内に第1クロック信号を発生させる発振回路と、前記回路装置内において、2以上の場所それぞれに、配置され、第2クロック信号を出力する2以上の位相調整回路と、を備え、前記位相調整回路それぞれは、配置場所に応じた位相を有する前記第1クロック信号を受け取り、前記位相調整回路それぞれが受け取った前記第1クロック信号間の位相差よりも、前記位相調整回路それぞれが出力する前記第2クロック信号間の位相差を減じる調整を行うことを特徴とするクロック分配回路。

(もっと読む)

分周回路、分周装置及び電子機器

【課題】位相同期した出力信号及びその反転信号を生成・出力できる分周回路の実現。

【解決手段】分周回路1は、クロック信号生成部10と、分周信号生成部20と、出力信号生成部30とから構成される。出力信号生成部30からは、共通のクロック信号CLOCKによって動作/不動作が切り替えられるクロックドインバーターX15,X19によって、位相がほぼ完全に一致した出力信号OUT,XOUTが生成・出力される。

(もっと読む)

半導体装置

【課題】入力信号に基づいて位相の一致した相補の出力信号を生成する。

【解決手段】入力信号INTを受けて反転信号INBを出力するインバータ11と、反転信号INBを受けて内部信号INTTを出力するインバータ12と、反転信号INBを電源とし、入力信号INTを受けて内部信号INBBを出力するインバータ21と、を備える。本発明によれば、一方の信号パス上の信号を他方の信号パスに含まれるインバータの電源として用いていることから、調整用の容量や抵抗を付加することなく、一対の出力信号の位相を正確に一致させることが可能となる。

(もっと読む)

非重複クロック生成のための技術

【解決手段】望ましい周波数範囲にわたって、正確な非重複時間及びクロックフェーズ遅延時間を生成する技術が提供される。一構成において、装置はそれに結合されるクロック生成回路への制御電圧を順に生成する遅延ロックループ(DLL)回路を含む非重複クロック生成回路を備えている。制御電圧はクロック生成回路によって生成される非重複遅延クロック信号の正確なタイミング関係を維持するように動作する。一態様において、DLL回路は知られたデューティサイクルによる入力クロックを受信し、入力クロックサイクルの特定の部分へのユニット遅延をフィックスする出力制御電圧を得る。更なる態様において、クロック生成回路は製造プロセス変化とは関係ない非重複時間(tnlp)でクロック信号の第1のセットから遅延されたクロック信号の第2のセット及びクロック信号の第1のセットを生成するDLL回路に結合される複数の電圧制御遅延セルを備えている。 (もっと読む)

クロック信号生成装置

【課題】本発明は、温度特性、電源電圧特性、個体バラツキを吸収し、最適なノンオーバーラップ時間を有する2相クロック信号を確実に生成できる信頼性の高いクロック信号生成装置を提供することを目的とする。

【解決手段】本発明のクロック信号生成装置は、ノンオーバーラップクロック信号を使用する負荷回路において使用される2相クロック信号の遅延時間を可変する可変遅延器と、2相クロック信号におけるHレベル区間のノンオーバーラップ時間を検出し、ノンオーバーラップ時間に応じた検出信号を出力するノンオーバーラップ検出器と、ノンオーバーラップ検出器からの検出信号に基づいて可変遅延器を制御する制御信号を生成する制御信号生成部と、を備えている。

(もっと読む)

相補信号生成回路

【課題】 容量素子のみによるこれまでのスキュー調整方法よりもスキューの微調整を可能にした相補信号生成回路を提供する。

【解決手段】 本発明による相補信号生成回路は、複数のインバータ(901、904、905、906)を含む第1の信号伝達経路と、インバータ(901、907、908)と抵抗素子903を含む第2の伝達経路とを有する。

(もっと読む)

1 - 10 / 21

[ Back to top ]