国際特許分類[H03K5/26]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | パルス技術 (16,231) | このサブクラス中の他のメイングループの1によっては包括されないパルス操作 (3,125) | 入力信号特性,例.傾斜,積分,にもとづいてパルスまたはパルス列をお互いに比較するための2つ以上の入力と1つの出力をもつ回路 (310) | 入力信号特性が持続時間,間隔,位置,周波数または順序であるもの (305)

国際特許分類[H03K5/26]に分類される特許

301 - 305 / 305

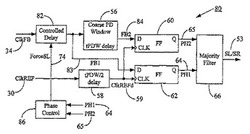

進歩した位相等化を用いたDLL位相検出

【解決手段】同期回路(例えば、遅延ロックドループ即ちDLL)の初期化中にクロックのシフトモードを開始及び終了するシステム及び方法が開示されている。初期化の際に、DLLは、ForceSL(Force Shift Left)モード及びOn1xモード(即ち、クロックサイクル毎にレフトシフト)に入る。フィードバッククロックは、(システムクロックから順次供給される)リファレンスクロックの位相をトラックし、コース位相検出ウインドウに与えられる前に、最初にコース位相検出器内で遅延される。フィードバッククロックの2つの遅延バージョンが、リファレンスクロックでサンプリングされて、一組の位相情報信号が生成される。それら信号は、その後、アドバンスド等位相(APHEQ)信号を確立するために使用される。APHEQ信号は、PHEQ(位相等化)位相のオンセットを進め、ForceSLモード及びOn1xモードの終了に使用される。これによって、クロックジッタによる不適切なForceSLの終了、又はOn1xが終了する間におけるフィードバックパスのオーバーシューティングが防止される。不適切なForceSLの終了及びOn1xのオーバーシューティングの問題が避けられることで、DLLのロッキングタイムはより速くなる。 (もっと読む)

差動位相検出器

【課題】本発明は、完全にデジタルで実装される差動位相検出器と、該差動位相検出器のための補間器に関する。

【解決手段】本発明によると、4つの光検出器のデジタル化された信号(A、B、C、D)からトラッキング誤差信号を生成する差動位相検出器は、デジタル化された信号(A、B、C、D)を時間多重するマルチプレクサと、時間多重されたデジタル化信号(A、B、C、D)からサンプルを同期化するためのデマルチプレクサ/補間器を含む。デマルチプレクサ/補間器は、好ましくは、4個の信号の時間多重信号を受信し、時間多重信号の半分の速度である4チャネルの信号を生成する。

(もっと読む)

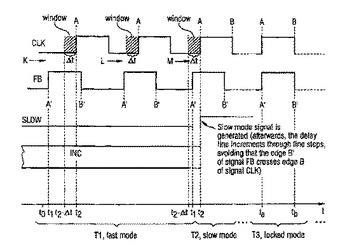

クロック信号を同期化する際に使用する装置、および、クロック信号同期化方法

本発明は、可変制御可能な遅延時間(tvar)を有する遅延手段(2)を備え、クロック信号(CLK)またはこのクロック信号(CLK)から得られる信号が、遅延手段(2)に入力され、可変制御可能な遅延時間(tvar)だけ遅延され、遅延されたクロック信号(DQS)の形状で出力される、クロック信号同期化方法、および、クロック信号(CLK)の同期化に使用する装置(1)に関するものである。本発明は、遅延手段(2)から出力される遅延されたクロック信号(DQS)またはこのクロック信号(DQS)から得られる信号(FB)の上記クロックエッジ(A’)が、上記クロック信号(CLK)またはこのクロック信号(CLK)から得られる信号の対応するクロックエッジ(A)の前の所定の時間窓の内側にあるかどうかを決定するためのデバイス(5)が設けられていることを特徴とする。  (もっと読む)

(もっと読む)

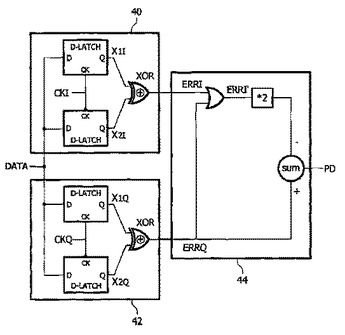

位相検出器

本発明は、データ信号DATAを用いてデータクロックDATA-CLKと参照クロックREF-CLKとの間の位相差を検出する位相検出器に関する。データ信号DATAの遷移は、データクロックDATA-CLKの遷移と同期している。データクロックDATA-CLK及び参照クロックREF-CLKは同じ周波数を持つ。位相検出器は、第1のバイナリ信号ERRQを生成する第1の信号生成器を有する。そのパルス幅は、データ信号DATAの遷移とデータ信号DATAの遷移に隣接する第1の参照クロック信号CKQの遷移との間の第1の時間差ΔT1に等しい。第1の信号生成器は、第1の参照クロック信号CKQを受信する入力と、データ信号DATAを受信する入力とを有する。位相検出器は、第2のバイナリ信号ERRIを生成する第2の信号生成器を有する。第2のバイナリ信号ERRIのパルス幅は、データ信号DATAの遷移とそのデータ信号DATAの遷移に隣接する第2の参照クロック信号CKIの遷移との間の第2の時間差ΔT2に等しい。第2の信号生成器は、第2のバイナリ信号ERRIを受信する入力と、第2の参照信号CKIを受信する入力とを有する。位相検出器は、データクロックDATA-CLKと参照クロックREF-CLKとの間の位相差を表す出力信号を生成する出力信号生成器を有する。出力信号は、ANDが論理AND演算を表すとき、ERRQ-2*(ERRQ AND ERRI)に等しいか、又はXORが論理XOR演算を表すとき、(ERRQ XOR ERRI)-ERRIに等しい。  (もっと読む)

(もっと読む)

遅延回路及びデジタル位相ロック回路

【課題】 遅延回路及びデジタル位相ロック回路に関し、任意の遅延時間を実現でき、データ信号のデューティ比劣化が少ない遅延回路、及び、それを用いた位相誤差が少ないデジタル位相ロック回路を提供する。

【解決手段】 遅延回路は、第一のバッファ・ゲートと、第二のバッファ・ゲートと、第一のバッファ・ゲートの出力端子と第二のバッファ・ゲートの入力端子とを接続する信号線と所定の電位に設定された点との間に接続される、スイッチとコンデンサとの複数の直列接続体とを有する構成を備える。又、デジタル位相ロック回路は、リング発振器に適用する遅延回路に上記遅延回路を適用する。

(もっと読む)

301 - 305 / 305

[ Back to top ]