国際特許分類[H03K5/26]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | パルス技術 (16,231) | このサブクラス中の他のメイングループの1によっては包括されないパルス操作 (3,125) | 入力信号特性,例.傾斜,積分,にもとづいてパルスまたはパルス列をお互いに比較するための2つ以上の入力と1つの出力をもつ回路 (310) | 入力信号特性が持続時間,間隔,位置,周波数または順序であるもの (305)

国際特許分類[H03K5/26]に分類される特許

201 - 210 / 305

アナログ信号比較器

【課題】

アナログ信号の値を、比較的簡易な回路でかつ短時間で、所定の値と比較する。

【解決手段】

第1のパルス信号を生成する発振器21Aと、アナログ信号を入力し当該アナログ入力信号を第2のパルス信号に変換して出力するVCO22と、発振器21からの第1のパルス信号を入力する第1のシフトレジスタ241と、VCO22からの第2のパルス信号を入力する第2のシフトレジスタ242と、第1および第2のシフトレジスタ241,242の全ビットまたは一部ビットの値を検出し、これらの検出値に基づき、発振器21Aが生成する第1のパルス信号の個数と、VCO22が生成する第2のパルス信号の個数とを比較するパルス個数比較回路とを備えたことを特徴とするアナログ信号比較器。

(もっと読む)

位相検出回路及びデータ処理装置

【課題】回路構成が簡素化され、低消費電力化され集積回路化する上で有利な構成の回路を得る。

【解決手段】第1クロックが各クロック入力端に与えられる複数段のフリップフロップ回路(Q1−Q7)と、第2クロックが入力される直列接続された複数段の遅延素子(D1−D6)と、前記複数段の遅延素子の出力をそれぞれ、前記複数段のフリップフロップ回路の各データ入力端に与える接続部(L1−L7)と、前記複数段のフリップフロップ回路の出力データが入力され、この出力データ内容に応じて変化する制御信号を得る信号生成回路(163)と、前記信号生成回路からの制御信号に応じて、前記第1若しくは第2クロックを相調整する位相調整信号を出力する位相調整信号出力部(164)を有する。

(もっと読む)

クロック信号出力回路

【課題】逓倍クロック信号の基準クロック信号に対する同期ずれを補正することができるクロック信号出力回路を提供する。

【解決手段】位相誤差補正回路12は、基準クロック信号PREFと逓倍クロック信号POUTとの位相差を検出し、その位相差に応じて、逓倍クロック信号POURの出力位相を基準クロック信号PREFに同期させる補正を、1制御周期の間に複数回実行する。

(もっと読む)

パルス幅測定方法および回路

【課題】入力パルスのデューティが測定可能となり、回路構成が簡素化できるようにする。

【解決手段】HレベルとLレベルとを繰り返す入力パルスを同一遅延時間でn+1段に亘って遅延させてn+1相の遅延パルスを生成し、該n+1相の各遅延パルスのそれぞれがHレベルであるかLレベルであるかに応じて変化し、且つ所定のタイミングにおいて、前記入力パルスのHレベル側又はLレベル側のパルス幅を示すエンコード信号を生成し、前記所定のタイミングにおける前記エンコード信号を、前記Hレベル側又はLレベル側のパルス幅信号として保持する。

(もっと読む)

オーバーサンプリング型CDR

【課題】キャリブレーション中であってもデータ受信を可能とする。

【解決手段】本発明は、位相のずれた第1クロック及び第2クロックを含む多相クロックが入力されるオーバーサンプリング型CDRであって、入力信号及びクロックが入力され、クロックのタイミングに合わせて入力信号を取り込んで出力信号を出力する第1差動対及び第2差動対と、第1差動対がキャリブレーション時に第1クロックを第2差動対に出力するクロックセレクタと、を備え、第1差動対は、クロックとして第1クロックが入力されると、第1クロックのタイミングに合わせて入力信号を取り込んで前記出力信号として第1データ出力信号を出力し、第2差動対は、クロックとして第1クロックが入力されると、第1クロックのタイミングに合わせて入力信号を取り込んで出力信号として第1データ出力信号を出力するものである。

(もっと読む)

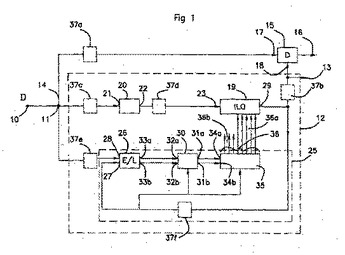

外部制御を必要としないデジタル位相ロックによるクロック抽出装置

本発明は、注入ロック発振器(19)と、デジタル位相検出器(26)を有する位相制御ループ(25)とを備えた、ベースバンドシリアル信号からクロックを抽出する装置に関する。発振器(19)はその周波数の値を制御するデジタル制御入力部(24)を備え、位相制御ループ(25)は、デジタル位相検出器(26)から供給されるデジタル信号の相対値を累算し、発振器(19)用のデジタル形態の制御信号を渡す、カウント回路(30、35)を備える。  (もっと読む)

(もっと読む)

位相差計測回路

【課題】2つの信号の進み遅れに関係なく、遷移タイミングの差を測定することができる位相差計測回路を提供する。

【解決手段】EXOR11により、デジタル信号S1,S2の位相差に対応したパルス幅の信号S3が出力される。信号S3は、インバータ12で反転された信号S4と共にセレクタ13に与えられ、選択信号SELに従っていずれか一方が選択され、ゲート制御用の信号S5としてADN14に与えられる。AND14には連続したクロック信号CLKが与えられており、信号S5でゲート制御されたクロック信号CLKが、信号S6としてカウンタ15に与えられる。カウンタ15は、信号S6のパルス数をカウントし、カウント値CNTを出力する。選択信号で信号S3,S4を選択することにより、デジタル信号S1,S2の進み遅れに関係なく、遷移タイミングの差を測定できる。

(もっと読む)

デジタルシンセサイザ

【課題】位相比較器および信号発振器をデジタル化することによって短時間に同期を確立し、同期状態を高精度でしかも高安定に保持することができるデジタルシンセサイザあるいはデジタル同期発振器を提供する。

【解決手段】少なくとも、デジタル位相比較器21と、デジタル制御発振器22と、分周器23から構成する。

【効果】通信システムにおいて同じ周波数であることが必須の2つの入力信号の間で短時間に同期を確立し、入力信号が停止した場合あるいは取去られた場合にも、同期状態を高精度でしかも高安定に保持する。

(もっと読む)

電圧制御発振器を内蔵したPLL(PhaseLockedLoop)回路の位相差検出回路

【課題】低電圧動作時においても、VCO信号と基準信号との位相差を検知し、その位相差に対応したデジタル信号を生成する位相比較器を提供する。

【解決手段】基準信号と対象信号との位相差をデジタル信号として出力する位相比較器において、前記位相差に対応したパルス幅の信号により第1容量素子を充電することによって前記位相差を電荷として検出する第1検出手段と、前記基準信号の周期に対応したパルス幅の信号により第2容量素子を充電することによって基準となる時間差を基準電荷として検出する第2検出手段と、前記第1検出手段により検出された電荷と前記第2検出手段により検出された電荷とを比較する電荷比較手段と、前記電荷比較手段による比較結果により、前記第2容量素子に充電された電荷に対する前記第1容量素子に充電された電荷の比をデジタル信号として出力する出力手段と、を備える。

(もっと読む)

半導体集積回路およびイコライザの制御方法

【課題】回路規模の増大を抑制しつつ、受信したデータ信号の等化量を調整することが可能な半導体集積回路を提供する。

【解決手段】半導体集積回路100は、イコライザと、イコライザにより等化されたデータ信号の位相を検出しこのデータ信号の位相と復元クロック信号の位相とを比較し、等化されたデータ信号のビット幅が復元クロック信号の周期よりも小さいときは第1の比較信号を出力し、一方、大きいときは第2の比較信号を出力し、復元クロック信号の位相がデータ信号の位相よりも進んでいる場合には第3の比較信号を出力し、遅れている場合には第4の比較信号を出力する位相比較回路と、第3、第4の比較信号および基準クロック信号に基づいて、復元クロック信号を生成する復元クロック生成回路と、少なくとも第1、第2の比較信号に基づいて、イコライザのピーキング量を制御する制御回路と、を備える。

(もっと読む)

201 - 210 / 305

[ Back to top ]