国際特許分類[H03K5/26]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | パルス技術 (16,231) | このサブクラス中の他のメイングループの1によっては包括されないパルス操作 (3,125) | 入力信号特性,例.傾斜,積分,にもとづいてパルスまたはパルス列をお互いに比較するための2つ以上の入力と1つの出力をもつ回路 (310) | 入力信号特性が持続時間,間隔,位置,周波数または順序であるもの (305)

国際特許分類[H03K5/26]に分類される特許

171 - 180 / 305

周波数異常検出回路

【課題】従来の、監視クロックが被監視クロックよりも高い周波数を使用する周波数異常検出回路は、高コストかつノイズ対策が必要で実装が困難であり、また、監視クロックが被監視クロックよりも低い周波数を使用する周波数異常検出回路は、クロック固着のタイミングによっては異常を検出できないだけでなく、リセット時にシフトレジスタを構成するすべてのレジスタ出力が“0”となるので、警報が発出されないようにする構成を別途設けなければならない問題があった。

【解決手段】クロック周波数の上限異常は被監視クロック数のカウント数と上限値との大小比較にて検出し、下限異常は、同期化した監視クロックの立ち上がりエッジにて出力する正極性パルスと、当該パルス出力で”High”を出力する初回エッジホールド回路出力と、下限値と被監視クロック数のカウント値の大小を比較するコンパレータ出力との論理積の出力にて検出すること。

(もっと読む)

位相比較器、位相同期回路及び位相比較制御方法

【課題】入力断検出部を位相比較器に内蔵することで位相比較器を実装するPLL回路の小型化を図る。

【解決手段】参照信号を入力すると共に、参照信号に基づく被参照信号を帰還入力し、これら入力した参照信号及び被参照信号の立ち上がりエッジを検出し、参照信号の立ち上がりエッジ及び被参照信号の立ち上がりエッジ間の位相差を検出する位相差検出部21と、位相差検出部21にて検出した位相差に基づき、位相差を小さくすべく、定電流出力動作を実行する定電流出力部24と、被参照信号のエッジを検出した後、参照信号のエッジを検出する前に、被参照信号のエッジを再度検出した場合、参照信号の入力断として検出する入力断検出部23とを有している。

(もっと読む)

パルス発生回路及びパルス発生回路を備えた電子機器

【課題】PVTに依存せずに安定した周波数を出力する。

【解決手段】出力する第1の出力信号Vf1の周波数を第1の制御電圧VC1で制御する第1の電圧制御発振器11と、第1の出力信号Vf1及び基準信号CLKに基づき第1の出力信号Vf1の周波数を一定に維持する第1の制御電圧VC1を生成する制御電圧生成部13と、を含む位相同期回路10と、出力する第2の出力信号Vf2の周波数を第2の制御電圧VC2で制御する第2の電圧制御発振器20と、第1の制御電圧VC1に基づき第2の出力信号Vf2の周波数を一定に維持する第2の制御電圧VC2を生成する制御電圧変換部30と、を含むパルス発生回路1。

(もっと読む)

タイミングリカバリー回路

【課題】 構成を簡易にしたタイミングリカバリー回路を提供する。

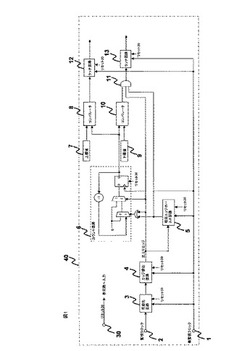

【解決手段】 クロック入力信号に対するデータ入力信号の位相差を検出して位相差信号を出力すると共に異常時に異常信号を出力する位相比較器100と、VCXO109の制御電圧の中間値若しくはその付近の値の電圧が定電圧として供給され、平滑化された位相差信号と定電圧とを比較し、両信号の差分によりクロック入力信号に対するデータ入力信号の位相が進んでいる場合は位相を遅らせる制御電圧を、位相が遅れている場合は位相を進める制御電圧をVCXO109に出力するオペアンプ105と、オペアンプ105の位相差信号が入力される端子とVCXO109の入力端子との接続を制御し、異常信号によって接続をオンにするスイッチとを有するタイミングリカバリー回路である。

(もっと読む)

半導体集積回路

【課題】出力バッファを必要とせずに多相クロックの位相状態の検出を可能にする半導体集積装置を提供する。

【解決手段】半導体集積回路1Aは、集積化された論理演算回路12、クロック生成器10、中継回路11および信号生成部13を有する。クロック生成器10は、多相クロックMP0を生成する。中継回路11は、当該生成された多相クロックMP0を論理演算回路12に分配する。信号生成部13は、当該分配された多相クロックMP1の位相状態を検出し、当該検出された位相状態に基づいて多相クロックMP1の位相誤差を表す電圧値を持つアナログ電圧信号LV0,LV1を生成する。

(もっと読む)

半導体集積回路装置

【課題】遅延を有する論理回路から検出した信号を直接利用して、その論理回路の電源電圧の制御を行うような機構が求められている。

【解決手段】本発明は、本発明は、論理回路と、前記論理回路の遅延の変化に応じた周波数の検出信号を出力する遅延特性検出回路と、前記検出信号に応じて抵抗値が変化する抵抗素子と、前記抵抗素子の抵抗値の変化に応じて参照電圧を出力する参照電圧生成回路と、前記参照電圧を前記論理回路及び遅延特性検出回路に出力する電圧供給回路とを有する半導体集積回路装置である。

(もっと読む)

位相制御回路

【課題】 データ信号とクロック信号がどのような位相差であっても位相差に応じたパルス幅の位相差信号を出力する。

【解決手段】 データ信号および反転した信号Yを入力し、反転した信号Yをデータ信号の遷移タイミングで保持して信号Xを出力する第1の保持手段と、クロック信号および信号Xを入力し、信号Xをクロック信号の遷移タイミングで保持して信号Yを出力する第2の保持手段と、信号Xおよび信号Yを入力し、その位相差に応じたパルス幅を有する位相差信号を生成し、データ信号とクロック信号の位相差に応じたパルス幅を有する位相差信号として出力する比較手段とを備える。

(もっと読む)

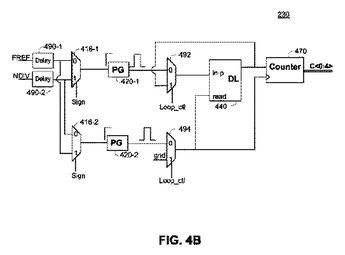

完全デジタル位相ロックループにおける位相デジタル変換器

位相デジタル変換器と、完全デジタル位相ロックループと、完全デジタル位相ロックループを有する装置とについて、本明細書で説明する。位相デジタル変換器は、時間デジタル変換器を駆動する位相周波数変換器を含む。時間デジタル変換器は、位相周波数変換器によって出力された位相差の絶対値と符号とを判断する。時間デジタル変換器は、タップ付き遅延線とループフィードバックカウンタとを利用して、ループ追跡プロセスによくある小さいタイミング差およびループ収集プロセスによくある大きいタイミング差の測定を可能にする。タップ付き遅延線は、基準期間の部分の測定を可能にし、基準クロックの速度に関する要件を低減することによって位相デジタル変換器のより低電力の動作を可能にする。  (もっと読む)

(もっと読む)

信号処理装置

【課題】0と1の出現確率が異なるデータ信号のデューティサイクルの歪みを補正する。

【解決手段】位相検出回路21は、0と1の出現確率が異なるデータ信号の位相の進みおよび遅れを検出する。AND回路43はデータ信号の立ち上がりを検出し、AND回路44は立ち下がりを検出する。+DCD検出回路45は、位相検出回路21とAND回路43および44の検出結果に基づいて、デューティサイクルのプラス側の歪みを検出し、−DCD検出回路46は、デューティサイクルのマイナス側の歪みを検出する。デューティ調整回路12は、+DCD検出回路45と−DCD検出回路46の検出結果に基づいて、デューティサイクルを調整することにより、デューティサイクルの歪みを補正する。本発明は、例えば、データ信号を受信する受信装置に適用することができる。

(もっと読む)

クロック信号分周回路および方法

【課題】大きな回路規模を必要とすることなく、有理数分周した出力クロック信号のサイクル時間変動を抑制するとともに、分周時に出力クロック信号の位相を調整する。

【解決手段】クロック選択制御回路100により、入力クロック信号のサイクルごとに、分周比に応じた一定サイクル時間を有する基準分周クロック信号と入力クロック信号との位相関係を示す位相計算値111を計算するとともに、位相調整信号に応じてその値を増減し、この位相計算値111に基づいて、出力動作のうち、基準分周クロック信号の位相と近いクロック信号を生成するための出力動作を指示する制御信号102,103を生成する。クロック選択回路101により、制御信号102,103に基づいて、入力クロック信号のクロックパルスをそのまま非反転で出力するか、反転して出力するか、マスクして出力しないか、のいずれかの出力動作を選択して実行することにより、出力クロック信号を生成する。

(もっと読む)

171 - 180 / 305

[ Back to top ]