国際特許分類[H03K5/26]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | パルス技術 (16,231) | このサブクラス中の他のメイングループの1によっては包括されないパルス操作 (3,125) | 入力信号特性,例.傾斜,積分,にもとづいてパルスまたはパルス列をお互いに比較するための2つ以上の入力と1つの出力をもつ回路 (310) | 入力信号特性が持続時間,間隔,位置,周波数または順序であるもの (305)

国際特許分類[H03K5/26]に分類される特許

131 - 140 / 305

インピーダンス調整回路及びこれを備える半導体装置

【課題】インピーダンス調整回路における調整誤差を低減する。

【解決手段】レプリカ回路1441,1443のインピーダンスをそれぞれ変化させるカウンタ回路1421,1422と、これらカウンタ回路のカウント値を更新するインピーダンス調整制御回路141とを備える。制御回路141は、レプリカ回路1441のインピーダンスが外部抵抗REのインピーダンスよりも低い状態から高い状態に変化したことに応答してカウンタ回路1421のカウント値更新を終了し、レプリカ回路1443のインピーダンスがレプリカ回路1441のインピーダンスよりも高い状態から低い状態に変化したことに応答してカウンタ回路1422のカウント値更新を終了する。これにより、レプリカ回路1441,1443にて生じる調整誤差が相殺される。

(もっと読む)

クロック生成回路

【課題】高速動作するクロック・データリカバリのための正確なクロック信号を生成するクロック生成回路を提供する。

【解決手段】クロック生成回路は、第1入力電圧に応じて第1周波数信号を出力する第1電圧制御発振回路と、第2入力電圧に応じて第2周波数信号を出力する第2電圧制御発振回路と、制御信号を受け取り、第1周波数信号と第2周波数信号との位相差が制御信号に応じた値になるように第1入力電圧と第2入力電圧とを制御する位相調整回路と、第1周波数信号に同期して受信信号を検出して出力する第1判定回路と、第2周波数信号に同期して受信信号を検出して出力する第2判定回路と、第1判定回路の出力と第2判定回路の出力とに基づいて受信信号の位相を検出し、その位相検出の結果に応じて第1入力電圧と第2入力電圧とを制御する位相検出器とを含む。

(もっと読む)

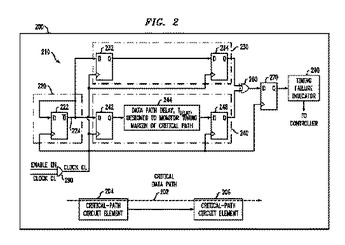

性能監視用クリティカルパス回路

目標タイミング・マージンを有する、クリティカルパス中のタイミングを監視する監視回路を含む集積回路が、開示される。監視回路は、2つのシフト・レジスタを含み、シフト・レジスタの1つは、受領信号に遅延値を加える遅延素子を含む。2つのシフト・レジスタの入力部は、入力信号を受領することができる信号入力ノードを形成する。監視回路は、出力部および少なくとも2つの入力部を有する論理ゲートも含み、各入力部は、2つのシフト・レジスタの出力部の対応する1つに接続される。論理ゲートの出力部は、目標タイミング・マージンが満足されるか、または満足されないかを示す。  (もっと読む)

(もっと読む)

クロック生成回路

【課題】広帯域の周波数範囲におけるどの周波数の基準クロックを受けてもロックする時間を短くできるクロック生成回路を簡易な回路構成で実現。

【解決手段】基準クロックを第1の個数の電圧制御遅延素子12−1〜12−Nで遅延させて第1の遅延クロックを生成し、第2の個数の電圧制御遅延素子12−1〜12−Kで遅延させて第2の遅延クロックを生成する遅延部11と、前記基準クロックの位相と前記第1の遅延クロックの位相とを比較する位相比較部21と、遅延制御電流を出力するチャージポンプ22と、遅延制御部23と、前記基準クロックの位相と前記第2の遅延クロックの位相とを比較し、前記基準クロックと前記第1の遅延クロックとの位相差を判定する判定部13aと、前記位相差が閾値より大きい場合、前記遅延制御電流が第1の値になり、前記閾値以下の場合、前記第1の値より小さい第2の値になるように制御するチャージ制御部13bとを備える。

(もっと読む)

PLL回路

【課題】感度関数と相補感度関数の両方が低減されたPLL回路を提供する。

【解決手段】本発明のPLL回路10は、一般的なPLL回路の構成を備えた第1ループ50と、相補感度関数を低減するための第2ループ52とを備えて構成されている。第1ループ50では、周波数が高い基準クロック34を用いて比較部14にて位相比較を行うことにより、感度関数を下げている。そして、第2ループ52からの出力により電流補償部16にて電流値を補完することにより、相補感度関数を下げている。

(もっと読む)

高性能信号発生

【課題】高性能位相検出器は、プログラムで制御できる周波数および位相を有するデジタル基準信号を生成する局部デジタルオシレータを含む。

【解決手段】位相検出器は、デジタル基準信号とサンプリングされた入力信号の間の位相差を蓄積し、位相誤差の指標を作る。位相検出器は、周波数合成器において用いられ、低位相ノイズおよび正確な位相制御で信号を発生することができる利点がある。さらに、この種類のシンセサイザは、低ジッタのクロックおよび波形を生成するATEシステムおよび他の電子システムにおいて、ビルディングブロックのように用いられる。

(もっと読む)

2相カウンタおよびカウンタシステム

【課題】カウント動作を高速でも容易に行えるようにすること。

【解決手段】A相パルスの前パルスエッジとB相パルスの前パルスエッジとのエッジ位相差と、A相パルスの後パルスエッジとB相パルスの前パルスエッジとのエッジ位相差とを検出し、上記両エッジ位相差の比率を演算し、上記エッジ位相差比率に対応して割り当てられたカウント値を演算する2相カウンタ。

(もっと読む)

データ復元回路、データ復元方法、及びデータ受信装置

【課題】安定した動作を容易に実現することができるデータ復元回路を提供する。

【解決手段】データ復元回路は、データ列を表す入力アナログ信号をクロック信号に同期してアナログデジタル変換することにより、前記データ列のデータ間隔より短い間隔でサンプルしたデジタルコードの列を生成するアナログデジタル変換器と、前記デジタルコードが値を取り得る範囲の略中心にある所定のコード値の位置と前記デジタルコードの列を補間して得られる線分とが交差するクロス点の位置を前記デジタルコードの列から算出する位相検出器と、前記クロス点の位置に基づいて前記データ列のデータ中心点の推定位置を求める位相推定器と、前記クロス点の位置と前記データ中心点の推定位置とに基づいて前記デジタルコードの列からデータ判定値の列を抽出するデータ判定部とを含む。

(もっと読む)

タイム/デジタルコンバーター及びデジタル位相ロックループ

【課題】 本発明の目的は、入力される2つの信号の位相差だけでなく周波数の差まで検出することができるタイム/デジタルコンバーター及びこれを用いるデジタル位相ロックループを提供することを目的とする。

【解決手段】 タイム/デジタルコンバーターが開示される。本タイム/デジタルコンバーターは、第1信号及び第2信号を受信し、直列接続された複数の遅延素子を用いて第2信号を段階的に遅延させ、遅延された第2信号と第1信号とを比較して第1信号に対する第2信号の位相エラーを出力するコンバーターと、第1信号及び複数の遅延素子のノードのうち一つのノードから第3信号を受信し、第1信号及び第3信号に対する位相差を出力する位相周波数検出器と、位相周波数検出器の出力信号と第2信号を用いて、第1信号に対する第2信号の周波数エラーをデジタルコードに出力する周波数検出器と、を含む。これにより、本タイム/デジタルコンバーターは入力される2つの信号間の位相差だけでなく周波数の差まで検出することができる。

(もっと読む)

半導体集積回路装置

【課題】DLL回路においてロックはずれが発生しても、短時間で確実に正常ロック状態に復帰させる。

【解決手段】遅延回路13の遅延時間が1周期より小さくなると、遅延検出回路15から最小遅延時間検出信号K2が出力される。さらに位相周波数比較器11がUPパルスを出力していると、最小遅延時間検出信号K2とUPパルスとの2NOR論理(否定論理和回路21)によりクロックがUPパルスカウンタ19に伝達し、Hレベルのロックはずれ検出信号K3が出力され、リセット期間保持カウンタ17にLレベルが入力される。これにより、リセット期間保持カウンタ17がカウンタ動作を開始し、所定の期間、リセット信号をLレベルにして制御電圧CNTLを電源電圧にショートし、かつ位相周波数比較器11をリセットする。

(もっと読む)

131 - 140 / 305

[ Back to top ]