国際特許分類[H03K5/26]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | パルス技術 (16,231) | このサブクラス中の他のメイングループの1によっては包括されないパルス操作 (3,125) | 入力信号特性,例.傾斜,積分,にもとづいてパルスまたはパルス列をお互いに比較するための2つ以上の入力と1つの出力をもつ回路 (310) | 入力信号特性が持続時間,間隔,位置,周波数または順序であるもの (305)

国際特許分類[H03K5/26]に分類される特許

141 - 150 / 305

位相比較器、PLL回路、及び位相比較器の制御方法

【課題】電圧制御発振器VCOの出力信号と参照信号との位相差をデジタル信号として高精度に検知できる位相比較器、PLL回路、及び位相比較器の制御方法を提供する。

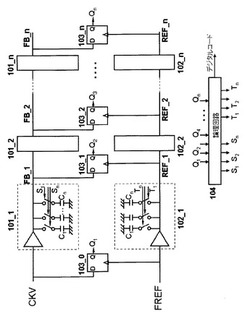

【解決手段】各々複数段縦列接続され、基準信号および対象信号が入力される遅延回路と、各々の段の遅延時間の差により、基準信号と対象信号との位相差を出力する保持回路と、その出力結果を元に、遅延素子の時間差及び大小を変更する論理回路とを備えた。

(もっと読む)

半導体集積回路装置および遅延路の制御方法

【課題】電力効率を向上させる。

【解決手段】クロック信号CLKに同期して動作する2つの同期動作回路11、12間を並列形態で接続して信号伝送可能とされる複数の遅延路13a、13b、・・13nと、複数の遅延路13a、13b、・・13nにおけるそれぞれの遅延時間を検出する遅延検出部14と、遅延検出部14の検出結果に基づいて複数の遅延路13a、13b、・・13nの内の一の遅延路を選択し、選択した一の遅延路以外における信号伝送を阻止するように制御する制御部15と、を備える。

(もっと読む)

位相検出回路

【課題】位相ロックループ周波数シンセサイザ設計における、大きな電圧制御発振器範囲(例えば、487MHz)、(例えば)1.2V電力供給電圧、および低い電力消費の要求を達成する。

【解決手段】位相検出回路は、参照信号を受信するように構成された参照入力と、フィードバック経路においてディバイダ回路からの分周信号を受信するように構成されたフィードバック入力と、参照信号と分周信号の間の周波数及び位相関係に従って位相ロックループ内のチャージポンプを制御するための制御パルスを生成するように構成されたパルス生成回路と、を有し、分周信号は、分周信号の周期の半分よりも短い長さを具備するパルスを有し、且つ、パルス生成回路は、分周信号のエッジ及び参照信号のエッジから制御パルスのエッジを定義するように、分周信号のパルスをマスクとして使用して参照信号をマスキングすることにより、制御パルスを生成するように構成されている。

(もっと読む)

PLL(PHASELOCKEDLOOP)回路内のチャージポンプリークに起因した制御電圧リプルを最小化する技術

【解決手段】位相ロックループ回路を含む装置においてチャージポンプリーク電流の影響を和らげるようループフィルタのサンプリング間隔を適切に制御する技術を提供する。一態様において、装置は電圧制御発振器(VCO)、位相周波数検知部(PFD)、VCOを固定するための制御電圧を提供するループフィルタ、及びUPパルスDOWNパルスの少なくともいずれか1つに応じてループフィルタに出力信号を供給するよう構成されたチャージポンプを含む。ループフィルタの入力とチャージポンプの出力との間で結合されサンプリング間隔によって特徴付けられたスイッチを含む。サンプリングスイッチ制御部は位相比較動作の前にスイッチを閉じ位相比較動作が完了するとスイッチを開くことでチャージポンプからのリーク電流の影響を和らげるようサンプリング間隔幅を適切に制御するよう構成される。 (もっと読む)

DLL回路及びその制御方法

【課題】本発明は、短いロッキングタイムを有する多相DLL回路及びその制御方法を提供する。

【解決手段】本発明のDLL回路は、 基準クロックを遅延させてDLLクロックを生成するが、制御電圧のレベルに応じて遅延量を調整する遅延手段;制御電圧の初期レベルを制御し、検出イネーブル信号を生成する初期動作制御手段;及び、検出イネーブル信号に応じて前記基準クロック及びDLLクロックの位相を比較して、制御電圧を生成する遅延制御手段を含むことを特徴とする。

(もっと読む)

デューティ感知回路およびこれを備えるデューティ補正回路

【課題】デューティ補正回路のロッキングタイムを減らし、正確なデューティの補正が可能となり、多様な周波数のクロックについてデューティ補正を可能にするデューティ補正回路を提供すること。

【解決手段】本発明に係るデューティ補正回路は、デューティ調節コードC<1:5>に応答して入力クロックCLK、CLKBのデューティを調節した出力クロックCLK_OUT、CLKB_OUTを生成するデューティ調節部110と、前記出力クロックのハイパルス幅とローパルス幅の差異を測定してその差異値S<1:4>を出力するデューティ感知部120と、前記差異値を累積して前記デューティ調節コードを生成する累積部130とを備える。

(もっと読む)

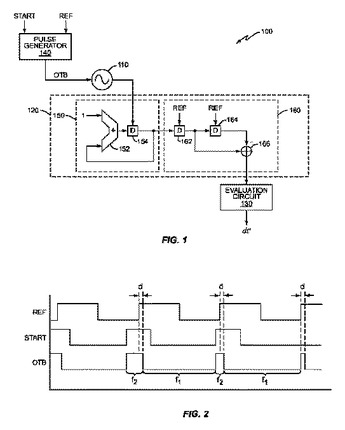

ノイズシェーピング時間測定回路

時間測定回路のある実施形態では、リファレンス信号期間の第1の部分においてデジタル制御発振器(DCO)を第1の周波数で動作させ、前記対象信号と前記リファレンス信号との時間差に応じて前記リファレンス信号期間中に動作周波数を前記第1の周波数から第2の周波数に変更することにより、対象信号とリファレンス信号の時間差が測定される。時間測定回路は、前記リファレンス信号期間において前記デジタル制御発振器の出力で何回の信号遷移が発生したかを継続的に計数する。対象信号とリファレンス信号の時間差は、前記リファレンス信号期間において計数された前記信号遷移の回数に基づいて推定される。

(もっと読む)

(もっと読む)

半導体装置、内部信号タイミング回路、及び遅延時間測定方法

【課題】内部信号のタイミングを測定する場合、チップ内に形成されたトランジスタ等の素子における場所依存性によって特性が異なる場合にも、内部信号のタイミングを測定できる測定回路を提供する。

【解決手段】内部で実信号として用いられる第1及び第2の内部回路制御信号を生成する内部回路と、内部回路を通して受信される第1及び第2の内部回路制御信号を遅延時間測定開始信号及び遅延時間測定終了信号として受け、当該遅延時間測定開始信号及び遅延時間測定終了信号間の遅延時間を測定し、出力する遅延時間測定回路を備えた内部信号タイミング回路及び当該回路を含む半導体装置。

(もっと読む)

PLL回路

【課題】PLL回路において、アナログ回路のデジタル化によって生じる量子化雑音を抑制することができる技術を提供する。

【解決手段】基準信号REFと分周後の信号DIVとの位相及び周波数を比較してデジタル値に変換するデジタル位相周波数比較器(DPFD)101と、デジタル位相周波数比較器101の出力から高周波雑音成分を除去するデジタルループフィルタ(DLF)102と、デジタルループフィルタ102の出力のデジタル値をアナログ値に変換するデジタルアナログ変換器(DAC)105と、デジタルアナログ変換器105の出力から高周波雑音成分を除去するアナログフィルタ(AnF)106と、アナログフィルタ106の出力に基づいて周波数が制御される電圧制御発振器(VCO)103と、電圧制御発振器103の出力を分周し、分周後の信号DIVを出力する分周器(DIV)104とを備える。

(もっと読む)

半導体装置

【課題】PVT変動による遅延制御回路の遅延量変動を正しく補正する。

【解決手段】互いに動作条件が異なる第1及び第2の遅延素子列121,122と、第1及び第2の遅延素子列121,122に同時に入力されたパルス信号Pの伝搬速度差を検出する検出回路123と、検出回路123による検出結果に基づいて選択信号SELを生成する設定回路124とを備える。選択信号SELは、基準信号を遅延させることによって動作タイミング信号を生成する遅延制御回路130に供給され、その遅延量は選択信号SELによって調整される。これにより、PVT変動を見越して遅延制御回路の遅延量を大きく設計しておく必要がなくなるため、パフォーマンスの低下を防止することが可能となる。

(もっと読む)

141 - 150 / 305

[ Back to top ]