国際特許分類[H03K5/26]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | パルス技術 (16,231) | このサブクラス中の他のメイングループの1によっては包括されないパルス操作 (3,125) | 入力信号特性,例.傾斜,積分,にもとづいてパルスまたはパルス列をお互いに比較するための2つ以上の入力と1つの出力をもつ回路 (310) | 入力信号特性が持続時間,間隔,位置,周波数または順序であるもの (305)

国際特許分類[H03K5/26]に分類される特許

181 - 190 / 305

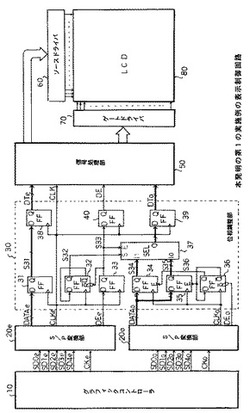

位相調整回路

【課題】大きな位相ずれにも対応可能な位相調整回路を提供する。

【解決手段】基準となるクロック信号CLKeに同期して与えられる画像データDATAeとデータイネーブル信号DEeは、このクロック信号CLKeで動作するFF31,33,38,40で2クロック分遅延され、画像データDTeと共通のデータイネーブル信号DEとして出力される。位相調整の対象となるクロック信号CLKoに同期して与えられる連続する2つの画像データDATAoは、それぞれFF34,35によって2クロック周期の間保持される。FF34,35の保持データは、セレクタ37によっていずれか一方が選択出力され、基準となるクロック信号CLKeのタイミングでFF39に保持されて画像データDToとして出力される。これにより、位相のずれがクロック周期よりも小さければ、2系統の画像データは同位相になるように位相調整ができる。

(もっと読む)

高速時間ディジタル・コンバータ

【解決手段】 時間ディジタル・コンバータ(TDC)がサブ・インバータ遅延分解能でサンプリングすることを可能にするための手法が開示されている。一実施形態では、TDC中の差動型D−Qフリップフロップへの入力は、シングルエンド型信号、およびこの信号の遅延された形態および反転された形態に接続されてこの信号の時間補間を可能にする。さらに、TDC中の第1遅延ラインおよび相補な遅延ラインの負荷の平衡を保つための手法が開示されている。 (もっと読む)

位相検出装置、位相比較装置およびクロック同期装置

【課題】クロック同期システムに用いる位相比較器として、次段のカウンタに影響を与えることなく、クロックの同期がとれた際に確実にロックをかけること。

【解決手段】本発明は、基準クロックの位相に対する比較クロックの位相のずれを検出する第1の位相比較部K1aと、基準クロックおよび比較クロックのいずれか一方について所定時間遅延または進んだ状態での両クロックの位相のずれを検出する第2の位相比較部K1bと、第1の位相比較部K1aの出力と第2の位相比較部K1bの出力との論理積を位相ずれの検出結果として出力する論理積部AND1とを備える

(もっと読む)

フリップフロップ回路

【課題】不感帯が少なく高速安定動作が可能なフリップフロップ回路を提供すること。

【解決手段】本発明は、データ信号Dと、立ち上がり遅延クロック信号CKdとを入力し、データ信号Dの立ち下がりと立ち上がり遅延クロック信号CKdの立ち下がりとによって内部ノードNCの信号を立ち上げる第1のラッチ回路L1と、内部ノードNCの信号とクロック信号CKとを入力し、内部ノードNCの信号が立ち上がっている状態でクロック信号CKが立ち下がるタイミングにより内部ノードXの信号を立ち下げる第2のラッチ回路L2と、内部ノードXの信号とクロック信号CKとを入力し、クロック信号CKが立ち上がっている状態でのデータ信号Dを保持する出力信号を生成するための第3のラッチ回路L3と、内部ノードNCの信号を立ち上がり遅延クロック信号CKdによってプルダウンさせるプルダウン回路PDとを備えるフリップフロップ回路である。

(もっと読む)

半導体集積回路

【課題】低消費電力化に適したAVS技術又はDVS技術を実現した半導体集積回路を提供すること。

【解決手段】半導体集積回路は、クリティカル・パスを形成する第1のフリップ・フロップ、組み合わせ回路及び第2のフリップ・フロップと、前記組み合わせ回路の後段に設けられる第1の遅延回路及び第3のフリップ・フロップと、前記組み合わせ回路の後段に設けられる第2の遅延回路及び第4のフリップ・フロップと、第2のフリップ・フロップの出力と第3のフリップ・フロップの出力とを比較する第1の比較回路と、第2のフリップ・フロップの出力と第4のフリップ・フロップの出力とを比較する第2の比較回路と、これら比較回路の出力に応じて、前記組み合わせ回路に供給される電源電圧を制御する制御回路とを備える。なお、第1の遅延回路による遅延時間と第2の遅延回路による遅延時間は異なる。

(もっと読む)

半導体集積回路装置および逓倍クロック生成方法

【課題】 エージング時に使用可能な同期逓倍クロック発生回路を提供することである。

【解決手段】 可変ディレイヤを用いた発振回路と、カウンタを用いた発振周波数制御回路とを有し、入力クロック周波数の逓倍の周波数のクロックを発生するクロック発生回路において、上記発振回路を入力クロックに同期させて動作させることで、入力クロックと同期した逓倍クロックを発生させる。

(もっと読む)

試験測定装置並びに位相拘束ループ及び方法

【課題】消費電力が大きくなく、位相ノイズが小さく、広い同調範囲のPLLを提供する。

【解決手段】位相検出器34は、基準信号路30及び帰還信号路32から入力の位相差を検出し、位相検出器出力を発生する。発振器32は、位相検出器出力に応答し且つこの位相検出器出力に基づいた発振出力Foutを発生する。この発振出力Foutが帰還信号路32に供給される。基準信号路30内のミキサ74は、基準信号Frefをダイレクト・デジタル・シンセサイザ72からの出力と混合する。基準信号路内のスイッチング機構80は、複数の異なるフィルタの1つを選択的にミキサ及び位相検出器の間に直列に配置する。

(もっと読む)

位相同期装置

【課題】本発明は、短いロッキングタイムを有しながらも、安定的に動作できる位相同期装置を提供する。

【解決手段】本発明の位相同期装置は、入力クロックを所定の分周比で分周した後、順次遅延させる動作により周波数を判別し、前記判別された周波数情報を用いて発振器ゲイン設定信号を生成する発振器ゲイン設定手段と、前記入力クロックに応じて、前記発振器ゲイン設定信号に対応する周波数を有する出力クロックを発振させるPLL回路を含むことを特徴とする。

(もっと読む)

物体検出回路及びそれを備えた物体検出装置

【課題】受光素子にて検知されたパルス光の波長が判別可能であり、外乱光による影響をさらに低減し、検出精度の高い物体検出回路を実現する。

【解決手段】物体検出回路1は、パルス変調された光を照射する発光素子12と、被検出物体の有無に応じて発光素子12からの出力パルス光を受光する受光素子13と、受光素子13にて検知されたパルス光の波長を判別する信号検出回路19とを備える。

(もっと読む)

位相調整回路および試験装置

【課題】被測定信号の位相を、基準信号の位相に精度よく合わせることができる位相調整回路を提供する。

【解決手段】被測定信号の位相を調整する位相調整回路であって、トリガ信号を生成するトリガ発生部と、基準信号を受け取り、共通の前記トリガ信号のタイミングで、被測定信号および基準信号を測定し、被測定信号および基準信号のそれぞれの信号レベルの差分に応じた測定結果を出力するレベル比較部と、レベル比較部が出力する信号レベルの差分が略零となるように、被測定信号の位相を調整する信号位相調整部とを備える位相調整回路を提供する。

(もっと読む)

181 - 190 / 305

[ Back to top ]