国際特許分類[H03K5/26]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | パルス技術 (16,231) | このサブクラス中の他のメイングループの1によっては包括されないパルス操作 (3,125) | 入力信号特性,例.傾斜,積分,にもとづいてパルスまたはパルス列をお互いに比較するための2つ以上の入力と1つの出力をもつ回路 (310) | 入力信号特性が持続時間,間隔,位置,周波数または順序であるもの (305)

国際特許分類[H03K5/26]に分類される特許

91 - 100 / 305

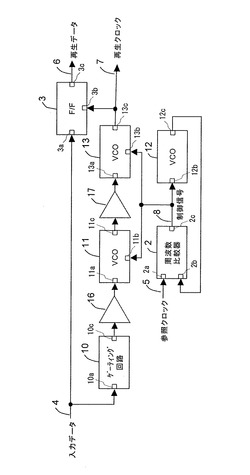

CDR回路

【課題】入力データに対する瞬時応答特性を備えかつジッタが大きな入力データが入力された時にも安定的な動作が可能でかつ出力ジッタを低減可能な小型低消費電力のCDR回路を提供する。

【解決手段】CDR回路は、入力データ4が遷移したときにパルスを出力するゲーティング回路10と、ゲーティング回路10の出力パルスのタイミングに合うように出力クロックの位相を調整するVCO11と、VCO11の出力クロックのタイミングに合うように再生クロック7の位相を調整するVCO13と、入力データ4のデータ識別を再生クロック7に基づいて行うフリップフロップ3と、ゲーティング回路10の出力端子とVCO11の入力端子との間に設けられたバッファ増幅器16と、VCO11の出力端子とVCO13の入力端子との間に設けられたバッファ増幅器17とを備える。

(もっと読む)

遅延時間差測定回路

【課題】本発明の一実施例では、2つの信号間の遅延時間差を信号のエッジに応じて正確に測定する遅延時間差測定回路を提供することを目的とする。

【解決手段】上記課題を解決するため、2本の信号線の伝播遅延時間差を測定する遅延時間差測定回路は、該2本の信号線に接続され、選択信号に応じて一方の信号線を伝播する信号を出力する選択回路と、該選択回路に接続され、該選択回路の出力信号を一定時間遅延させて該選択信号として出力する切替回路と、該選択回路の出力側と該2本の信号線の入力側を接続する帰還経路と、該帰還経路に接続され、該帰還経路を伝播する信号の自己発振周期に基づいて該2本の信号線を伝播する信号の遅延時間の差を算出する制御回路とを有する。

(もっと読む)

位相周波数比較器およびシリアル伝送装置

【課題】ループ帯域幅を安定させる位相周波数比較器を簡易な回路で提供する。

【解決手段】基準クロック102とフィードバッククロック103とを入力とし、周波数シンセサイザへのアップ信号と周波数シンセサイザへのダウン信号とを出力する位相周波数比較器において、第1位相周波数比較回路106と、第2位相比較回路107と、前記基準クロック102と前記フィードバッククロック103とを入力とし、前記第1位相周波数比較回路106の入力と前記第2位相比較回路107の入力とに、所定の相対的な遅延を与える遅延回路部108とを備え、周波数比較を前記第1位相周波数比較回路106で行い、位相比較を前記第1位相周波数比較回路106とラッチを制御した前記第2位相比較回路107とで行う位相周波数比較器。

(もっと読む)

位相検出回路および方法

【課題】 相当量の電力を消費し、かつジッタを生成する分周器回路を必要とせずに、高周波周期出力信号を生成する位相ロックループを提供すること。

【解決手段】 位相検出器回路は、第1および第2周期入力信号の位相を比較して、出力信号を生成する。位相検出器は、第1および第2周期入力信号の2つの異なる組み合わせを作り、第3および第4周期信号を生成する回路を備える。この回路は、第3周期信号を、第1相対位相シフトを付与する、第1周期信号および第2周期信号の第1の組み合わせに基づかせる。この回路は、第4周期信号を、第1周期信号および第2周期信号の第2の組み合わせに基づかせて、異なる相対位相シフトを提供する。位相検出器は、また、第3周期信号の電力の大きさを第4周期信号の電力の大きさと比較して、位相比較出力信号を生成する比較回路も備える。

(もっと読む)

基準周波数発生装置

【課題】比較器が出力する追従誤差に応じて適切な制御を行い、外乱の影響によっても基準周波数信号の精度が低下しない構成の基準周波数発生装置を提供する。

【解決手段】基準周波数発生装置は、電圧制御発振器と、位相比較器と、制御器と、ファジィ補償器と、を備える。電圧制御発振器は、基準周波数信号を出力する。位相比較器は、基準周波数信号を分周した信号と、リファレンス信号と、を比較して位相差を算出する。制御器は、位相差を考慮して制御電圧信号を電圧制御発振器に出力する。ファジィ補償器は、位相差が急激な変動をしているか否かを、ファジィ理論を用いて判定する。そして、ファジィ補償器は、位相差が急激な変動をしていると判定した場合は、当該位相差が基準周波数信号に影響を及ぼさないように補償値を決定する。

(もっと読む)

適応デジタル位相ロックループ

【課題】従来のデジタルPLLで問題であった出力クロックの位相ノイズ及びジッタ性能の低下に対応するアプローチを提供する。

【解決手段】幾つかの実施形態で、デジタルPLLは、例えば位相エラー等の1又はそれ以上の実時間性能パラメータに応答して有効なDPLL帯域幅を変更する動的制御可能なフィルタを有して開示される。高帯域幅が必要とされないとき、それは比較的低いレベルであるよう制御されてよく、それによって、出力クロックのジッタは低下する。他方で、高帯域幅が必要とされるとき、例えば、ループでの位相エラーが高いとき、フィルタは、基準クロックを追跡するためにループの応答性を高めるよう比較的高いループ帯域幅を提供するように制御され得る。

(もっと読む)

クロック位相同期回路

【課題】基準クロックに位相同期したクロックを出力するクロック位相同期回路に関し、長期間安定化及び入力擾乱影響を緩和する。

【解決手段】リファレンス入力a位相に同期した電圧制御発振器1の出力信号dを得る為のクロック位相同期回路であって、リファレンス入力aの周波数と電圧制御発振器1の出力信号dの周波数とを一致させて位相比較器3により所定のタイミング毎に位相比較した位相差検出信号bを入力し、それを所定期間順次記憶するメモリ等の記憶手段と、所定期間毎の位相差検出信号の差を位相変動量として求め、位相変動量が許容範囲内の場合は、その位相変動量に対応した電圧制御発振器1の制御電圧に変換し、許容範囲内でない場合は、前回の位相変動量に対応した制御電圧又は自走状態となる制御電圧として、電圧制御発振器1に制御電圧cを入力する演算処理手段とを備えている。

(もっと読む)

クロックデータリカバリ回路

【課題】ジッタに高速に追従可能なCDR回路を提供する。

【解決手段】フリップフロップFF1〜FF4はそれぞれ、入力データDINを対応するクロック信号CKのタイミングでラッチする。i(iは自然数)番目の第1論理ゲートG1iは、(2×i−1)番目のフリップフロップFFの出力と(2×i)番目のフリップフロップFFの出力とが不一致のときアサートされる内部アップ信号UPを生成する。j(jは自然数)番目の第2論理ゲートG2jは、(2×j)番目のフリップフロップFFの出力と(2×j+1)番目のフリップフロップFFの出力とが不一致のときアサートされる内部ダウン信号dnを生成する。第3論理ゲートG3は、複数の内部アップ信号up1〜up2にもとづきアップ信号UP_Aを生成する。第4論理ゲートG4は、複数の内部ダウン信号dn1、dn2にもとづきダウン信号DN_Aを生成する。

(もっと読む)

PLL回路

【課題】高速かつ確実に低雑音特性を得ることができるPLL回路を得ることを目的とする。

【解決手段】相互に異なる移相量PS14,PS24,PS34がそれぞれ設定されており、N分周された発振信号の位相を設定されている移相量だけ変える移相器4−1〜4−3と、移相量の差分の関係が移相器4−1〜4−3のそれぞれに設定されている移相量の差分の関係と一致する条件の下で、相互に異なる移相量PS15,PS25,PS35がそれぞれ設定されており、R分周された基準信号Refの位相を設定されている移相量だけ変える移相器5−1〜5−3とを設ける。

(もっと読む)

信号多重化回路

【課題】データ信号とクロック信号との位相関係を適応的に制御できる信号多重化回路を提供する。

【解決手段】信号多重化回路は、第1のクロック信号の第1の位相位置に同期したデータ遷移をする第1のデータ信号と第1のクロック信号の第1の位相位置から180度位相がずれた第2の位相位置に同期したデータ遷移をする第2のデータ信号とを受け取り、第2のクロック信号に応じて第1及び第2のデータ信号を順次選択して出力するセレクタ回路と、第1及び第2のデータ信号と第1及び第2のクロック信号とに基づいて、第2のクロック信号とデータ遷移との位相関係を示す位相制御信号を出力する位相検出器と、位相制御信号に応じて位相関係を制御する位相制御器とを含む

(もっと読む)

91 - 100 / 305

[ Back to top ]