国際特許分類[H03L7/089]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | 電子的振動またはパルス発生器の自動制御,起動,同期または安定化 (3,550) | 周波数または位相の自動制御;同期 (3,453) | 周波数または位相ロックループに加えられる基準信号を用いるもの (3,073) | 位相ロックループの細部 (2,372) | 出力信号のろ波又は増幅を含む主として周波数または位相検出装置に関するもの (896) | アップダウンパルスを出力する位相または周波数検出器 (20)

国際特許分類[H03L7/089]に分類される特許

1 - 10 / 20

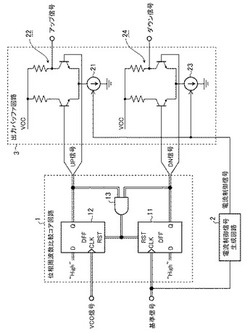

位相周波数比較回路

【課題】雑音特性及び高速動作を維持しながら、消費電力を削減することができる位相周波数比較回路を得ることを目的とする。

【解決手段】出力バッファ回路3が、電流制御信号生成回路2から電流制御信号が出力されている期間中、位相周波数比較コア回路1からUP信号が出力された場合、アップ信号を出力し、電流制御信号生成回路2から電流制御信号が出力されている期間中、位相周波数比較コア回路1からDN信号が出力された場合、ダウン信号を出力する。

(もっと読む)

位相周波数比較器およびシリアル伝送装置

【課題】ループ帯域幅を安定させる位相周波数比較器を簡易な回路で提供する。

【解決手段】基準クロック102とフィードバッククロック103とを入力とし、周波数シンセサイザへのアップ信号と周波数シンセサイザへのダウン信号とを出力する位相周波数比較器において、第1位相周波数比較回路106と、第2位相比較回路107と、前記基準クロック102と前記フィードバッククロック103とを入力とし、前記第1位相周波数比較回路106の入力と前記第2位相比較回路107の入力とに、所定の相対的な遅延を与える遅延回路部108とを備え、周波数比較を前記第1位相周波数比較回路106で行い、位相比較を前記第1位相周波数比較回路106とラッチを制御した前記第2位相比較回路107とで行う位相周波数比較器。

(もっと読む)

位相同期回路

【課題】デジタル型の位相比較器だけで構成しつつ、不感帯の影響を排除して出力信号の位相雑音を低減する。

【解決手段】制御電圧Vcに応じた周波数の出力信号Soを出力する電圧制御発振器4と、位相比較対象信号Sdおよび基準信号Srを入力して、位相比較対象信号Sdの位相が基準信号Srの位相に対して遅れているときには両信号Sd,Srの位相差に応じたパルス幅の第1パルス信号S1を出力し、位相比較対象信号Sdの位相が基準信号Srの位相に対して進んでいるときには両信号Sd,Srの位相差に応じたパルス幅の第2パルス信号S2を出力する位相比較器2と、両パルス信号S1,S2を入力すると共に両パルス信号S1,S2の差分を積分して制御電圧Vcを出力するループフィルタ3とを備え、両パルス信号S1,S2のうちの一方のパルス信号の信号電圧を他方のパルス信号の信号電圧と異なる電圧に規定する電圧規定部6を備えている。

(もっと読む)

発振回路、DC−DCコンバータ及び半導体装置

【課題】CPUなどの特別な制御回路が不要で、しかも無線送受信回路で用いている周波数に関わりなく、スイッチングノイズの影響を無視できるレベルまで軽減することが可能な発振周波数制御回路を提供する。

【解決手段】周波数が下限周波数と上限周波数の間を連続的に変化しながら往復する発振回路において、アップダウン制御回路20は、第1の検出回路30がクロック信号のハイレベル又はローレベルの時間が第1の遅延時間以下になったことを検出した場合は、ダウン信号を可変周波数発振回路に出力し、第2の検出回路40がクロック信号のハイレベル又はローレベルの時間が第2の遅延時間以上になったことを検出した場合は、アップ信号を可変周波数発振回路10に出力する。

(もっと読む)

位相同期ループ形周波数シンセサイザ

【課題】サイクルスリップの発生を防止して、短時間で周波数の切り換えを行うことができる位相同期ループ形周波数シンセサイザを得ることを目的とする。

【解決手段】 VCO4により発振される高周波信号Doの周波数が切り換えられる場合、位相比較器2が第1の位相比較信号Dnuと第2の位相比較信号Dndの差分を一定に保持するように構成する。これにより、サイクルスリップの発生を防止して、短時間で周波数の切り換えを行うことができる効果を奏する。

(もっと読む)

位相比較器、位相同期回路及び位相比較制御方法

【課題】入力断検出部を位相比較器に内蔵することで位相比較器を実装するPLL回路の小型化を図る。

【解決手段】参照信号を入力すると共に、参照信号に基づく被参照信号を帰還入力し、これら入力した参照信号及び被参照信号の立ち上がりエッジを検出し、参照信号の立ち上がりエッジ及び被参照信号の立ち上がりエッジ間の位相差を検出する位相差検出部21と、位相差検出部21にて検出した位相差に基づき、位相差を小さくすべく、定電流出力動作を実行する定電流出力部24と、被参照信号のエッジを検出した後、参照信号のエッジを検出する前に、被参照信号のエッジを再度検出した場合、参照信号の入力断として検出する入力断検出部23とを有している。

(もっと読む)

位相検出装置、位相比較装置およびクロック同期装置

【課題】クロック同期システムに用いる位相比較器として、次段のカウンタに影響を与えることなく、クロックの同期がとれた際に確実にロックをかけること。

【解決手段】本発明は、基準クロックの位相に対する比較クロックの位相のずれを検出する第1の位相比較部K1aと、基準クロックおよび比較クロックのいずれか一方について所定時間遅延または進んだ状態での両クロックの位相のずれを検出する第2の位相比較部K1bと、第1の位相比較部K1aの出力と第2の位相比較部K1bの出力との論理積を位相ずれの検出結果として出力する論理積部AND1とを備える

(もっと読む)

デジタル位相ロックループを実施するためのシステム及び方法

【課題】デジタル位相ロックループを実施するシステム及び方法を提供する。

【解決手段】デジタル位相ロックループを実施する装置は、VCO制御電圧に応答して1次クロック信号を発生する電圧制御式発振器を含む。検出手段は、カウントアップ信号及びカウントダウン信号を含むカウンタ制御信号を発生し、1次クロック信号と基準信号の現在の関係を示す。アップ/ダウンカウンタは、次に対応するカウンタ制御信号に応答してカウンタ値を増分又は減分する。カウンタ値は、次に電圧制御式発振器により発生された1次クロック信号の周波数を調節するためにデジタル/アナログ変換器によってVCO制御電圧に変換される。代替実施形態では、上述のアップ/ダウンカウンタを利用して、デジタル/アナログ変換器でVCO制御電圧を発生する以外の適切な技術の利用により、カウンタ値に比例して電圧制御式発振器の周波数を調節することができる。

(もっと読む)

CP出力型位相比較器の制御方法及びCP出力型位相比較器

【課題】CP出力型位相比較器に関し、REFクロック歯抜け後の位相スリップを防止することができる定電流CP出力型位相比較器を提供。

【解決手段】PLL回路に用いる位相比較器において、位相比較器の状態遷移モードをハイインピーダンス状態と、電流吐き出し状態と、電流吸い込み状態の3つの状態を設け、電流吸い込み状態からハイインピーダンスに移行する条件として、REFクロックの立ち上がりに加え、フィードバッククロックの立下がりにおいてもハイインピーダンス状態に遷移するようにして、クロック歯抜け後の出力位相スリップを防止するように構成する。

(もっと読む)

位相同期ループのための線形位相周波数検出器およびチャージポンプ

位相同期ループ(PLL)における位相周波数検出器およびチャージポンプの線形動作を達成するための技術が説明される。位相周波数検出器は、基準信号とクロック信号とを受け取り、基準信号とクロック信号とに基づいて第1および第2の信号を生成し、第1の信号のみに基づいて第1および第2の信号をリセットする。第1および第2の信号は、それぞれ、upおよびdownの信号であってもよいし、それぞれ、downおよびupの信号であってもよい。位相周波数検出器は、予め定められた量の分、第1の信号を遅らせ、遅れた第1の信号と第2の信号とに基づいて、リセット信号を生成し、リセット信号を用いて第1および第2の信号をリセットすることができる。チャージポンプは、第1および第2の信号を受け取り、基準信号とクロック信号との間の位相誤差を示す出力信号を生成する。  (もっと読む)

(もっと読む)

1 - 10 / 20

[ Back to top ]