国際特許分類[H03L7/091]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | 電子的振動またはパルス発生器の自動制御,起動,同期または安定化 (3,550) | 周波数または位相の自動制御;同期 (3,453) | 周波数または位相ロックループに加えられる基準信号を用いるもの (3,073) | 位相ロックループの細部 (2,372) | 出力信号のろ波又は増幅を含む主として周波数または位相検出装置に関するもの (896) | サンプリング装置を用いる位相または周波数検出器 (49)

国際特許分類[H03L7/091]に分類される特許

1 - 10 / 49

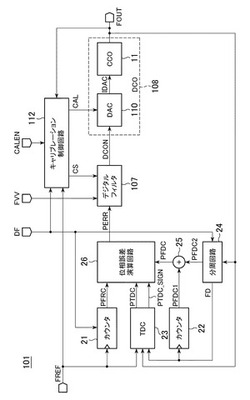

デジタルPLL回路、半導体集積回路装置

【課題】デジタルPLL回路の追従可能な周波数レンジを拡大する。

【解決手段】第1カウンタ(21)は、第1クロック信号をカウントして第1カウント値を出力し、第2カウンタ(22)は、第2クロック信号を分周して生成される第3クロック信号をカウントして第2カウント値を出力する。位相検出器(23)は、第1クロック信号と、第3クロック信号との位相差をデジタル値で示す出力値を出力する。位相誤差演算回路(26)は、第1カウント値と、第2カウンタ値と、出力値とに基づいて、位相誤差を演算して出力する。デジタルフィルタ回路(107)は、位相誤差を平滑化して発振周波数を示すコードを出力する。デジタル制御発振器(108)は、コードに応答して第2クロック信号を出力する。キャリブレーション制御回路(112)は、分周比と、第2クロック信号と第1クロック信号との比較結果とに基づいてデジタル制御発振器の発振周波数を調整する。

(もっと読む)

周波数シンセサイザ

【課題】ディジタル処理を用いたPLLにより周波数シンセサイザを構成するにあたって、A/D変換部を不要とすること。

【解決手段】設定周波数に応じたディジタル値を積分することにより、位相信号となる鋸波を生成する。一方電圧制御発振器から出力される周波数信号を分周回路を介してエッジ検出部に入力し、前記周波数信号の立ち上がりまたは立ち下がりのエッジを検出して当該周波数信号の周波数に応じた矩形波信号を生成する。そしてラッチ回路にて、前記矩形波信号により鋸波の値をラッチし、この値をループフィルタにて積分し、電圧制御発振器の制御電圧とする。

(もっと読む)

周波数推定方法、広帯域周波数弁別器及び無線位置測定用受信機

【課題】 サンプリング周波数の2倍の周波数における回転因子の集合に対応する、DFT演算子と1/2DFT演算子の組み合わせにもとづく周波数弁別器である。

【解決手段】 周波数弁別器は、ゼロ又は不連続点を持たないように選定される。そのため、この発明の弁別器は、拡張された動作範囲において、より安定的かつ良好に動作する。この発明の弁別器は、GPS受信機に適用された場合、初めに大きな誤差が有っても、より確実にキャリヤ周波数にロックすることが可能であるとともに、誤ってロックする問題を防止するものである。

(もっと読む)

デジタル位相同期回路および物理量検出センサ

【課題】簡単な構成で位相同期を行うことができるデジタル位相同期回路および物理量検出センサを提供する。

【解決手段】位相比較部は、サンプリング値の符号情報を示す符号クロックCLK1と分周器の分周クロックCLK2との位相差を算出する。このとき、位相比較部は、符号クロックCLK1による立上りタイミングからダウンカウントし、分周器の分周クロックCLK2による立下りタイミングにてアップカウントし、符号クロックCLK1による立上りタイミングにて得られたカウント値を位相比較カウント値として出力する。そして、加算器が、位相比較カウント値に位相補正部の位相補正値を加算してループフィルタに出力する。

(もっと読む)

位相周波数比較回路及びPLL回路

【課題】入力クロックが停止しても出力クロックの周波数を保持するPLLを用いて、ロジック回路を駆動する方法を提供する。

【解決手段】位相周波数比較回路をPFD主要部と基準クロック停止検出部202Bの二つのモジュールから構成する。基準クロック停止検出部202BはPFD主要部のRS−FFのデータ端子に基準データ信号pfd_in_enを出力する。この基準データ信号pfd_in_enは、基準クロック停止検出部202B内のフリップフロップ202B−1に由来して生成される。このフリップフロップ202B−1は位相比較動作の終了を表すオーバラップ信号overlapをタイミングとし、基準クロックref_clkによってリセットされる。基準クロックref_clkが停止すると、基準データ信号pfd_in_enは「L」のままとなり、結果PFD主要部の動作が停止する。

(もっと読む)

クロック発振回路及び半導体装置

【課題】起動時にTDCにキャリブレーション処理を加えることで、時間分解能のばらつきが発生することを防ぎ、合わせて、遅延用の素子の冗長度を減らすことで回路規模の増大を防ぐ手段を提供する。

【解決手段】電源投入時等に多相発振器型TDCであるPDC_c及びバーニア型TDCであるPDC_fのキャリブレーションを実行する。キャリブレーション時にはPDC_fに入力するタイミング入力を参照クロックCLK_REFからDCCOの出力信号のうち一つを選択する。またデータは、先のDCCOの出力信号に隣接し、位相が進んだ出力信号とし、その間の遅延を導出する。これを全出力信号繰り返すことで、DCCOの出力信号1周期を導出する。

(もっと読む)

位相比較器およびクロックデータリカバリ回路

【課題】充放電流を切り替えるスイッチを確実に動作させ、高速化に対応できチャージポンプ回路の機能を保持できる位相比較器およびクロックデータリカバリ回路を提供する。

【解決手段】入力データと第1のラッチ111のラッチデータの論理不一致を検出する第1の検出回路と、第1のラッチのラッチデータと第2のラッチ112のラッチデータの論理不一致を検出する第2の検出回路と、第1の検出回路および第2の検出回路の検出結果に応じて、電流を充電または放電を切り替えるための切替スイッチ機能を含むチャージポンプ回路と、を有し、第1の検出回路、第2の検出回路、およびチャージポンプ回路は、第1および第2の検出回路の論理不一致判定部とチャージポンプ回路の充放電流を切り替える切替スイッチとが複合化された検出回路複合型チャージポンプ回路120として形成されている。

(もっと読む)

位相同期回路および無線受信装置

【課題】サブサンプリングPLLの利点を保持したまま、フラクショナル分周を実現する。

【解決手段】電圧制御発振器は、制御電圧に応じて周波数が制御される第1信号、および前記第1信号と逆相の第2信号を生成する。サブサンプリング位相比較器は、基準信号の周期毎に、前記第1信号および第2信号の電圧を標本化して、第1標本化電圧および第2標本化電圧を生成する。電流生成回路は、供給電圧に応じて第1電流信号を生成する第1のチャージポンプと、供給電圧に応じて前記第1電流信号と反対符号の第2電流信号を生成する第2のチャージポンプとを有する。セレクト制御手段は、前記第1および第2標本化電圧を前記第2および第1チャージポンプにまたはこれと反対に供給する第1、第2供給モードを選択的に実行する。ループフィルタは、前記第1、第2の電流信号の合成電流信号を平滑化して、前記電圧制御発振器に与える前記制御電圧を生成する。

(もっと読む)

半導体集積回路および無線通信装置

【課題】小規模かつ低消費電力で発振信号を生成可能な半導体集積回路およびこれを用いた無線通信装置を提供する。

【解決手段】半導体集積回路は、デジタル制御発振器と、カウンタと、時間デジタル変換器と、加算器と、制御信号生成部と、を備える。時間デジタル変換器は、発振信号と参照信号との位相差に対応する第3のデジタル信号を生成する。前記時間デジタル変換器は、分周器と、複数のインピーダンス素子と、位相差検出部と、を有する。分周器は、前記発振信号を分周して複数の分周信号を生成する。複数のインピーダンス素子は、前記複数の分周信号を分圧して、前記発振信号を遅延させた複数の遅延信号を生成する。位相差検出部は、前記参照信号と、前記複数の遅延信号のそれぞれと、を比較することにより、前記参照信号と前記発振信号との位相差に対応する前記第3のデジタル信号を出力する。

(もっと読む)

位相同期回路

【課題】位相同期回路においてロックアップを高速化する。

【解決手段】位相同期回路100は、基準信号の周波数にXを乗じて得られる出力周波数を有し、基準信号源180と、電圧制御発振器110と、位相比較器120と、第1チャージポンプ130と、ループフィルタ150と、カウンタ161と、第2チャージポンプ170と、制御回路164とを備える。電圧制御発振器110は、第1信号、および逆相の第2信号を生成する。スイッチ140は、第1チャージポンプ130で生成された電流信号をループフィルタ150に供給する。カウンタ161は、基準信号の1周期期間に含まれる、第2信号のサイクル数をカウントする。第2チャージポンプ170は、互いに反対符号の第1電流信号と第2電流信号をループフィルタ150に供給可能である。制御回路164は、サイクル数とXの値との比較に基づき、スイッチ140および第2チャージポンプ170を制御する。

(もっと読む)

1 - 10 / 49

[ Back to top ]