国際特許分類[H03L7/199]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | 電子的振動またはパルス発生器の自動制御,起動,同期または安定化 (3,550) | 周波数または位相の自動制御;同期 (3,453) | 周波数または位相ロックループに加えられる基準信号を用いるもの (3,073) | 間接的な周波数の合成,すなわち周波数または位相ロックループを用いる予じめ決められた多数の周波数の内の所望の一つを発生するもの (528) | ループの中に分周器または計数器を用いるもの (427) | ループをロックするために時間差を用いるもの,適時変化可能な数値間を計数する計数器,または適時変化可能な係数によって分周する分周器,例.非整数の周波数分周を得るもの (112) | 分周器または計数器のリセットを用いるもの,例.初期同期を確実にするためのもの (18)

国際特許分類[H03L7/199]に分類される特許

1 - 10 / 18

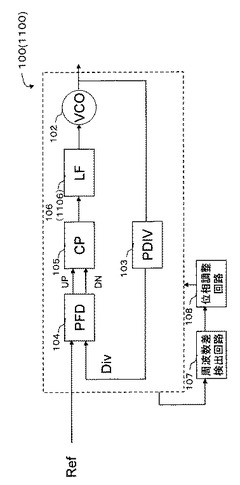

位相同期回路及び無線機

【課題】位相同期回路のセトリング時間を短縮する。

【解決手段】位相同期回路は、制御信号に応じた発振周波数を含む発振信号を生成する電圧制御発振器と、前記発振信号を分周して分周信号を生成する分周器と、前記分周信号と基準信号との位相を比較し、比較信号を生成する位相比較器と、前記比較信号に応じた電流を出力するチャージポンプと、前記電流をフィルタリングし、前記制御信号を生成するフィルタと、前記分周信号の周波数の定数倍の値と前記基準信号の周波数の定数倍の値との差分が極小となった場合に検出信号を生成する周波数差検出回路と、前記検出信号が生成されると、前記分周信号と前記基準信号との位相を同期させる位相調整回路とを備える。

(もっと読む)

分周回路及び集積回路

【課題】分周器の発振を防止する分周回路を提供する。

【解決手段】クロック信号Vcを所定の分周比にて分周する分周器20を備え、分周器の発振を防止する分周回路1であって、クロック信号のピーク電圧Vcpを検出してピーク値を保持するピーク検出器30と、分周器が正常動作するために必要なクロック信号の振幅vpに対応した参照電圧Vrefを出力する参照電圧発生器40と、ピーク検出器により検出されたピーク値と参照電圧とを比較する比較器50と、を備え、分周器に分周開始を指示する制御信号を入力する制御端子を備え、制御端子に比較器の出力信号Veを接続し、ピーク値が参照電圧を超えたときに、比較器は、分周器の制御端子に分周開始を指示する制御信号を出力する

(もっと読む)

タイミング回復のためのサイクルスリップ検出

【課題】タイミング回復のためのサイクルスリップ検出の提供。

【解決手段】タイミング回復のために制御ループ中のループフィルタLFの出力信号を使用するステップと、前記フィルタ処理後のタイミング誤差信号から平均タイミング誤差値を生成するステップと、第1の閾値を超えるサンプルの隣接するブロックの平均タイミング誤差値の変化を累積するステップとを含む。第2の閾値を超える隣接するブロックの累積した平均タイミング誤差変化がサイクルスリップとして表明され、サイクルスリップの数が許容閾値である第3の閾値によって決定される。さらに、先入れ先出しメモリFIFOがサンプル挿入または削除のために設けられ、それは、サンプル挿入またはサンプル削除が向上した信頼性を伴ってサンプル領域で行われ、サイクルスリップ検出の改善された方法が雑音および不適切に選ばれたタイミングループパラメータに対する頑健性の増強のために推奨される。

(もっと読む)

PLL位相合わせ回路

【課題】PLL回路のリファレンスクロックが停止された後に再開された場合、再開後のリファレンスクロックとフィードバッククロックとの位相合わせを短時間で行い、再ロックさせることができるPLL位相合わせ回路を提供する。

【解決手段】PLL位相合わせ回路は、PLL回路と、フィードバッククロックを分周する第1の分周回路と、PLL回路の出力クロックを分周する第2の分周回路と、リファレンスクロックの動作状態を監視するクロックモニタ回路とを備える。第1の分周回路の分周数は、第2の分周回路の分周数と等しく、クロックモニタ回路が、リファレンスクロックが停止されたことを検出すると、第1の分周回路がリセットされてフィードバッククロックが停止され、リファレンスクロックが再開されたことを検出すると、第1の分周回路のリセットが解除されてフィードバッククロックが再開される。

(もっと読む)

PLL回路

【課題】同期信号の位相が大きく変化する場合にも、短時間で位相を同期させる。

【解決手段】本PLL回路における位相比較器10は、映像信号に含まれる同期信号SYNと位相比較信号BLKとの位相誤差を示す比較出力信号PDPを出力し、VCO30は、比較出力信号PDPを積分するLPF20から与えられる直流電圧に応じた周波数のクロック信号CKを出力する。カウンタ40は、クロック信号CKを分周した位相比較信号BLKを出力する。ロック確認回路50は、位相比較信号BLKと同期信号SYNとの位相が同期すべきロック状態であるか否かを確認し、ロック状態でない場合にはリセット信号RSTを出力し、カウンタ40をリセットすることにより強制的にロック状態にすることができる。よって、短時間で位相を同期させることができる。

(もっと読む)

位相雑音除去装置及び方法、受信装置及び方法、並びにプログラム

【課題】使用予定のダウンコンバータが複数ある場合でも、位相雑音を適切に除去する。

【解決手段】位相雑音除去回路31では、位相雑音量検出器41は、ダウンコンバータ22から供給されるIF信号から位相雑音量を検出し、ゲイン決定回路42は、位相雑音量に応じた、IF信号に対する位相同期で用いられるループゲインを示す対照表を複数有し、その複数の対照表のうちの1つに基づいて、検出される位相雑音量に応じたループゲインを決定し、位相同期回路43は、決定されたループゲインに基づいて、IF信号の位相雑音を除去する。本発明は、例えば、TV受像機等に適用できる。

(もっと読む)

位相同期ループ周波数合成に於ける低雑音化の方法

【課題】位相ジッタの少ない位相同期ループ回路を実現する。

【解決手段】第一および第二レジスタへ接続された第一および第二計数手段10,14を含む位相同期ループ回路が開示される。第一レジスタ18は数Mを第二レジスタ20は数Nを記憶する。第一計数手段は基準信号FrefのMサイクルに応答してF1出力信号を出力し、第二計数手段は出力信号FoutのNサイクルに応答してF2出力信号を出力する。F1,F2,Fref,Fout 信号は、位相検出器30へ接続され、FrefとFoutの位相が比較される。位相検出回路の出力信号は位相検出回路出力信号に比例したFout信号を発生する電圧制御発振器12に接続される。Fout信号は位相同期ループ回路が整定するまで第二レジスタへフィードバックされる。

(もっと読む)

同期損失防止方法及び同期損失防止装置

【課題】CDR回路側の原因による接続ノード間の同期化の非成立を抑制し、接続失敗を抑制することができる同期損失防止方法及び同期損失防止装置を提供する。

【解決手段】受信データから同期化クロックを生成するCDR(Clock Data Recovery )回路と、受信データの受信開始から同期化検出時間Nを経過しても同期化クロックに基づく接続ノード間の同期化が非成立のときに、接続失敗処理を行う接続失敗処理段階(S15)と、受信データの受信開始から同期化リトライ判定時間(N/2)を経過しても同期化クロックに基づく接続ノード間の同期化が非成立のときに、CDR回路の動作を補正処理する補正処理段階(S13)とを備える。

(もっと読む)

周波数切替え方法、周波数切替え装置および撮像装置

【課題】 回路規模が大きくなるのを抑えることができ、動作中に周波数を切り替えたときに異常動作が起きるのを防ぐことができる周波数切替え方法を提供する。

【解決手段】 出力信号の周波数を目標周波数に切り替えるときに、位相周波数比較器10とチャージポンプ回路11と逓倍設定回路14をリセット状態にし(S2)、逓倍数を目標周波数に対応した逓倍数C1に変更し(S4)、分周数を目標周波数に対応した分周数より大きい仮分周数2Nに変更する(S5)。その後、位相周波数比較器10とチャージポンプ回路11と逓倍設定回路14のリセット状態を解除して(S6)、分周数を目標周波数に対応した分周数Nに変更する(S8)。

(もっと読む)

クロック位相シフト装置

【課題】PLL回路を使用してクロックの位相をずらすクロック位相シフト装置において、PLLロック外れを発生しにくくする。

【解決手段】水晶発振器100の出力クロックC100を入力する第1段のPLL回路201、およびこの第1段のPLL回路の出力クロックC201を入力する第2段のPLL回路202を備え、前記第2段のPLL回路の出力クロックC202が前記第1段のPLL回路に前記水晶発振器の出力クロックと比較する入力クロックとして入力され、前記第2段のPLL回路の出力クロックC202が外部への出力クロックとして取り出されるクロック位相シフト装置。

(もっと読む)

1 - 10 / 18

[ Back to top ]