国際特許分類[H03M1/66]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | 符号化,復号化または符号変換一般 (10,763) | アナログ/デジタル変換;デジタル/アナログ変換 (2,647) | デジタル/アナログ変換器 (612)

国際特許分類[H03M1/66]の下位に属する分類

異なる感度の変換を伴うもの,すなわち一方の変換が上位のデジタルビットに関連し,他方の変換が下位のデジタルビットに関連するもの (84)

変換器範囲を修正するための自動制御 (10)

直列接続段による逐次変換 (2)

同時変換 (311)

時間間隔への中間変換を行うもの (43)

パルス周波数への中間変換を行うもの (4)

国際特許分類[H03M1/66]に分類される特許

1 - 10 / 158

DACの直線歪補正回路

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

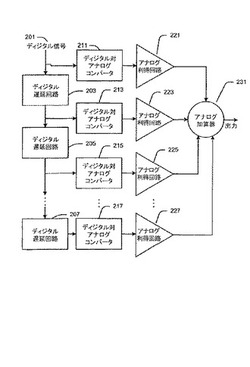

結合されたディジタル対アナログコンバータおよび信号フィルタ

【課題】多様な応用、および超広帯域の応用において使用されることができるアナログローパスフィルタを提供する。

【解決手段】ディジタル信号201を処理する電子回路は、各々がディジタル信号の遅延されたレプリカを生成するように構成されている複数のディジタル遅延回路203,205,207と、各々がディジタル信号または遅延回路の1つからの遅延されたレプリカをアナログ信号へ変換するように構成されている複数のディジタル対アナログコンバータ211,213,215,217と、各々がディジタル対アナログコンバータからのアナログ信号を利得係数によって調節するように構成されていて、かつ各々が出力をもつ複数のアナログ利得回路221,223,225,227と、アナログ利得回路の出力を加算するように構成されているアナログ加算器231とを含む。

(もっと読む)

DA変換回路

【課題】精度の高いDA変換結果を出力する。

【解決手段】入力される2値の論理値に応じて充電され、充電電荷が再分配されることでDA変換結果を第1および第2の容量素子C1、C21(C22)における電圧として得る電荷再分配型のDA変換回路であって、第2の容量素子C21(C22)に電荷として保持されたDA変換結果を出力する増幅器AMPと、第1の容量素子C1の一端と増幅器AMPの入力端とを短絡可能とするスイッチ素子φ4と、第2の容量素子C21(C22)に保持されたDA変換結果を増幅器AMPの入力端に与える前に、スイッチ素子φ4を一時的に短絡するように各部を制御するタイミング信号群を生成するタイミング制御回路CNTと、を備える。

(もっと読む)

半導体集積回路装置

【課題】レベル変換回路のレイアウト面積の縮小を図る。

【解決手段】半導体集積回路装置(10)は、レベル変換回路(14)と、D/A変換回路(12)とを備える。このとき、パラレル形式のデジタル信号をシリアル形式に変換して上記レベル変換回路に供給するためのパラレル・シリアル変換回路(15)と、上記レベル変換回路の出力をパラレル形式のデジタル信号に変換して上記D/A変換回路に供給するためのシリアル・パラレル変換回路(13)とを設ける。上記レベル変換回路は、シリアル形式のデジタル信号に対応するレベル変換機能を備えていれば良く、パラレル形式のデジタル信号に対応させる場合に比べて、レベル変換回路のレイアウト面積を縮小することができる。

(もっと読む)

半導体装置、その検査方法および送信回路

【課題】光結合部の伝送マージンを確保して復調誤りを抑制し、高精度の信号伝送を可能とする半導体装置、その検査方法および送信回路を提供する。

【解決手段】半導体装置100は、アナログディジタル変換部3と、ディジタル信号に応じたパルスパターンである伝送信号を出力するパルス幅変調部5と、固定パルスである参照信号を生成する参照信号生成部7と、を備える。そして、前記伝送信号および前記参照信号のいずれかを選択する第1の制御部13と、前記伝送信号または前記参照信号に基づく駆動電流を出力する発光素子駆動部9と、前記伝送信号または前記参照信号基づく光信号を放出する発光素子15と、を備える。さらに、前記光信号を電圧信号に変換する光受信部21と、前記電圧信号を前記伝送信号または前記参照信号に基づくディジタル信号に復調する復調部25と、を備える。

(もっと読む)

オーディオ信号伝送装置

【課題】 I2S信号をパルストランスを使用して絶縁すること。

【解決手段】 オーディオ信号が無音(振幅値が0V)である場合に、DATA信号のLチャンネルのデータDLiは、「00000000・・・」と「0」が続き、直流信号となってしまう。しかし、変調部2で生成される第2のLチャンネルオーディオ信号は、LRCK信号のハイレベルの期間においては「00000・・」であり、LRCK信号のローレベルの期間においては「11111・・」であるので、その結果、第2のLチャンネルオーディオ信号は交流信号と見なすことが可能となる。従って、第2のLチャンネルオーディオ信号を、パルストランス3を使用して絶縁することができる。

(もっと読む)

DA変換装置

【課題】より高精度でビット拡張ができるDA変換装置を提供する。

【解決手段】DA変換装置12は、2m個のnビットのDAコンバータ14と、このDAコンバータ14からの出力を加算する演算器16と、前記DAコンバータに入力するnビットの中間データを生成するデータプロセッサ12と、を備えている。データプロセッサは、各DAコンバータ14の中間データとして、入力データの上位nビットデータに、補正値を付加したデータを生成する。補正値は、その総和が、入力データの下位mビットデータが示す値に等しくなるように設定される。

(もっと読む)

液晶駆動用のソースドライバのオフセット低減出力回路

【課題】 出力アンプのオフセット電圧を適切に低減して表示品質の悪化を防止することができる液晶駆動用のソースドライバのオフセット低減出力回路を提供する。

【解決手段】 基準電圧がオペアンプの非反転入力端に印加されたオペアンプと、少なくとも通常出力動作時にオペアンプの反転入力端に接続される第1の接続点に各々の一端が接続された第1の入力コンデンサ及び第1の出力コンデンサと、リセット動作時に第1の入力コンデンサ及び第1の出力コンデンサ各々の両端を短絡してその両端に基準電圧を印加し、リセット動作後の通常出力動作時に第1の入力コンデンサの他端に階調電圧を印加しかつ第1の出力コンデンサの他端をオペアンプの出力端に接続する第1のスイッチ素子回路と、を備え、第1のスイッチ素子回路は、第1の接続点とオペアンプの出力端との間に接続され、リセット動作時にオンとなり、通常出力動作時にオフとなる直列接続の第1及び第2のスイッチ素子を有し、通常出力動作時には第1及び第2のスイッチ素子の直列接続点に基準電圧を印加する。

(もっと読む)

パラレルデータ出力制御回路及び半導体装置

【課題】常に信頼性の高いパラレルデータ出力制御が行えるをパラレルデータ出力制御回路を得る。

【解決手段】CPU12はバッファ13からのリクエストRQに応答して内蔵RAM11よりデジタルデータをバッファ13に出力する。バッファ13は複数段構成のFIFOを有し、FIFOの各段は1単位(10ビット)のデジタルデータを格納可能であり、バッファ13全体としてFIFOの構成段数単位分のデジタルデータを格納することができる。レジスタ14は出力制御クロックCK15に同期して、バッファ13内部に格納したデジタルデータを1単位ごとに取り込む。レジスタ14に格納されたデジタルデータがD/A変換用データDataとしてパラレルDAC2に出力される。WR信号出力タイマ17は出力制御クロックCK15に同期して“L”の1ショットパルスを有する書き込み制御信号WRを生成する。

(もっと読む)

DA変換装置

【課題】複数のDA変換器のそれぞれの積分非直線性誤差の影響を抑えて高速動作できるとともに、SFDRを拡大させることができるDA変換装置を提供する。

【解決手段】デジタル信号源2で生成されたデジタルデータ及びクロック信号がDA変換装置1に入力される。DA変換装置1は、データ選択用スイッチ11と、複数のDA変換器としての第1のDA変換器12及び第2のDA変換器13と、切替手段としてのアナログ信号切替用スイッチ14と、分周器15とを有している。各DA変換器12,13の積分非直線性誤差特性の非線形歪特性は、互いに逆の特性である。第1,2のDA変換器12,13の積分非直線性誤差特性は、第1,2のDA変換器12,13の両方の積分非直線性誤差を平均すると、ゼロに近づくような特性である。

(もっと読む)

1 - 10 / 158

[ Back to top ]