国際特許分類[H04L25/38]の内容

電気 (1,674,590) | 電気通信技術 (544,871) | デジタル情報の伝送,例.電信通信 (61,356) | ベースバンド方式 (1,966) | 同期またはスタート・ストップ方式,例.ボード符号 (545)

国際特許分類[H04L25/38]の下位に属する分類

送信回路;受信回路 (479)

中継器回路;リレー回路 (15)

国際特許分類[H04L25/38]に分類される特許

11 - 20 / 51

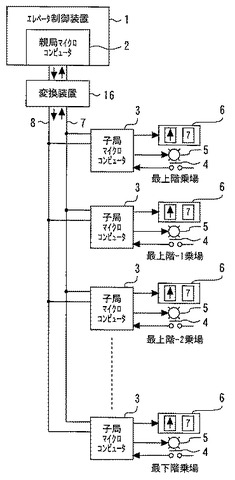

エレベータの信号伝送装置

【課題】直列伝送信号が時間軸に対して歪んだとしても、正しくデータを受信することができるレベータの信号伝送装置を提供する。

【解決手段】直列伝送信号の最初のビット以外の特定のビットが直前のビットと異なるレベルに緩やかに移行する場合に、親局によるサンプリング位置での特定のビットの値が異なるレベルと認識される値となるように、残りのビットの時間幅を維持しつつ、最初のビットの時間幅を狭くして、複数のビットを連続的に並べて親局へ送信するようにした。

(もっと読む)

シリアルコントローラ及び双方向シリアルコントローラ

【課題】シリアルコントローラを提供する。

【解決手段】本シリアルコントローラは外部クロックと入力データとを受信し、反転クロックと出力データとを出力するよう適合し、インバータと、シリアル位置検出器と、同期クロック生成器と、シリアルレジスタと、半サイクル遅延ユニットとを備える。このシリアルコントローラにより、クロック列が反転された場合、データ信号と駆動クロックが同期しないという問題を回避できる。また、双方向シリアルコントローラは識別ユニットと、データ方向付けユニットとを更に備え、このシリアルコントローラは、エラー検出のための参照データとするために現在の状態を中央制御ユニットに送ることが出来る。

(もっと読む)

半導体装置

【課題】動作用クロックの周波数にかかわらず、所要のビットレートに近いビットレートでシリアル通信を行えるようにする。

【解決手段】半導体装置は、所定の動作用クロックに従って動作するシリアルコミュニケーションインタフェース(109)を含む。上記シリアルコミュニケーションインタフェースに、上記動作用クロックをカウントし、それに基づいて、上記単位転送時間を規定するための基本クロックを生成するボーレートジェネレータ(202)と、生成された基本クロックに従って送受信制御を行うための送受信コントローラ(201)とを設ける。さらに上記シリアルコミュニケーションインタフェースに、上記動作用クロックの上記ボーレートジェネレータへの供給を部分的にマスクすることで所望のビットレートを実現可能なビットレートモジュレータ(203)を設けることで、所要のビットレートに近いビットレートでのシリアル通信を実現する。

(もっと読む)

信号処理装置、及び信号伝送方法

【課題】バスシステムにおいて伝送遅延による受信不良を回避することが可能な信号処理装置を提供すること。

【解決手段】第1のバスに接続されたマスター機器から供給されるクロックと、当該クロックに同期して前記マスター機器から送信されるデータとを受信するマスター側受信部と、前記第1のバスとは異なる第2のバスに接続されたスレーブ機器に対し、前記マスター側受信部により受信されたクロック及びデータを送信するスレーブ側送信部と、前記スレーブ側送信部により送信されたクロックに同期して前記スレーブ機器から送信されたデータを受信してバッファに格納するスレーブ側受信部と、前記マスター側受信部によりクロック及びデータが受信されるタイミングで、当該クロックに同期して前記バッファに格納されているデータを前記マスター機器に送信するマスター側送信部と、を備える、信号処理装置が提供される。

(もっと読む)

ボーレートエラー検出回路、ボーレートエラー検出方法

【課題】シリアル通信におけるシンクフィールドの異常波形を検出すること。

【解決手段】ボーレートエラー検出回路は、エッジディテクタと、スタートビットサンプリング回路と、異常波形検出回路とを備える。エッジディテクタは、シリアル通信のボーレートを調整するためのシンクフィールドを受け取り、シンクフィールド中のエッジに応答してエッジ検出信号を生成する。スタートビットサンプリング回路は、エッジ検出信号及び内部クロック信号に基づいてシンクフィールドのスタートビットのビット幅を計測し、計測されたビット幅を期待値として示す期待値信号を生成する。異常波形検出回路は、エッジ検出信号及び内部クロック信号に基づいてスタートビット以降のエッジ間の幅を計測し、エッジ間幅と期待値信号で示される期待値との間の誤差が所定の許容誤差範囲を超える場合に異常波形検出信号を生成する。

(もっと読む)

信号処理装置、情報処理装置、多値符号化方法、及びデータ伝送方法

【課題】多値信号の振幅平均値が期間毎に大きく変動するのを抑制可能な信号処理装置を提供すること。

【解決手段】互いに異なる第1及び第2のビット値で表現されたビット列から1ビットおきにビット値を抽出して得られる、奇数番目に位置するビット値で構成された第1のビット列と、偶数番目に位置するビット値で構成された第2のビット列と、をそれぞれ所定の符号化方式で符号化して直流成分を含まない第1及び第2の符号化信号を生成する符号化部と、前記符号化部で生成された第1及び第2の符号化信号よりも大きな振幅を有するクロック信号に対し、当該クロック信号が正の振幅値をとるタイミングに同期して前記第1の符号化信号を加算し、当該クロック信号が負の振幅値をとるタイミングに同期して前記第2の符号化信号を加算することにより多値信号を生成する信号生成部とを備える信号処理装置が提供される。

(もっと読む)

シリアル通信システム及びシリアル通信方法

【課題】MDライン及びSDラインの両方を同時にデータ送信に使用することができるシリアル通信システムを提供する。

【解決手段】本発明のシリアル通信システム1は、第1のデバイス2と第2のデバイス3とを有し、第1のデバイス2と第2のデバイス3とは、第2のデバイス3が生成したシリアルクロックに基づいて、相互通信を開始するシリアル通信システムである。第1のデバイス2から第2のデバイス3への出力が、前フェーズにおいて受信したデータの最終ビット値と反転していると、第2のデバイス3は第1のデバイス2の通信準備状態が完了状態であると判断し、相互通信を開始する。

(もっと読む)

シリアル通信装置

【課題】制御信号に適したシリアル伝送によって配線数を削減することが可能なシリアル通信装置の提供する。

【解決手段】複数の送信制御信号を送信シリアル信号に変換して外部に出力するP/S変換器と、外部から入力された受信シリアル信号を外部から入力された受信転送クロックを用いて複数の受信制御信号に変換するS/P変換器と、送信シリアル信号に同期した送信転送クロックを外部に出力するクロック出力回路と、受信シリアル信号に同期した受信転送クロックをS/P変換器に出力するクロック入力回路とを具備する。

(もっと読む)

シリアル通信装置

【課題】マスターとスレーブ間で制御信号のシリアル通信を行う際に、システムに応じた最適な通信レートで通信を行うことが可能なシリアル通信装置を提供する。

【解決手段】シリアル通信装置に、制御信号のサンプリングクロックを入力とし、当該サンプリングクロックに位相同期した逓倍クロックを生成する位相同期回路と、外部設定された分周比を用いて前記逓倍クロックを分周して転送クロックを生成する分周回路と、前記制御信号を前記転送クロックを用いてパラレル/シリアル変換して出力するP/S変換器とを設ける。

(もっと読む)

通信システム、送信装置、及び受信装置

【課題】 より効率的にデータの送受信を行うことができる通信システム、送信装置、及び受信装置を提供する。

【解決手段】 データを送信する送信装置(2、3)と、前記送信装置から送信されるデータを受信する受信装置(2、3)とを備える通信システム(1)であって、前記送信装置は、送信データのデータ部の第1のレベルのビットまたは第2のレベルのビットの数をカウントし、カウントした数に応じて反転処理を行うか否か判定する。反転処理を行う場合、前記送信装置は、送信データのデータ部の各ビットを反転させ、スタートビットを送信する場合のレベルを第3のレベルに設定し、送信する。受信装置は、データを受信し、受信したデータのスタートビットのレベルが前記第3のレベルである場合、前記受信データのデータ部に対して反転処理を行う。

(もっと読む)

11 - 20 / 51

[ Back to top ]