国際特許分類[H04N5/956]の内容

電気 (1,674,590) | 電気通信技術 (544,871) | 画像通信,例.テレビジョン (280,882) | テレビジョン方式の細部[4,2011.01] (126,971) | テレビジョン信号の記録 (37,482) | 以上のためのテレビジョン信号処理 (21,250) | テレビ信号またはその選択された部分の再生 (5,618) | 時間軸誤差の補償 (14) | 独立した書き込みおよび読み取りクロック発生器をもつデジタルメモリを用いるもの (10)

国際特許分類[H04N5/956]に分類される特許

1 - 10 / 10

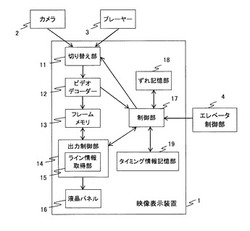

映像表示装置

【課題】表示映像のノイズの発生を防止することができる映像表示装置を提供する。

【解決手段】映像表示装置1は、第1のテレビ信号のデジタル映像データ及び第1の垂直同期信号を記憶するフレームメモリ13と、デジタル映像データ及び第2の垂直同期信号を出力する出力制御部14と、デジタル映像データを第2の垂直同期信号に同期して表示する液晶パネル16と、1フレームの前記デジタル映像データが前記フレームメモリに書き込まれた後に、出力制御部14がフレームメモリ13に書き込まれた1フレームのデジタル映像データを読み出すようするための情報として、第2の垂直同期信号と第1の垂直同期信号のタイミングのずれ情報であるタイミング情報を記憶するタイミング情報記憶部19と、第1の垂直同期信号とタイミング情報に基づいて、第2の垂直同期信号を出力させるように、出力制御部14を制御する制御部17とを備える。

(もっと読む)

画像処理装置及び画像処理方法

【課題】スキップ・リピート処理作業を簡素化し、処理能力を向上させた画像処理装置及び画像処理方法を提供する。

【解決手段】フィールド単位毎にインデックスが設定された記憶領域を有するメモリバンク14と、メモリバンク14における空き領域の前記インデックスを管理する入力管理キュー、及びメモリバンク14における出力可能なデータ領域の前記インデックスを管理する出力管理キューによって、メモリバンク14のデータ入出力を制御する入出力制御回路15を備え、入出力制御回路15は、前記出力管理キューによって出力可能なフィールド数を決定する手段と、決定されたフィールド数と閾値とを比較する手段と、比較結果に基づいて、スキップ処理又はリピート処理するか決定する手段と、を有する画像処理装置1である。

(もっと読む)

フレームシンクロナイザおよびその同期方法,画像処理装置並びにフレーム同期プログラム。

【課題】 画質を低下させることなくジャギーの発生を抑制する。

【解決手段】 フレームシンクロナイザ10は、第1の同期信号に同期して供給される入力映像データストリームを順次記憶するバッファメモリ14と、第2の同期信号に同期してバッファメモリ14から映像データを読み出すメモリ制御部15とを有する。メモリ制御部15は、バッファメモリ14の残存容量が所定の下限に達する前は、各フレームのうちの偶数番目水平ライン上の画素データからなる第1のフィールドと当該各フレームのうちの奇数番目水平ライン上の画素データからなる第2のフィールドとの一方のフィールドを所定の開始ラインより読み出すとともに他方のフィールドを第1の開始ラインより読み出す一方、バッファメモリ14の残存容量が前記所定の下限に達したときはこれに応じて、他方のフィールドのみを、前記第1の開始ラインから1水平ラインずれた第2の開始ラインより読み出す。

(もっと読む)

デジタル化ビデオ信号のための時間軸補正方法

【課題】標準信号の提供を可能にすべく改善されたアナログビデオ信号からデジタルビデオ信号の作成中の時間軸補正方法を提供すること。

【解決手段】 アナログビデオ信号を受信するステップと、ビデオデコーダを用いてアナログビデオ信号からデジタルビデオ信号を作成するステップと、デジタルビデオ信号の少なくとも一部をメモリに記憶するステップと、デジタルビデオ信号中の異常なフィールド順序を有している改ざんデータ部分を検出するステップと、改ざんデータの部分を切り捨てるステップか又は改ざんデータ部分の少なくとも一部をメモリに記憶されている先行データと置き換えるステップと、デジタルビデオ信号を出力するステップが含まれるようにする。

(もっと読む)

スレッショルド演算装置

【課題】時間軸誤差検出装置において、水平同期信号のパルスの後縁を用いて時間軸誤差を検出する場合に、誤った誤差情報を出力しないスレッショルド演算装置を提供することを目的とする。

【解決手段】ペデスタル平均値算出回路103、シンクチップ平均値算出回路104と誤判別防止回路202を備え、この誤判別防止回路202によって出力信号を選択する選択回路108は、ペデスタル平均値とシンクチップ平均値の中間値をスレッショルド値として出力する際に、ペデスタル平均値、シンクチップ平均値が正常値であるかどうかを判断して正常値であると判断すれば中間値を出力して、異常値と判断すれば擬似中間値を出力する。フィールドの最終ラインでは算出された中間値が異常と判断されるので画面上で映像が右に伸びることが無く、誤動作を防ぐことが出来る。

(もっと読む)

タイムベースコレクタ

【課題】 本発明は、タイムベースコレクタに関し、例えば家庭用ビデオテープレコーダから出力されるビデオ信号を処理する各種映像機器に適用して、同期の安定しないビデオ信号を処理する場合でも、画飛び、同一映像の繰り返しを有効に回避することができるようにする。

【解決手段】 本発明は、メモリ回路6における書き込みアドレス及び読み出しアドレスの差分値の平均値が所定値になるように、読み出しクロックRCKの周波数を可変する。

(もっと読む)

ビデオ信号処理装置

【課題】

MPEG2エンコーダ等の画像圧縮回路に、非標準信号が入力された場合に、画像がフリーズしたりあるいはブロックノイズを発生する等の不具合を解決する。

【解決手段】

時間軸補正回路15は、入力信号をメモリ6に格納し、入力信号のV同期から所定時間だけ遅れたタイミングで読み出す。そのため、入力フィールド毎に読み出し同期発生回路9をリセットする。リセット位置は読み出しV同期から3Hないし10Hだけ先行する位置とする。入力信号がノンインターレース信号であるか、フィールド長が標準値からずれているかを検出し、同期信号のodd/even順序や同期タイミングを補正する。また、入力信号が非標準信号の場合は、

画像圧縮回路16,17を通過させないで出力できるように切換スイッチ18を設ける。

(もっと読む)

映像信号処理装置

【課題】 非標準の入力映像信号が入力された場合にも安定した表示をコストの増加を招くことなく実現する。

【解決手段】 入力映像信号を与えられてA/D変換を行い映像データを出力するA/D変換器1、映像データに含まれる垂直同期、水平同期信号を分離する同期分離回路7、水平同期信号に同期した書き込みクロック、水平同期信号に同期又は非同期である読み出しクロックを生成するクロック生成回路10、垂直同期及び水平同期信号を与えられ入力映像信号の標準/非標準を判定する非標準判定回路13、映像データの書き込み、読み出しを行うメモリ4、垂直同期信号に同期した書き込み開始信号を生成し映像データの書き込み開始のタイミングを制御する書き込み制御回路8、入力映像信号が標準信号である場合垂直同期信号に同期した読み出し開始信号に従って映像データ信号の読み出し開始のタイミングを制御し、非標準信号である場合垂直同期信号と非同期である読み出し開始信号に従って制御する読み出し制御回路9を備える。

(もっと読む)

時間軸処理装置

時間軸処理装置

【課題】 時間軸処理装置を従来よりも回路規模を小さくして構成する。

【解決手段】 固定位置補間手段4がメモリ3からのディジタル映像信号を整数倍の標本化周波数によってオーバーサンプリングした信号に対して、可変位置補間手段5が時間軸誤差情報に基づいて補間し、基準の時間軸を有するディジタル映像信号を得ることにより、時間軸誤差を補正する。これにより、可変位置補間手段5に用いるフィルタは、通過帯域以上の帯域における減衰が緩やかな周波数特性になるので、このフィルタはタップ数が減らせ乗算器数が減らせる。

(もっと読む)

1 - 10 / 10

[ Back to top ]