エルピーダメモリ株式会社により出願された特許

1,101 - 1,110 / 2,599

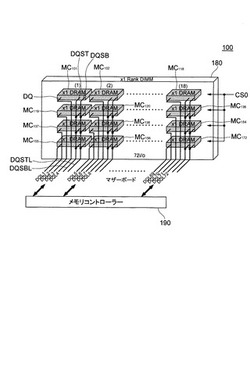

メモリモジュール

【課題】メモリバッファを用いることなく、各チャネルにかかる負荷が低減されたメモリモジュールを提供する。

【解決手段】モジュール基板180と、モジュール基板180に搭載されたメモリチップMC101〜MC172と、メモリチップMC101〜MC172にそれぞれ個別に接続され、リードデータ又はライトデータが伝送されるデータ入出力配線DQL1〜DQL72とを備える。メモリチップMC101〜MC172の数は、データ入出力配線DQL1〜DQL72を介して同時に伝送されるリードデータ又はライトデータのビット数と等しい。このように、複数のデータ入出力配線がそれぞれ個別のメモリチップに接続されていることから、メモリバッファを用いることなく、各チャネルにかかる負荷を低減することが可能となる。

(もっと読む)

半導体装置

【課題】リード動作時における位相調整精度を低下させることなく、DLL回路の消費電力を低減する。

【解決手段】ODT機能を有するデータ入出力回路80と、データ入出力回路80の動作タイミングを規定する内部クロックLCLKを生成するDLL回路100とを備える。DLL回路100は、内部クロックLCLKを高精度に位相制御する第1のモードと、低消費電力で動作する第2のモードとを有し、データ入出力回路80がODT動作を行っていない場合には第1のモードで動作し、データ入出力回路80がODT動作を行っている場合には第2のモードで動作する。このように、ODT動作の有無によってDLL回路100の動作モードを切り替えていることから、厳密な位相制御が不要なODT動作時における消費電力を低減することが可能となる。

(もっと読む)

マスクパターン生成装置、マスクパターン生成方法及び半導体装置

【課題】データ率を向上することが可能なレイアウト設計データを生成するマスクパターン生成装置を提供する。

【解決手段】マスクパターン生成装置1は、測定部3と、変更部4と、を含む。測定部3は、半導体装置の回路素子を構成する素子パターンと、回路素子を構成しないダミーパターンと、を含むレイアウト設計データに基づいて、ダミーパターンと他のパターンとの間隔を測定する。変更部4は、測定部3にて測定された間隔が予め指定された指定値よりも大きい場合、その間隔を規定しているダミーパターンを拡大して、その間隔が短縮するように、レイアウト設計データを変更する。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】ビット線とシリコンピラーとを接続するための開口部の形成を容易化する。

【解決手段】半導体記憶装置10は、マトリクス状に配置され、それぞれの側壁にゲート絶縁膜12を介してゲート電極13が形成され、かつそれぞれの上端が記憶素子と電気的に接続される多数のシリコンピラー11と、各シリコンピラー11の間を互いに直交する方向に配線されたビット線BL及びワード線WLとを備える。ビット線BLは、両側のシリコンピラー11の下端と、1行おきに電気的に接続し、ワード線WLは、両側のシリコンピラー側壁にそれぞれ形成されたゲート電極13と、1列おきに電気的に接続する。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】チャネル間の相互影響を抑制しつつ、少なくとも3F2のレイアウトを実現する。

【解決手段】半導体記憶装置1は、Y方向に垂直な2側面のうちの一方の側面12aの領域13aに第1のチャネルCH1、他方の側面12bのうちY方向に見て領域13aと重ならない領域13bに第2のチャネルCH2がそれぞれ設けられるとともに、これらの側面12a,12bの他の領域が酸化されて絶縁酸化膜とされたシリコンピラー11と、それぞれゲート絶縁膜14a,14bを介して側面12a,12bを覆う2本のワード線WLとを備え、第1のチャネルCH1と第2のチャネルCH2とが、上記絶縁酸化膜によって絶縁分離されている。

(もっと読む)

半導体装置及びその製造方法

【課題】微細化に対応可能であり、不純物拡散領域上に形成したコンタクトプラグが近傍の導電材料とショートすることを防止する配線構造を有する半導体装置を提供する。

【解決手段】半導体基板内の不純物拡散領域22上に選択エピタキシャル成長法により、第1の層16aを形成する工程と、第1の層16a上に、選択エピタキシャル成長法により第2の層18を形成する工程と、第2の層18上に導電材料を充填することにより、コンタクトプラグ21を形成する工程と、を有する。

(もっと読む)

基板洗浄装置および基板洗浄方法

【課題】基板面内に、洗浄ブラシの回転方向と基板の回転方向とが同じとなる部分の割合が非常に少なく、回転方向の同じ部分と反対の部分とが存在することに起因する基板面内での洗浄能力のばらつきが小さく、高い洗浄効果が得られる基板洗浄装置を提供する。

【解決手段】基板1を保持し、基板1を回転させる基板回転手段30と、基板面と平行で基板回転軸aと交差するブラシ回転軸の延在方向に並べて配置された2つの洗浄ブラシ7、8(10)を備え、2つの洗浄ブラシ7、8(10)がブラシ回転軸を中心として相反する方向に回転されるものであって、各洗浄ブラシ7、8、10が基板1の回転方向と反対方向に回転される一対のブラシ40(50)と、一対のブラシを回転させるとともに、ブラシ回転軸の延在方向に一対のブラシを往復移動させるブラシ駆動手段12とを備える基板洗浄装置20とする。

(もっと読む)

フォトマスクおよびフォトマスクの製造方法

【課題】非解像パターンを形成するためのレジストパターンが所望の形状とは異なった状態となり、その状態でフォトマスク上の金属膜に転写されることを防止することで、所望のパターン形状の非解像パターンを備えたフォトマスクを提供する。

【解決手段】配線用解像パターン1と、配線用解像パターン1の光隣接効果を補正するために配線用解像パターン1に離間して配置された非解像パターン2とを具備してなり、非解像パターン2の平面視形状が、その長手方向に沿って湾曲した形状とされていることを特徴とするフォトマスクを採用する。

(もっと読む)

半導体装置の製造方法

【課題】封止体を形成する際の封止体の漏れを抑制する。

【解決手段】まず、半導体装置の配線基板となるべき製品形成部が形成された配線母基板31を準備する。そして、製品形成部に半導体チップ15を搭載し、配線母基板の、半導体チップが搭載されるチップ搭載面側に、配線母基板を型閉めする成型金型70の内面に圧接する圧接部材51aを搭載する。その後、成型金型によって、配線母基板のチップ搭載面とは反対側の面93と圧接部材とを圧接するように、成型金型で配線母基板を型閉めする。そして、成型金型の内部に封止体18を充填する。

(もっと読む)

半導体パッケージ用基板、該基板を用いた半導体パッケージ、および半導体パッケージ用基板の製造方法

【課題】半導体パッケージの小型化と実装温度サイクル耐性との両立を図る。

【解決手段】パッケージ基板1において、基板コア層3にランド6と接する位置より、ランド6の径より小さい径の孔14が掘削され、当該孔に基板コア層3の材料より弾性率が低い低弾性樹脂11が充填されている。

(もっと読む)

1,101 - 1,110 / 2,599

[ Back to top ]