川崎マイクロエレクトロニクス株式会社により出願された特許

101 - 110 / 449

PLL回路

【課題】面積増大や消費電流増大を伴うことなくPLLロック時の位相オフセット量により生じるクロックの位相ばらつきを極力小さし、またロック後の温度や電源電圧変動へも対応できるようにする。

【解決手段】基準クロックCLK1と帰還クロックCLK2の位相を位相周波数比較器41で比較した結果に応じて出力クロックCLK3の周波数を決定するPLL回路において、出力クロックCLK3がクロックバッファ6を介して入力する分周回路5と分周回路5の出力クロックが入力し帰還クロックCLK2を出力する可変遅延回路9と、その帰還クロックCLK2の位相と基準クロックCLK1の位相を比較する位相比較器8とを備える。可変遅延回路9は、位相比較器8における基準クロックCLK1の位相と帰還クロックCLK2の位相の位相差がキャンセルされるようにその遅延量が制御され、結果としてPLL出力クロックCLK3の位相を調整できる。

(もっと読む)

半導体集積回路

【課題】配線の混雑を減少し、配線効率を向上させることができる電源配線構造を有する半導体集積回路を提供する。

【解決手段】主電源配線層と中間電源配線層との間には、第1の主電源配線と重なる位置に、第1の主電源配線と第1の中間電源配線とを接続する第1の中間接続ビアが設けられ、第2の主電源配線と重なる位置に、第2の主電源配線と第2の中間電源配線とを接続する第2の中間接続ビアが設けられる。中間電源配線層と副電源配線層との間には、第1の中間電源配線と第1の副電源配線とを接続する第1の副接続ビアと、第2の中間電源配線と第2の副電源配線とを接続する第2の副接続ビアとが、それぞれ複数、第1の方向に並ぶ副接続ビア列が、第2の方向に複数配置される。中間電源配線層の第2の中間電源配線には、第2の中間接続ビアと第2の副接続ビアとを接続する接続配線が含まれる。

(もっと読む)

スケルチ検出回路

【課題】温度、プロセス、電源電圧の変動に強く、安定したスケルチ検出信号を出力することができるスケルチ検出回路を提供する。

【解決手段】受信した差動信号RX+,RX−の電位振幅が所定値を超えているときその検出信号Vpをパルスとして出力するピーク検出回路11と、ピーク検出回路11から出力する検出信号Vpのパルス幅を差動信号RX+,RX−の少なくとも1周期分延長するパルス幅延長回路12とを備える。ピーク検出回路11は、差動信号RX+,RX−に同一のDCバイアスを与えた後にその差分に対応する電圧信号Vdataを出力する入力差動増幅回路11Aと、入力差動増幅回路11Aのほぼレプリカ回路として構成され、参照電圧Vref’をレベルシフトしたシフト参照電圧Vrefを出力するレプリカ参照電圧生成回路11Bと、電圧信号Vdataとシフト参照電圧Vrefとを比較して検出信号Vpを出力する電圧比較回路11Cと、を備える。

(もっと読む)

画像処理装置

【課題】 回路規模の増大を抑えたまま、高画質の画像を得ることができる画像処理装置を提供する。

【解決手段】 入力される画像データINを、画像特徴抽出回路11でフレームN−1の期間の後半から次のフレームNの期間の前半にかけて収集して画像データINの特徴を抽出し、フレームNの期間の前半の終了後に、補正係数演算回路20でフレームN+1の期間に設定される補正係数を、上記抽出した特徴に応じて演算し、その補整係数を画像補整演算回路30でフレームN+1の画像データに反映させる。

(もっと読む)

信号品質評価方法および信号品質評価システム

【課題】 PONにおける送受信データの信号品質を安価に評価することができる信号品質評価方法および信号品質評価システムを提供する。

【解決手段】 2ビットを1単位としてトグルされる擬似ランダム連続データを基本にしてプリアンブル部終了後に1ビットを挿入して180度の位相ずれを生じさせた試験用バーストモードデータをデータ生成機11で生成してOLT20に入力し、CDR回路21で試験用バーストモードデータのパターンを判定し、判定されたパターンと期待値パターンとを受信比較機12で比較してビット誤り率(BER)を算出する。

(もっと読む)

半導体集積回路

【課題】 回路面積を小さく抑えたまま、出力電圧レベルのテストを短時間で且つ高精度に行なうことができる半導体集積回路を提供する。

【解決手段】 接点14_1をオン状態にして内部回路10_1から‘L’レベルの信号S1を印加してPMOSトランジスタ11_1をオン状態にするとともに、接点15_2をオン状態にしてNMOSトランジスタ13_3,11_2からなるカレントミラーを形成してNMOSトランジスタ11_2に、電流I3がミラーされた電流I5を流して、出力端子12の電圧VOHのレベルをテストし、また、接点15_1をオン状態にして内部回路10_2から‘H’レベルの信号S2を印加してNMOSトランジスタ11_2をオン状態にするとともに、接点14_2をオン状態にしてPMOSトランジスタ13_2,11_1からなるカレントミラーを形成してPMOSトランジスタ11_1に、電流I2がミラー化された電流I4を流して、出力端子12の電圧VOLのレベルをテストする。

(もっと読む)

半導体装置の製造方法

【課題】シリサイド層上に成膜された層間絶縁膜の剥離による、半導体装置の製造歩留まりの低下等の不具合発生を防止できる半導体装置の製造方法を提供する。

【解決手段】サリサイド工程を行うに際し、素子形成領域以外の半導体基板表面の露出領域の少なくとも一部に、素子形成領域以外の半導体基板表面の露出領域の半導体基板表面にシリサイド層が形成されることを防止するマスクとなるサリサイドブロックを半導体基板表面上に形成する。素子形成領域以外の半導体基板表面の露出領域は、半導体ウェハの周辺露光領域境界から高融点金属の成膜領域境界までのリング状の領域、スクライブラインの領域を含む。

(もっと読む)

ノイズ低減回路

【課題】面積効率が高く、応答性およびESD耐性も問題が生じないノイズ低減回路を提供する。

【解決手段】ノイズ低減回路は、電源とグランドとの間に配置された容量素子および抵抗素子を含むデカップリング容量回路と、容量素子と抵抗素子との接続点とグランドもしくは電源との間に接続されたダイオード素子とを備える。電源とグランドとの間の電位差が小さくなった場合、ダイオード素子がオン状態になると、グランドからグランド、または、電源から電源へ向かって電流が流れることで、電源ノイズを瞬時に低減できる。

(もっと読む)

電源装置、および、その制御方法ならびに半導体装置

【課題】特別な素子を用いず、実現するための費用も抑えることができる電源装置と、その制御方法、ならびに、回路構成が簡単で外部との接続端子数も少ない制御用半導体装置を提供する。

【解決手段】2次側回路が同期整流方式の2次側スイッチング素子を用いて出力電圧の整流を行う電源装置において、2次側回路が有する補助巻線に現れる信号、もしくは、2次巻線のタップに現れる信号に基づいて、2次側スイッチング素子をオンおよびオフとすべきタイミングを検知し、この検知したタイミングに基づいて、2次側スイッチング素子の動作を制御する駆動信号を生成し、駆動信号により2次側スイッチング素子の動作を制御する。

(もっと読む)

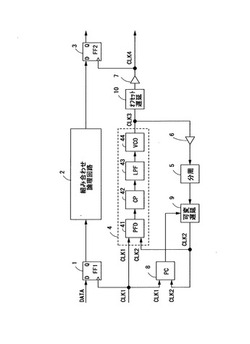

PLL位相合わせ回路

【課題】PLL回路のリファレンスクロックが停止された後に再開された場合、再開後のリファレンスクロックとフィードバッククロックとの位相合わせを短時間で行い、再ロックさせることができるPLL位相合わせ回路を提供する。

【解決手段】PLL位相合わせ回路は、PLL回路と、フィードバッククロックを分周する第1の分周回路と、PLL回路の出力クロックを分周する第2の分周回路と、リファレンスクロックの動作状態を監視するクロックモニタ回路とを備える。第1の分周回路の分周数は、第2の分周回路の分周数と等しく、クロックモニタ回路が、リファレンスクロックが停止されたことを検出すると、第1の分周回路がリセットされてフィードバッククロックが停止され、リファレンスクロックが再開されたことを検出すると、第1の分周回路のリセットが解除されてフィードバッククロックが再開される。

(もっと読む)

101 - 110 / 449

[ Back to top ]