株式会社ルネサステクノロジにより出願された特許

181 - 190 / 4,790

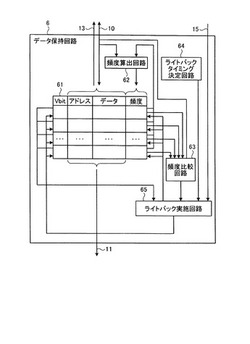

MRAM制御装置およびMRAM制御方法

【課題】MRAMからの読み出し回数を増やさず、システム全体の電流量を低減することができるMRAM制御装置を得ること。

【解決手段】MRAMの書込みを制御するMRAM制御装置であって、書込み要求に含まれるデータを、書込みアドレスと書込み要求回数を示す頻度情報と対応づけて保持するデータ保持メモリ61と、保持している書込みアドレスに対して書込みのあった回数を計数して頻度情報としてデータ保持メモリ61に格納する頻度算出回路62と、書込み要求に含まれる書込みアドレスと保持している書込みアドレスとを比較し、一致するアドレスがなく、空き領域が無い場合には、頻度情報に基づき頻度の小さいデータを選択し、選択したデータをMRAMへ書込み、そのデータが格納されていたデータ保持メモリ61の領域に、書込み要求に含まれるデータを書込む。

(もっと読む)

半導体装置およびその製造方法、ならびに電源装置

【課題】電界効果型トランジスタを備えた半導体装置において、チャネル抵抗を低減する。

【解決手段】厚さ方向に沿って互いに反対側に位置する第1主面S1および第2主面S2を持つ半導体基板1に、トレンチゲート型の電界効果型トランジスタを有する半導体装置であって、前記トレンチゲート型の電界効果型トランジスタは、前記第1主面S1側に第1半導体領域2と、前記第2主面S2側に第2半導体領域5と、その間に半導体ウェル領域3と、第2主面と交差する第1方向Aに延びるように形成された溝部9と、その内面にゲート絶縁膜6を介して形成されたゲート電極8とを備え、ゲート電極8の底部BGは第1半導体領域2にあり、ウェル底部BWは、ウェル深部DBWとウェル浅部SBWとを有し、ウェル深部DBWは、ゲート絶縁膜6に対して、ウェル浅部SBWよりも遠い領域にあることを特徴とする。

(もっと読む)

マイクロコンピュータ

【課題】チップ外に出力されるクロック信号と、チップ内のクロック信号との間の位相差を低減する。

【解決手段】第1クロック信号を発生可能な発振器(101)と、上記第1クロック信号とフィードバック信号との位相比較を行い、それに基づいて第2クロック信号を形成するPLL回路(102)とを設ける。さらに、上記第2クロック信号に基づいて、チップ内部に供給される第3クロック信号と、チップ外部に出力される第4クロック信号(CLK(φ))とを形成するクロックパルスジェネレータ(103)と、クロック遅延補正データが格納されるクロック遅延補正データ記憶部(105)とを設ける。上記PLL回路に、上記フィードバック信号を補正するための可変ディレイ回路(13)を設け、上記位相差低減のためのクロック遅延補正を行う。

(もっと読む)

半導体装置

【課題】電界効果トランジスタ、特に、アンテナスイッチのスイッチング素子を構成する電界効果トランジスタで発生する高次高調波の発生を低減できる技術を提供する。

【解決手段】メアンダ構造をしているトランジスタQ1において、ゲート入力側に最も近い部分トランジスタのゲート幅を大きくする。具体的には、図5に示すように、櫛歯状電極CL(1)をその他の櫛歯状電極CL(2)〜CL(n)よりも長くするように構成している。言い換えれば、フィンガー長Lw1をその他のフィンガー長Lwjよりも長くしている。特に、櫛歯状電極CL(1)を櫛歯状電極CL(1)〜CL(n)の中で最も長くする。

(もっと読む)

内部電圧発生回路

【課題】安定に所望の補償範囲を有する温度補償された内部電圧を制御性よく生成する。

【解決手段】温度依存性を有しない参照電圧(VOUT16)から温度依存性を有する基準電圧(VREF16)を温度特性付加回路(10)により生成する。この基準電圧をアナログ/デジタル変換し、そのアナログ/デジタル変換値を内部電圧のレベルを規定する基準コード情報(TN_VREF<4:0>)と加算する。この加算値(TN_VREF2<4:0>)をデジタル/アナログ変換して温度依存性を有するオフセット電圧(Vrefos)を生成する。このオフセット電圧に基づいて、必要なレベルの内部電圧(VCPP)を生成する。

(もっと読む)

半導体装置の製造方法

【課題】サリサイドプロセスで金属シリサイド層を形成した半導体装置の信頼性を向上させる。

【解決手段】ゲート電極GE1,GE2、ソース・ドレイン用のn+型半導体領域7b及びp+型半導体領域8bを形成してから、半導体基板1上にNi1−xPtx合金膜を形成し、第1の熱処理を行って合金膜とゲート電極GE1,GE2、n+型半導体領域7b及びp+型半導体領域8bとを反応させることで、(Ni1−yPty)2Si相の金属シリサイド層41aを形成する。この際、Niの拡散係数よりもPtの拡散係数の方が大きくなる熱処理温度で第1の熱処理を行ない、かつ、金属シリサイド層41a上に合金膜の未反応部分が残存するように、第1の熱処理を行なう。これにより、y>xとなる。その後、未反応の合金膜を除去してから、第2の熱処理を行って金属シリサイド層41aを更に反応させることで、Ni1−yPtySi相の金属シリサイド層41bを形成する。

(もっと読む)

コンパレータ

【課題】低い電源電圧を使用する場合であってもラッチ状態を解消可能であり、かつ高速動作が可能なコンパレータを提供する。

【解決手段】出力ノードN1とPMOSトランジスタM3のソースとの間には、電源Vdd側から順に、PMOSトランジスタM5およびダイオードD1が直列に接続されて第1の電圧差解消手段を構成している。また、出力ノードN2とPMOSトランジスタM4のソースとの間には、電源Vdd側から順に、PMOSトランジスタM6およびダイオードD2が直列に接続されて第2の電圧差解消手段を構成している。なお、NMOSトランジスタM1およびM2のゲートには、それぞれアナログプラス入力電圧Vinpおよびアナログマイナス入力電圧Vinnが与えられ、リセットスイッチとして機能するPMOSトランジスタM5およびM6のゲートにはリセット信号RSTNとして接地電圧Vssが与えられる構成となっている。

(もっと読む)

マイクロコンピュータ

【課題】動作モードの指定を可能とする外部端子を電源端子あるいはグランド端子として十分に機能させることができ、しかも、当該外部端子の論理を外部から容易に切り替え可能にする。

【解決手段】内部回路(102〜107)と、グランドライン(29)と、電源ライン(28)と、上記内部回路の動作モードを指定可能な外部端子(20,21)と、電源スイッチ回路(101)とを設ける。上記電源スイッチ回路には、上記外部端子を電源ライン又はグランドラインに接続するための第1電源ドライバ(40)と、上記第1電源ドライバよりも小さな駆動能力を有し、上記外部端子を電源ライン又はグランドラインに接続するための第2電源ドライバ(41)とを設ける。上記内部回路のリセット期間中は上記第1電源ドライバの回路動作を禁止し、上記内部回路のリセット解除後に上記第1電源ドライバの回路動作を許可することで、上記課題を解決する。

(もっと読む)

半導体装置およびその製造方法

【課題】下地段差を考慮したリソグラフィマージンを確保しつつ、高集積度と歩留り向上との両立を図ることを可能とした、半導体装置およびその製造方法を提供する。

【解決手段】CMP後の層間絶縁膜ID11が、第1面SF11とこの第1面SF11よりも基板側に位置する第2面SF12を有し、第1面SF11に形成される第1ホールCH11の最上部の径(D11d)が、第2面SF12に形成される第2ホールCH12の最上部の径(D12d)よりも大きく設けられる。

(もっと読む)

半導体装置の製造方法

【課題】銅を主成分とするコンタクトプラグを有する半導体装置において、コンタクトプラグに隆起が発生することを防止する。

【解決手段】第1の層間絶縁膜102に、金属シリサイド層101に到達するコンタクトホール103を形成する工程(c)と、コンタクトホールの底面及び側壁に、高融点金属膜104を形成する工程(d)と、高融点金属膜上に、銅を主成分とする金属膜106Aを形成し、コンタクトホール内に、高融点金属膜を介して、金属膜が埋め込まれてなるコンタクトプラグ107を形成する工程(e)と、第1の層間絶縁膜及びコンタクトプラグの上に、第2の層間絶縁膜108を形成する工程(f)とを備え、工程(f)は、コンタクトプラグの表面に存在する酸素ガスを除去する工程(f1)と、工程(f1)の後に、コンタクトプラグの表面に存在する酸素ガスが除去された状態で、第2の層間絶縁膜を形成する工程(f2)とを含む。

(もっと読む)

181 - 190 / 4,790

[ Back to top ]