サンディスク コーポレイションにより出願された特許

21 - 30 / 175

周辺装置用ソフトウェア開発キットのアクセス認証

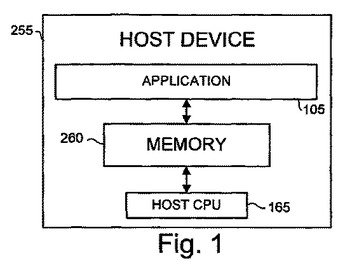

周辺装置のためのコードセットがホスト装置にインストールされる。コードセットは、ホスト装置から周辺装置へのアクセスを制御するために使用される。コードセットはまた、ホスト装置上のソフトウェアエンティティが周辺装置にアクセスするために使用する1つ以上のコードサブセットを含む。ホスト装置上のソフトウェアエンティティは、ホスト装置にインストールされたコードセットにより首尾よく認証されなければならない。ソフトウェアエンティティが首尾よく認証されると、ソフトウェアエンティティに専用の1つ以上のコードサブセットにアクセスできるようになる。ソフトウェアエンティティは1つ以上のコードサブセットを使って周辺装置にアクセスできる。  (もっと読む)

(もっと読む)

マルチバンク記憶装置のためのストレージアドレス再マッピングのための方法およびシステム

マルチバンクメモリにおけるストレージアドレス再マッピングのための方法およびシステムが開示される。この方法は、クラスタのブロックの中の論理アドレスを割り当てることと、論理アドレスをストレージアドレス空間内に再マッピングすることとを含み、論理アドレス空間内に分散しているホストデータの短いランはストレージアドレス空間においてメガブロックの中に連続的にマッピングされる。各バンクにおいて独立に、特定のバンク内で利用可能な新しいブロックの数が所望しきい値未満まで減ったとき、マルチバンクメモリの各バンクにおいてデータを受け取るために利用し得る新しいブロックを作るために、有効なデータおよび使用済データの両方を有するブロックからそれぞれのバンクの中で有効なデータがフラッシングされる。  (もっと読む)

(もっと読む)

ダイナミックデータラッチ要求を備えたキャッシュ操作における適合アルゴリズム

不揮発性メモリは、1つ以上のアドレス指定されたページの指定されたグループに、データラッチの対応するセットに保存された最初の1セットのデータを使用し、最初の操作(例えば、書き込み操作)を実行できる。また、これらの対応するデータラッチを使用する2番目の1セットのデータの2番目の操作(例えば、読み出し操作)の要求を受け取ることもできる。最初の操作の間、対応したそれぞれのセットの少なくとも1個のラッチが2番目の操作に利用可能になり、データラッチの対応するセットに十分な数があると、メモリでは最初の操作の間に、2番目の操作が実行される。そうでない場合には、2番目の操作が遅れることになる。最初の操作の間に十分な数のラッチが利用可能になると、メモリは続いて2番目の操作を実行できる。2番目の操作を実行するために対応するセットの十分な数のデータラッチがあるかどうかの判断に応じて、十分な数があることが判断されると、最初の操作の間に2番目の操作が実行される。  (もっと読む)

(もっと読む)

オンチップコピー操作適合データスクランブリングを提供するシステム、方法、およびメモリデバイス

フラッシュメモリデバイスの外部で実装されるデータスクランブリング手法を開示する。これは、フラッシュデバイスの内部で作用するフラッシュメモリオンチップコピー機能と協調的に使用できるため、高性能コピー操作をサポートする。ヘッダや制御構造等、フラッシュに記憶されるデータはすべてスクランブルできる。停電に耐えるうえ、データを逆スクランブルし再度スクランブルせずともフラッシュの内部でデータを再配置できる等、堅牢なファイルシステム操作を達成できる。ハードウェアに基づく典型的なソリューションの場合はシステム全体の性能におよぶ影響が皆無かごく僅かであり、非常に低い増分コストでシステム全体の信頼性を向上させることができる。このデータスクランブリング手法では、望ましくはシードスクランブル鍵の決定にあたって物理アドレスではなく、論理ブロックアドレスや論理ページアドレス等の論理アドレスを使用する。  (もっと読む)

(もっと読む)

プログラマブル電圧出力回路を使用する集積回路の拡張駆動能力

集積回路(IC)は、電源電圧表示などのICの状態の表示に対応する第1のモードまたは第2のモードで動作するように、コンフィグレーション入力によって電気的に設定可能な出力駆動回路部を含み、第1のモードと第2のモードとは、異なる駆動特性を有する。改良形ICの一部としてのコンフィグレーションインターフェイス回路部は、ICの状態に関係なく駆動強度制御入力に基づいて第1のモードまたは第2のモードに出力駆動回路部の動作を設定するために、コンフィグレーション入力を選択的にオーバライドするようになっている。  (もっと読む)

(もっと読む)

ソースレベルを追跡するためのワード線基準レベルの読み出し、ベリファイ

不揮発性記憶装置は、並行して感知されるべきメモリセルの個々のページを有する。この記憶装置は、ワード線電圧源からの所定のワード線電圧と1つ以上のページの集合ソースノードにおける電圧レベルとを受け取るように結合されると共に感知操作中にメモリのワード線に出力電圧を提供するように結合されたソースレベル追跡回路を含み、このソースレベル追跡回路はオペアンプを含み、出力電圧は、集合ノードにおける電圧レベルを追跡すると共に接地ループにおける有限の抵抗に起因するソースバイアスエラーを補償するための量だけオフセットされたワード線電圧である。  (もっと読む)

(もっと読む)

自己構成型マルチレギュレータASICコア電力供給

電子機器は特定用途向け集積回路(ASIC)を有し、このASICは、オプションの外部キャパシタンスとともに使用する線形レギュレータモジュールと、製品の内部キャパシタンスへ結合されるキャプレスレギュレータモジュールの両方をその回路に備える。電子機器を操作する方法は、キャプレスレギュレータモジュールの低電力サブモジュールと高電力サブモジュールとのうちのASICの電力投入段階に使用するいずれか一方のモジュールを選択する。ASICの制御ロジックは、外部キャパシタンスの有無を検出する。外部キャパシタンスが存在する場合は、ASICの電力投入段階に高電力キャプレスサブモジュールを使用し、存在しない場合は、ASICの電力投入段階に低電力キャプレスサブモジュールだけを使用する。制御ロジックはASIC電力投入後に、ある特定の動作期間中には線形レギュレータモジュールを、別の動作期間中にはキャプレスレギュレータモジュールを選択するほか、電力投入後の動作の全期間にわたり一方または他方を選択することもある。  (もっと読む)

(もっと読む)

有効電力のマルチレンジおよび局所的検出を備えたシステムおよび回路

電力有効検出を自動的および/または局所的に適合させる方法およびシステム。実施形態の1つの種類では、ローカルパワーオンリセット回路は、個々の電力アイランドに含まれ、実施形態の他の種類では、パワーオンリセット回路は、どちらのケースでも同じ回路を電力有効検出に使用するために、検出されたインターフェイス電圧レベルに応じて、自動的に再プログラムされる。  (もっと読む)

(もっと読む)

不揮発性メモリ用の低ノイズセンス増幅器アレイおよび方法

対応する検知モジュールのグループを備える不揮発性メモリセルのページを並列に検知している際、各高電流セルが特定されると、ページ内の他のセルが引き続き検知を受ける間、そのセルは後の検知からロックアウトされる。すると、ロックアウトされたセルに関与する検知モジュールはロックアウトモードに入り、非アクティブになる。検知モジュールがロックアウトモードになっているときは、その検知モジュールからのノイズ源の影響が大きくなる。ノイズは、そのビット線を通じて近隣のビット線に結合することによって、近隣のセルの検知に干渉しやすい。ノイズは、ページの共通ソース線を通じて結合して、ページ内で継続しているセルの検知の精度に影響を及ぼす可能性もある。改良形検知モジュールおよび方法は、ロックアウト検知モジュールからのノイズを分離し、ページ内のメモリセルの検知中に依然としてアクティブである他の検知モジュールに影響を及ぼさないようにする。  (もっと読む)

(もっと読む)

ASICコアのためのマルチレギュレータ電力供給システム

電子製品と操作方法を開示する。電子製品は特定用途向け集積回路(ASIC)装置を含み、ASIC装置は、任意の外部キャパシタンスへ結合されるように構成された線形レギュレータモジュールと、電子製品の内部キャパシタンスへ結合されるように構成されたキャップレスレギュレータモジュールの両方を含む。ASIC装置の制御ロジックはレギュレータ選出信号に応答し、線形レギュレータモジュールとキャップレスレギュレータモジュールとのうち、ASIC装置の給電に用いるいずれか一方のモジュールを選出する。制御ロジックは、ある特定の動作期間中に線形レギュレータモジュールとキャップレスレギュレータモジュールとのうち、いずれか一方を選出できる。  (もっと読む)

(もっと読む)

21 - 30 / 175

[ Back to top ]