ソイテックにより出願された特許

71 - 80 / 93

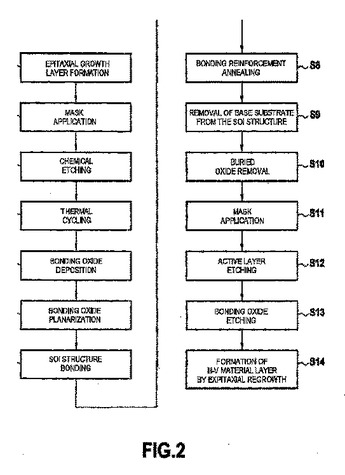

多層構造及びその製造プロセス

本発明は、多層構造を製造するためのプロセスであって、a)シリコン基板上で成長層をエピタキシャル成長するステップ(S1)と、b)成長層において少なくとも1つのパターンを形成するステップ(S2、S3)と、c)シリコン基板上に酸化層を堆積するステップ(S5)と、d)シリコン活性層を酸化層上へ転移するステップ(S7−S10)と、e)各パターンの上のシリコン活性層及び酸化層内にキャビティを形成するステップ(S11、S12)と、f)III−V族の物質のキャビティを成長層の各々の暴露されたパターンから成長させるステップ(S14)とを少なくとも備えることを特徴とするプロセスに関する。  (もっと読む)

(もっと読む)

高熱消散基板を製造する方法

本発明は、同じ寸法を有するバルクの単結晶シリコン構造よりも優れた熱消散特性を備えた複合構造を製造する方法に関し、該構造は、支持基板を備え、支持基板および上部層の間の上部層および酸化層を備えており、a)単結晶材料からなる上部層を設けること、b)上記構造を得るために、高い熱消散特性を有する多結晶材料からなる支持基板を上部層に結合することであって、不活性ガス雰囲気又は還元雰囲気で、所定の温度で所定の継続期間、構造を熱処理して、酸化層の少なくとも一部を分解することによって熱消散特性を増大することを特徴とする。  (もっと読む)

(もっと読む)

半導体オンインシュレータ構造体を製造する方法

本発明は、エレクトロニクスまたはオプトエレクトロニクス用の構造体を処理するプロセスに関し、この構造体は、連続的に、・基板と、・第1の酸化物層と、・中間層と、・半導体材料の酸化物で作製された第2の酸化物層と、・前記半導体材料で作製された薄い半導体層とを含み、このプロセスは、第2の酸化物層の厚さが所定の値だけ縮小するように、半導体層を通して第2の酸化物層のある量の酸素を拡散させるように選ばれた温度および持続期間による不活性または還元雰囲気中での構造体の熱処理を含むことを特徴とする。本発明は、さらに、前記熱処理を含むエレクトロニクスまたはオプトエレクトロニクス用の構造体を製造するプロセスに関する。  (もっと読む)

(もっと読む)

半導体ヘテロ構造

【課題】より小さな表面凹凸をもつ半導体ヘテロ構造を提供すること。

【解決手段】本発明は、第1の面内格子定数をもつ支持基板と、該支持基板上に形成されていて、上部に格子緩和状態おいて第2の面内格子定数をもつ緩衝構造と、および該緩衝構造上に形成された組成非傾斜層の多層積層とを備えた半導体ヘテロ構造に関するものである。表面凹凸の少ない、前記のタイプの半導体ヘテロ構造を提供することが本発明の目的である。前記の目的は、該組成非傾斜層が歪み層であり、かつ、該歪み層が前記第1および第2の格子定数の中間の第3の面内格子定数を格子緩和状態において有する半導体材料の、歪を有する平坦化層を少なくとも1つ含んで構成されることを特徴とする、前記のタイプのヘテロ構造によって達成される。

(もっと読む)

半導体オンインシュレータ構造体を製造する方法

本発明は、エレクトロニクスまたはオプトエレクトロニクス用の構造体を処理するプロセスに関し、この構造体は、連続的に、・基板と、・半導体材料の酸化物で作製された酸化物層の熱伝導率よりも実質的に高い熱伝導率を有する誘電体層と、・前記半導体材料の酸化物で作製された酸化物層と、・前記半導体材料で作製された薄い半導体層とを含み、このプロセスは、酸化物層の厚さが所定の値だけ縮小するように、半導体層を通して酸化物層のある量の酸素を拡散させるように選ばれた温度値および持続期間による不活性または還元雰囲気中での構造体の熱処理を含むことを特徴とする。本発明は、さらに、前記熱処理を含むエレクトロニクスまたはオプトエレクトロニクス用の構造体を製造するプロセスに関する。  (もっと読む)

(もっと読む)

半導体ヘテロ構造を作製する方法

【課題】接合の前に最上層を有するドナー・ウェーハ基板上への熱負荷を軽減すること、および、にも拘らず接合の良好な結果を達成すること。

【解決手段】ドナー・ウェーハを作製するために、第1の面内格子定数を持つ第1の基板と、該第1の基板上に、上部が格子緩和状態で第2の面内格子定数を有する空間的に組成傾斜した緩衝層とを準備し、該組成傾斜した緩衝層上に、格子緩和状態で第3の面内格子定数を有する半導体材料の組成非傾斜層を形成し、該組成非傾斜層上に半導体材料の最上層を形成する。また、持ち運び用ウェーハを作製するために、第2の基板を準備し、該第2の基板上に絶縁層を形成し、ドナー・ウェーハを持ち運び用ウェーハに接合する。

(もっと読む)

表面を改善する方法

【課題】本発明は、少なくとも部分的にシリコンを含む、半導体基板の表面を改善する方法に関する。本発明の目的は、少なくとも部分的にシリコンからなる半導体基板の表面を改善する方法であって、高い表面品質を有する半導体基板が提供されるよう、半導体基板の内部または表面にある欠陥を完全に修復することができる方法を提供することである。

【解決手段】この目的は、前記半導体基板の表面にある少なくとも1つのホール内での選択的エピタキシャル堆積を含んだ堆積ステップを含む、上述のタイプの方法によって解決される。

(もっと読む)

Si基板およびSiGe基板用のクロムを含まないエッチング液、そのエッチング液を使用して欠陥を明らかにする方法、およびそのエッチング液を使用してSi基板およびSiGe基板を処理するプロセス

【課題】 Si基板およびSiGe基板用のクロムを含まないエッチング液、このエッチング液を使用して欠陥を明らかにする方法、およびこのエッチング液を使用してSi基板およびSiGe基板を処理するプロセスを提供する。

【解決手段】 本発明は、本明細書で開示されたようなエッチング液を用いて半導体表面を処理する方法だけでなく、シリコンゲルマニウム表面を含んだ半導体表面の欠陥を特徴付けるのに適した新規なエッチング液に関する。この新規なエッチング液は、クロムを含まず、きわめて十分なエッチング速度およびきわめて満足のいくエッチング結果を可能にする。

(もっと読む)

三塩化ガリウムの噴射方式

本発明は、半導体処理装置および方法に関し、特に、光学および電子構成部品の製造、エピタキシャル堆積用の基板としての使用、ウェハ用などの用途に適したIII−V族化合物半導体材料の持続的大量生産を提供する。好ましい実施形態では、これらの方法が、III族−N(窒素)化合物半導体ウェハ、特にGaNウェハを生産するように最適化される。具体的には、この方法は、反応室内で、1つの反応物としてのある量の気体III族前駆体を、他の反応物としてのある量の気体V族成分と、1つまたは複数の基板上での半導体材料の持続的大量製造を提供するのに十分な条件下で反応させることを含み、気体III族前駆体は、III族元素として50g/時の質量流量で、少なくとも48時間の間、連続的に供給される。この方法を実行するシステムも提供される。  (もっと読む)

(もっと読む)

III−V族半導体材料の大量製造装置

本発明は、III族−N(窒素)化合物半導体ウェハ、特にGaNウェハを生産するように最適化された方法および装置に関する。具体的には本発明の方法は、化学蒸着(CVD)リアクタ内の分離弁フィクスチャ(isolation valve fixture)の表面への不必要な材料の形成を実質的に防ぐことに関する。本発明は、反応室内で、1つの反応物としてのある量の気体III族前駆体を、他の反応物としてのある量の気体V族成分と反応させることによって単結晶III−V族半導体材料を形成するシステムおよび方法において使用される分離弁の表面へのGaCl3および反応副生物の堆積/凝縮を制限する装置および方法を提供する。  (もっと読む)

(もっと読む)

71 - 80 / 93

[ Back to top ]