ソイテックにより出願された特許

11 - 20 / 93

III/V族半導体材料を形成する方法及びそのような方法を用いて形成された半導体構造体

【課題】内部の欠陥数がより少なく且つ/又は減少したIII/V族半導体材料を形成する方法、並びに欠陥数がより少なく且つ/又は減少したそのようなIII/V族半導体材料を含む半導体構造体及び素子が必要である。

【解決手段】三元III族窒化物材料を形成する方法は、チャンバー内で基板上に三元III族窒化物材料をエピタキシャル成長させるステップを含む。エピタキシャル成長は、チャンバー中の窒素前駆体の分圧と1つ又は複数のIII族前駆体の分圧との比較的に高い比を含む前駆体ガス混合物をチャンバー内に準備するステップを含む。少なくとも一部は比較的に高い比のため、三元III族窒化物材料の層は、小さいVピット欠陥をその中に含む高い最終厚さに成長させることができる。そのような三元III族窒化物材料の層を含む半導体構造体をそのような方法を用いて作製する。

(もっと読む)

三塩化ガリウムを製造するための大容量送達システム

【課題】本発明は、半導体処理装置および方法の分野に関し、特に、エピタキシャル堆積用の基板としてウェハーなどに使用される、光学および電子部品の製作に適切な、第III−V族化合物半導体材料の持続的大量生産のための方法および装置を提供する。

【解決手段】これらの方法および装置は、第III族−N(窒素)化合物半導体ウェハーを製造するために、特にGaNウェハーを製造するために最適化される。特に前駆体は、半導体材料の大量生産が促進されるよう、少なくとも48時間にわたり、第III族元素が少なくとも50g/時の質量流で提供される。気状第III族前駆体の質量流は、所望の量が送達されるように制御することが有利である。

(もっと読む)

埋め込みドープ層を有する完全空乏型SOIデバイス

【課題】完全空乏型SOIデバイスの製造に適したセミコンダクタオンインシュレータ(SeOI)ウェーハおよびそれを用いたデバイスを提供すること。

【解決手段】本発明は、第1の基板の表面領域にドープ層、ドープ層上に埋め込み酸化物層、埋め込み酸化物層上に半導体層を形成してSeOIウェーハを得る。SeOIウェーハの第2の領域の埋め込み酸化物層および半導体層を維持しながらSeOIウェーハの第1の領域から埋め込み酸化物層および半導体層を除去し、第2の領域に上部トランジスタを形成する。第1の領域にリセスチャネルアレイトランジスタを形成し、第2の領域にpチャネルトランジスタおよび/またはnチャネルトランジスタを形成する。ドープ層内またはこの近傍にバックゲートを形成し、第1の領域にリセスチャネルアレイトランジスタを形成し、ドープ層内またはその近傍にソース領域およびドレイン領域を形成する。

(もっと読む)

半導体構造同士を直接結合する方法、およびこの方法を使用して形成された結合された半導体構造

【課題】半導体構造同士を直接結合する方法を提供すること。

【解決手段】本発明の実施形態は、半導体構造同士を直接結合する方法を含む。いくつかの実施形態では、半導体構造の直接結合された金属フィーチャ間の境界面に、キャップ層を提供することができる。いくつかの実施形態では、半導体構造の直接結合された金属フィーチャ内に、不純物が提供される。そのような方法を使用して、結合された半導体構造が形成される。

(もっと読む)

表面を改善する方法

【課題】本発明は、少なくとも部分的にシリコンを含む、半導体基板の表面を改善する方法に関する。本発明の目的は、少なくとも部分的にシリコンからなる半導体基板の表面を改善する方法であって、高い表面品質を有する半導体基板が提供されるよう、半導体基板の内部または表面にある欠陥を完全に修復することができる方法を提供することである。

【解決手段】この目的は、前記半導体基板の表面にある少なくとも1つのホール内での選択的エピタキシャル堆積を含んだ堆積ステップを含む、上述のタイプの方法によって解決される。

(もっと読む)

三塩化ガリウムを製造するための大容量送達方法

【課題】本発明は、半導体処理装置および方法の分野に関し、特に、エピタキシャル堆積用の基板としてウェハーなどに使用される、光学および電子部品の製作に適切な、第III−V族化合物半導体材料の持続的大量生産のための方法および装置を提供する。

【解決手段】これらの方法および装置は、第III族−N(窒素)化合物半導体ウェハーを製造するために、特にGaNウェハーを製造するために最適化される。特に前駆体は、半導体材料の大量生産が促進されるよう、少なくとも48時間にわたり、第III族元素が少なくとも50g/時の質量流で提供される。気状第III族前駆体の質量流は、所望の量が送達されるように制御することが有利である。

(もっと読む)

接続構造体を実現するためのプロセス

【課題】半導体基板(1000)において接続構造体(2200)を実現するためのプロセス、および、そのように実現された半導体基板を提供すること。

【解決手段】半導体基板(1000)は、第1の表面に沿って第2の基板(1700)と3D集積される。本発明のプロセスは、導電層から半導体基板の残部の中への素子の拡散を防止するための拡散バリア構造体(2211)を成長させる。第1の端面が、拡散バリア構造体(2211)の、第1の表面に対して平行であり、第1の表面に対して垂直な方向に沿いかつ基板から第1の表面の方に延びる拡散バリア構造体(2211)の最も外側の表面であり、横方向のミスアライメントの方向の長さを有する。3D集積された構造体において、第2の基板(1700)の導電層からの素子の拡散を集積された状態で防止するように拡散バリア構造体(2211)の長さが選択される。

(もっと読む)

半径方向位置ずれの補償を含む分子接合による貼り合わせ方法

【課題】分子接合によってそれらの間に初期半径方向位置ずれを有する第1のウェーハを第2のウェーハに貼り合せる方法。

【解決手段】第1のウェーハ100及び第2のウェーハ200間に接合波(Bonding wave)の伝播を起こさせるために、第1のウェーハ100及び第2のウェーハ0200を接触させる少なくとも1つのステップを含む。接触させるステップ中に、予め定められた貼り合せ曲率(KB)が、初期半径方向位置ずれの関数として第1のウェーハ100及び第2のウェーハ200の少なくとも1枚に課される。

(もっと読む)

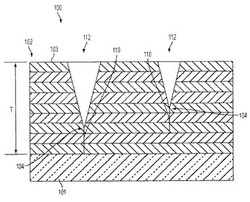

多層ウェーハ中のトレンチ構造

【課題】バーズビーク効果を軽減することのできる、SOIウェーハ内にトレンチを製造する方法を提供すること。

【解決手段】本発明は、基板と、基板上の酸化物層と、酸化物層上の半導体層とを備える多層ウェーハ内にトレンチ構造を製造する方法に関し、本方法は、半導体層および酸化物層を貫通して基板中へ延在するトレンチを形成するステップと、トレンチの内部表面において、半導体層のいくらかの材料が、トレンチの内部表面に露出した酸化物層の部分の一部の上に少なくとも流れるように、形成されたトレンチのアニール処理を行うステップとを含む。

(もっと読む)

SRAMメモリセル

【課題】現存のデバイスの欠点を取り除き、さらにSRAM型メモリセルの体積を減少させる。

【解決手段】SRAM型メモリセルであって、絶縁層によってベース基板から隔離された半導体材料の薄膜を含む絶縁基板上の半導体と、2個のアクセストランジスタT1,T4と、2個の伝導トランジスタT2,T5と、2個の充電トランジスタT3,T6とを含み、メモリセルは、トランジスタT1−T6のそれぞれが、チャネルの下方でベース基板内に形成されたバックコントロールゲートBG1,BG2を有し、トランジスタの敷居電圧を調整するようにバイアスをかけられ、第1のバックゲートラインはアクセストランジスタT1,T4に接続し、第2のバックゲートラインは伝導トランジスタT2,T5および充電トランジスタT3,T6に接続し、各々の電位はセル制御動作の型に応じて調整される。

(もっと読む)

11 - 20 / 93

[ Back to top ]