エイアールエム リミテッドにより出願された特許

11 - 20 / 85

演算およびスリープ・モード中のデータ格納回路並びに方法

【課題】スリープ・モード中に信号を格納するための回路を提供する。

【解決手段】スリープ信号を受け取るスリープ信号入力と、クロック信号を受け取るクロック信号入力と、クロック信号でクロックされる複数のラッチと、クロック信号でクロックされるトライステート素子であって、トライステート素子は1つの入力に、少なくとも1つの格納ラッチが接続され、格納ラッチは複数のラッチの1つであり、トライステート素子は格納ラッチの入力を、予め定められたクロック信号値に応答して選択的に分離するトライステート素子とを含み、回路への電源供給が、スリープ信号に応答して、回路の少なくとも1部の電圧差が低減されて回路の部分の電源が遮断され、格納ラッチに掛かる電圧差が維持され、トライステート素子で受け取られるクロック信号が予め定められた値に保持されて、格納ラッチの入力が分離される。

(もっと読む)

タイルベースのグラフィックスシステム及びこのようなシステムの動作方法

【課題】複数のタイルを含むグラフィックスデータ生成のための、タイルベースのグラフィックスシステムと、その動作方法、及びグラフィックス処理回路が提供される。

【解決手段】処理回路は、第1及び第2動作モード間で切換えられる。第1モードで処理回路は、フレーム用のグラフィックスプリミティブを受け取り、ビニング動作を行う。これにより複数のタイルそれぞれについて、グラフィックスプリミティブのうちタイルと交差するものを特定するリストを決定する。第2モードで処理回路は、割り当てられたタイルのタイルリストを受信し、ラスタライゼーション動作を行う。この動作ではタイルリストに応じて、割り当てられたタイルについてグラフィックスデータを生成する。その結果、ビニング動作およびラスタライゼーション動作で同じ処理単位を使用でき、性能およびエネルギー消費を向上でき、グラフィックスシステムのサイズも大幅に低減する。

(もっと読む)

命令の追跡中に作られるデータ・ストリームの大きさの削減

【課題】データ処理装置が高速になるに従って命令の実行の追跡が複雑になることに対処して、追跡中に作られるデータ・ストリームの大きさを削減する方法を開示する。

【解決手段】追跡論理(40)は命令ストリーム内の命令の処理を検出する監視論理(42)を含み、命令ストリーム内の命令のどれが条件付き直接分岐命令か、条件付き間接分岐命令か、無条件間接分岐命令かを検出する。追跡論理(40)は更に圧縮論理(50)を含み、前記条件付き直接分岐命令、条件付き間接分岐命令、または間接分岐命令をマーカ命令に指定し、マーカ命令毎に、マーカ命令を実行したことを示す実行標識またはマーカ命令を実行しなかったことを示す不実行標識は出力し、処理したがマーカ命令でない命令に関するデータは出力しない。

(もっと読む)

データ処理命令を実行するためのデータ処理装置および方法

【課題】本発明はリターンステートをセーブするためのデータ処理装置および方法を提供する。

【解決手段】このデータ処理装置はデータ処理命令を実行するための処理ユニットを備え、この処理ユニットは複数の作動モードを有し、各作動モードはそのモードに関連したデータを記憶するための対応するスタックを有する。処理ユニットは現在の作動モードからの処理ユニットのリターンステートデータを現在の作動モードと異なる作動モードに対応するスタックに書き込むよう、リターンステートデータ処理命令に応答自在である。このアプローチは公知の従来技術よりもコードサイズを大幅に縮小し、割り込みレイテンシーを改善する。

(もっと読む)

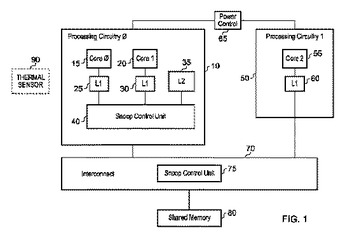

第1の処理回路と第2の処理回路との間で作業負荷を切り替えるためのデータ処理装置および方法

2つの処理回路の間で作業負荷の実施を切り替えるためのデータ処理装置および方法を提供する。データ処理装置は、第2の処理回路とアーキテクチャ上の互換性がある、第1の処理回路を有するが、第1の処理回路は、マイクロアーキテクチャ上で第2の処理回路とは異なる。任意の時点で、少なくとも1つのアプリケーションとそのアプリケーションを実行するための少なくとも1つのオペレーティングシステムとからなる作業負荷が、第1の処理回路および第2の処理回路のうちの1つによって実施される。スイッチコントローラは、移転刺激に応答して、移転元処理回路から移転先処理回路へ作業負荷の実施を移転するようにハンドオーバー動作を実施し、移転元処理回路は、第1の処理回路および第2の処理回路のうちの一方であり、移転先処理回路は、第1の処理回路および第2の処理回路のうちのもう一方である。ハンドオーバー動作中、スイッチコントローラは、移転元処理回路に、その最新アーキテクチャ状態を移転先処理回路に利用可能にさせ、この最新アーキテクチャ状態は、ハンドオーバー動作が開始された時に共有メモリからは利用できない状態であり、移転先処理回路が、移転元処理回路から作業負荷の実施を成功裏に引き継ぐために必要である。加えて、スイッチコントローラは、作業負荷の移転がそのオペレーティングシステムに透過的であるように、少なくとも1つのオペレーティングシステムから既定のプロセッサ固有の構成情報をマスクする。かかる手法は、処理回路間でアプリケーションを切り替える能力を備えるオペレーティングシステムを提供することに関連する複雑性を回避しながら、顕著なエネルギー消費利点を生み出すことが見出された。  (もっと読む)

(もっと読む)

移転元処理回路と移転先処理回路との間で作業負荷を移転するためのデータ処理装置および方法

移転刺激に応答して、移転に続いて移転元処理回路が電力節約状態に入れられる準備として、処理作業負荷の実施が移転元処理回路から移転先処理回路へ移転される。移転に続いて移転先処理回路によって必要となる、メモリ取得回数を削減するために、移転元処理回路のキャッシュは、スヌープ期間中、駆動状態に維持される。スヌープ期間中、キャッシュスヌープ回路は、移転元キャッシュのデータ値をスヌープし、移転先処理回路のためにスヌープデータ値を呼び出す。  (もっと読む)

(もっと読む)

インターコネクト内の低減されたレイテンシのバリアトランザクション要求

データ処理装置のためのインターコネクト回路機構が開示される。このインターコネクト回路機構は、少なくとも1つのイニシエータデバイスが、少なくとも1つの受信デバイスにアクセスする際に経由することができる、データルートを提供するように構成され、このインターコネクト回路機構は、少なくとも1つのイニシエータデバイスからトランザクション要求を受信するための、少なくとも1つの入力と、少なくとも1つの受信デバイスにトランザクション要求を出力するための、少なくとも1つの出力と、少なくとも1つの入力と少なくとも1つの出力との間でトランザクション要求を送信するための、少なくとも1つの経路と、受信されたトランザクション要求を、少なくとも1つの入力から少なくとも1つの出力へルーティングするための制御回路機構とを含み、この制御回路機構が、バリアトランザクション要求に応答して、少なくとも1つの経路のうちの1つに沿って通過するトランザクション要求のストリーム内部のバリアトランザクション要求に対しての、少なくとも一部のトランザクション要求の順序付けを、トランザクション要求のストリーム内のバリアトランザクション要求の後に発生する少なくとも一部のトランザクション要求に対しての、トランザクション要求のストリーム内のバリアトランザクション要求の前に発生する少なくとも一部のトランザクション要求の順序変更を許可しないことによって、維持するように構成され、この制御回路機構が、応答信号生成器を含み、この応答信号生成器は、バリアトランザクション要求の受信に応答して、応答信号を発行し、この応答信号は、バリアトランザクション要求に応答して遅延されたいずれかのトランザクション要求が更に先へ送信され得ることを、上流のブロッキング回路機構に指示する。  (もっと読む)

(もっと読む)

インターコネクト内のバリアトランザクション

データ処理装置のためのインターコネクト回路機構が開示される。このインターコネクト回路機構は、少なくとも1つのイニシエータデバイスが、少なくとも1つの受信デバイスにアクセスする際に経由することができる、データルートを提供するように構成され、このインターコネクト回路機構は、少なくとも1つのイニシエータデバイスからトランザクション要求を受信するための、少なくとも1つの入力と、少なくとも1つの受信デバイスにトランザクション要求を出力するための、少なくとも1つの出力と、少なくとも1つの入力と少なくとも1つの出力との間でトランザクション要求を送信するための、少なくとも1つの経路と、受信されたトランザクション要求を、少なくとも1つの入力から少なくとも1つの出力へルーティングするための制御回路機構とを含み、この制御回路機構が、バリアトランザクション要求に応答して、少なくとも1つの経路のうちの1つに沿って通過するトランザクション要求のストリーム内部のバリアトランザクション要求に対しての、少なくとも一部のトランザクション要求の順序付けを、トランザクション要求のストリーム内のバリアトランザクション要求の後に発生する少なくとも一部のトランザクション要求に対しての、トランザクション要求のストリーム内のバリアトランザクション要求の前に発生する少なくとも一部のトランザクション要求の順序変更を許可しないことによって、維持するように構成され、このバリアトランザクション要求は、トランザクション要求のストリーム内部のトランザクション要求のうちのいずれが、順序付けが維持されるべき少なくとも一部のトランザクション要求を含むかを指示する、指示子を含む。  (もっと読む)

(もっと読む)

データ処理システムにおける処理動作マスキング

【課題】セキュリティ攻撃に対して抵抗力を持つデータ処理システムを提供する。

【解決手段】条件付き書き込み処理操作をサポートするデータ処理システムの中にトラッシュレジスタが設けられていて、非書き込み条件に遭遇したとき、レジスタ書き込みが条件付き書き込み操作により特定されるデータレジスタでなくてトラッシュレジスタになされる。したがって、レジスタ書き込みが起きるか否かに関係する電力変動が外部から観察できなくなる。トラッシュレジスタはシステム・コンフィギュレーション・レジスタ内に記憶されているコンフィギュレーション・パラメータによって、イネーブルとディスエーブルにプログラム可能である。

(もっと読む)

データ処理システムに於けるメモリ制御

【課題】データ処理システムに於ける効率的なメモリシステムの管理並びに制御を実現する。

【解決手段】メモリアクセス要求が発生してキャッシュミスが生じた場合に、キャッシュを入れ替えるために取り除くべきキャッシュ(ビクティムキャッシュ)を選ぶ必要がある。その際、特定の機器で占有されていないキャッシュか否か、キャッシュ存在中に書き換えられたために主メモリに書き戻す必要があるか否か、書き戻し先の主メモリがビジーであるか否かを判定して最も処理に要する時間が短くかつ最近最も使用されていないキャッシュの中から、ビクティムキャッシュを選んで効率化を図る。

(もっと読む)

11 - 20 / 85

[ Back to top ]